TSMC создала для Alphawave опытный образец чипа на улучшенном 3-нм техпроцессе

Компания Alphawave сообщила о выпуске первого в мире опытного образца чипа с использованием улучшенного 3-нм технологического процесса N3E от компании TSMC. Разработчики отметили, что тестовый образец успешно прошёл все тесты.

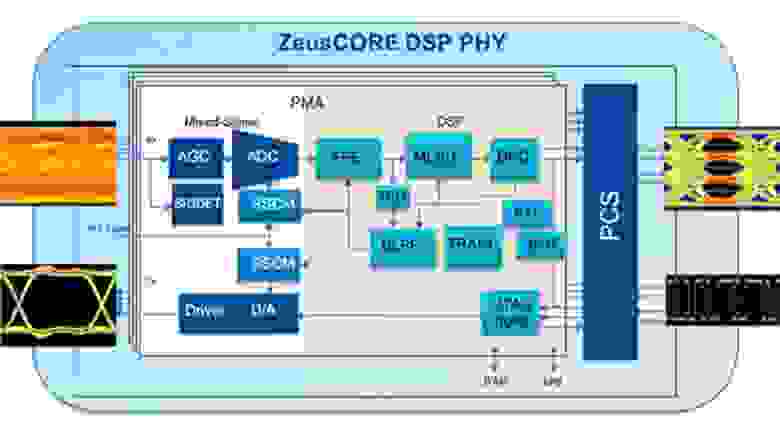

Образец чипа ZeusCORE100 1–112Gbps NRZ/PAM4 Serialiser-Deserialiser (SerDes) представляет собой два функциональных блока, используемых в высокоскоростной связи, для преобразования данных между последовательным и параллельным интерфейсами в обоих направлениях. Он поддерживает новые стандарты интерфейсов, в том числе 800G Ethernet, OIF 112G-CEI, PCIe 6.0 и CXL3.0. Эти чипы используют чаще всего для коммуникаций в серверах.

TSMC собирается сделать пять вариаций 3-нм технологического процесса в течение нескольких ближайших лет. Стандартная версия 3-нм (N3) техпроцесса будет доступна ведущим клиентам контрактного производителя чипов, например, Apple.

Чипы на базе усовершенствованного 3-нм техпроцесса (N3E) получат широкое использование в сравнении с чипами на базе N3. По утверждениям разработчиков, старт массового выпуска чипов на основе N3E будет не раньше середины 2023 года. После этого компания TSMC планирует перейти к выпуску микросхем на техпроцессах N3P и N3S. Эти техпроцессы представляют собой варианты оптимизации N3E под различные применения. N3P создан с упором на высокопроизводительные чипы. N3S создан с упором на энергоэффективные чипы с повышенной плотностью транзисторов. Однако эти техпроцессы запланированы на 2024 год.

В 2025 году компания собирается освоить ещё одну технологию 3-нм техпроцесса — N3X. На базе N3X будут выпускать высокопроизводительные процессоры, где важно использование высоких токов и долгая работа на повышенных тактовых частотах.