Микроконтроллеры Megawin серии MG32F02: таймеры общего назначения

Продолжая цикл публикаций по микроконтроллерам на ядре Cortex-M0 компании Megawin (см. предыдущие статьи 1, 2, 3, 4 и 5), сегодня рассмотрим таймеры общего назначения.

Функциональные возможности таймеров МК серии MG32F02

МК MG32F02×064, MG32F02×128 включают 7 таймеров общего назначения четырех типов TM00/01, TM10/16, TM20/26 и TM36. МК MG32F02A032 включает 5 таймеров трех типов TM00/01, TM10/16, и TM36. Таймеры имеют общий базовый принцип построения, но различаются функциональными возможностями, которые возрастают с увеличением первой цифры в названии.

Таймеры имеют следующие общие функциональные возможности:

основной счетчик (CT1) и предделитель (CT2) с одинаковой разрядностью (8 или 16);

три режима работы предделителя и счетчика: раздельный, каскадный, совмещенный (общая разрядность 16 или 32);

направление счета предделителя вверх или вниз;

выбор источника сигнала внутреннего тактирования модуля с делением частоты на 1, 2, 4 или 8;

выбор внешнего (с вывода МК) или внутреннего сигнала тактирования отдельно для CT1 и CT2;

выбор внешнего или одного из 8 внутренних сигналов (событий) МК в качестве входного триггерного сигнала;

выбор события для генерации выходного триггерного сигнала для других модулей МК;

коммутация выходного триггерного сигнала на внешний вывод МК;

коммутация сигнала переполнения от CT1 или CT2 на внешний вывод МК;

режим «автостоп»;

генерация прерывания по выбранному событию в модуле;

работа в режимах ON и SLEEP.

Различия в функциональных возможностях таймеров приведены в таблице.

Функция | TM00/01 | TM10/16 | TM20/26 | TM36 |

|---|---|---|---|---|

Разрядность основного счетчика | 8 | 16 | 16 | 16 |

Разрядность предделителя | 8 | 16 | 16 | 16 |

Независимые каналы | - | - | 2 | 4 |

Входы захвата (IC) | - | - | 2 | 4 |

Входной сигнал отключения выходов (Input Break) | - | - | - | + |

Выходы схемы сравнения (OC) | - | - | 2 | 4 |

Комплементарные выходы схемы сравнения (OCN) | - | - | 2 | 3 |

Выходы схемы сравнения для раздельного 8-битного режима (OCH) | - | - | 2 | 4 |

Режим ШИМ | - | - | + | + |

Режим ШИМ с выравниванием по центру | - | - | - | + |

Формированием «мертвого» времени | - | - | - | + |

Направление счета вверх основного счетчика | + | + | + | + |

Направление счета вниз основного счетчика | - | TM16 | TM26 | + |

Дополнительный счетчик для режима «автостоп» | - | - | + | + |

Интерфейс квадратурного энкодера | - | - | TM26 | + |

Сигнал XOR из 3-х сигналов IC в качестве сигнала захвата канала 0 | - | - | - | + |

Задержка выходного сигнала | - | - | + | + |

Поддержка DMA | - | - | - | + |

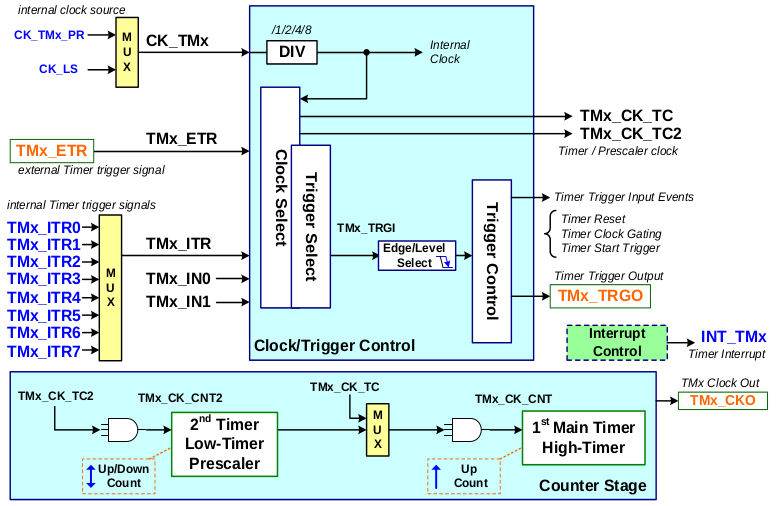

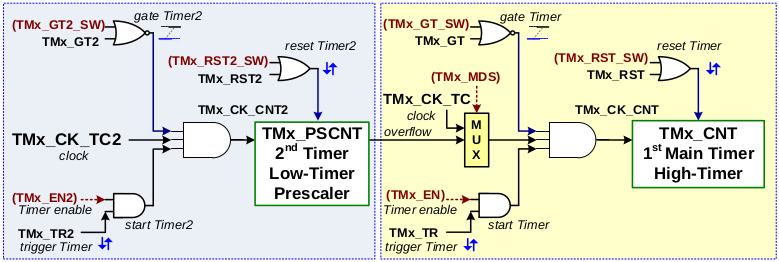

Функциональная схема включает общую для всех таймеров часть, приведенную на следующем рисунке, и часть дополнительных функций, которая далее будет рассматриваться отдельно для каждого типа таймера.

Общая часть функциональной схемы таймеров

Общая часть функциональной схемы таймеров

Общая часть включает:

блок формирования внутреннего сигнала тактирования, сигналов тактирования счетчиков TMx_CK_TC и TMx_CK_TC2 (Clock Control);

блок формирования входного триггерного и выходного триггерного сигналов (Trigger Control);

блок счетчиков (Counter Stage), состоящий из основного счетчика Main Timer (далее — CT1) и предделителя 2nd Timer (Prescaler) (далее — CT2) с одинаковой разрядностью;

блок формирования сигнала прерывания модуля INT_TMx (Interrupt Control).

Тактирование

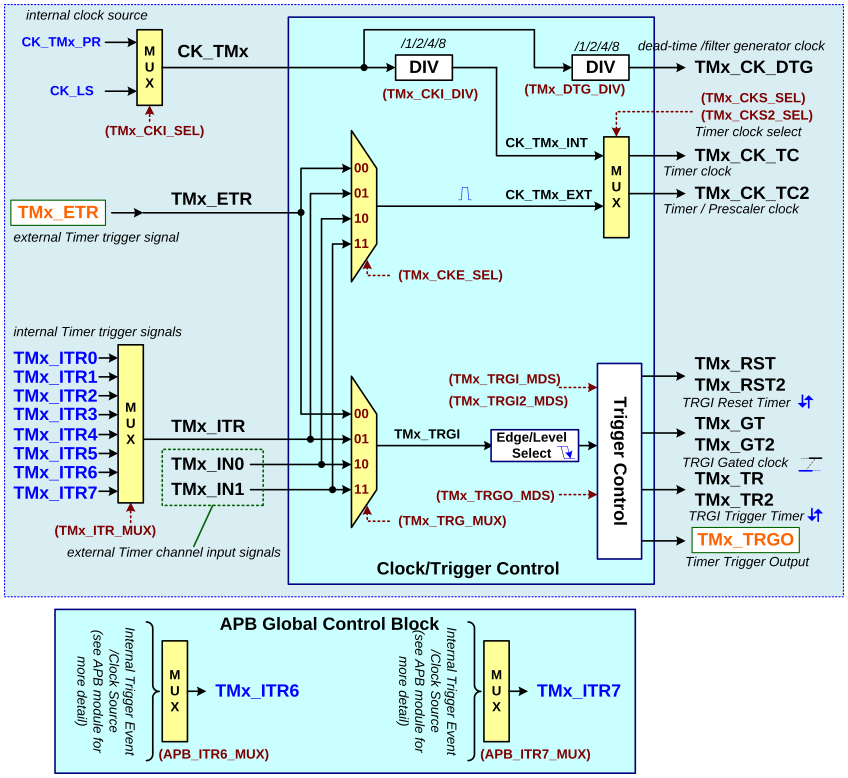

На следующем рисунке представлена более подробная схема блоков Counter Stage и Trigger Control.

Схема тактирования и формирования триггерных сигналов

Схема тактирования и формирования триггерных сигналов

Источник внутреннего тактового сигнала модуля CK_TMx определяется значением поля TMx_CLK.TMx_CKI_SEL:

0 — сигнал CK_TMx_PR из подсистемы тактирования МК, который, в свою очередь, определяется битом

CSC_CKS2.CSC_TMx_CKSиз сигналов CK_APB (0) или CK_AHB (1);2 — общесистемный НЧ-сигнал CK_LS, частота которого должна быть не выше половины частоты сигнала CK_TMx_PR.

Сигнал CK_TMx подается на делитель частоты с коэффициентом 1, 2, 4 или 8 (выбирается в поле TMx_CLK.TMx_CKI_DIV), на выходе которого формируется внутренний тактовый сигнал CK_TMx_INT. Альтернативный тактовый сигнал CK_TMx_EXT в зависимости от значения поля TMx_CLK.TMx_CKE_SEL формируется из одного из сигналов:

0 — внешний сигнал TMx_ETR с вывода МК,

1 — сигнал TMx_ITR с выхода мультиплексора выбора одного из доступных триггерных сигналов для данного таймера ITR_MUX (см. описание далее),

2 и 3 — дополнительные входные сигналы таймера TMx_IN0 и TMx_IN1 (только для таймеров TM20/26 и TM36).

Итоговый сигнал счетных импульсов TMx_CK_TC основного счетчика CT1 выбирается битом TMx_CLK.TMx_CKS_SEL из сигналов: CK_TMx_INT (0) или CK_TMx_EXT (1). Аналогично выбирается сигнал счетных импульсов TMx_CK_TC2 счетчика CT2 по значению бита TMx_CLK.TMx_CKS2_SEL.

В таймере TM36 сигнал CK_TMx также подается на другой делитель частоты с коэффициентом 1, 2, 4 или 8 (выбирается в поле TM36_CLK.TM36_DTG_DIV), на выходе которого сигнал TMx_CK_DTG используется для формирования «мертвого» времени в режиме ШИМ.

Режимы работы счетчиков

Выбор режима

В каждом таймере счетчики CT1 и CT2 могут быть настроены на работу в одном из трех режимов:

раздельном (Separate Mode) — каждый счетчик тактируется и работает независимо от другого;

каскадном (Cascade Mode) — счетчик CT2 выполняет функцию предделителя для основного счетчика CT1 (по-умолчанию);

совмещенном (Full-Counter Mode) — оба счетчика объединяются в единый счетчик с общей разрядностью 16 или 32.

Режим работы счетчиков задается в поле TMx_CR0.TMx_MDS. При использовании счетчика CT1 он должен быть включен установкой бита TMx_CR0.TMx_EN. При использовании счетчика CT2 в первых двух режимах необходимо установить бит TMx_CR0.TMx_EN2; в совмещенном режиме CT2 включается автоматически вместе с CT1 установкой бита TMx_CR0.TMx_EN.

Раздельный режим (Separate)

В раздельном режиме счетчики включаются и функционируют независимо друг от друга. Счетчик CT1 переключается под действием импульсов сигнала TMx_CK_TC. В таймерах TM00/01, TM10 и TM20 возможен счет только вверх, в остальных таймерах — в обе стороны, направление счета задается битом TMx_CR0.TMx_DIR. Текущее значение счетчика доступно по чтению и записи в регистре TMx_CNT (разряды 0–7 или 0–15 в зависимости от типа таймера). В регистре TMx_ARR (Auto-Reload Register) задается значение автозагрузки счетчика (разряды 0–7 или 0–15). При счете вверх при превышении этого значения генерируется событие Timer Overflow и устанавливается флаг TOF, а счетчик сбрасывается в 0. При счете вниз из нулевого состояния генерируется событие Timer Underflow и устанавливается флаг TUF, а в счетчик загружается значение TMx_ARR. По-умолчанию значение автозагрузки равно 0. Частота полного цикла счета будет определяться выражением

F1 = F (CK_TC) / (ARR + 1) ,

где F (CK_TC) — частота входных счетных импульсов счетчика CT1, ARR — значение регистра TMx_ARR.

Счетчик CT2 переключается под действием импульсов сигнала TMx_CK_TC2. Направление счета задается битом TMx_CR0.TMx_DIR2 для всех таймеров. Текущее значение счетчика доступно по чтению и записи в поле TMx_PSCNT регистра TMx_PSCNT (разряды 0–7 или 0–15). В этом же регистре в поле TMx_CNTA продублировано текущее значение счетчика CT1 (разряды 8–15 или 16–31 в зависимости от типа таймера), поле доступно только по чтению. В регистре TMx_PSARR (Prescaler Auto-Reload Register) задается значение автозагрузки счетчика CT2 (разряды 0–7 или 0–15), которое используется аналогично основному счетчику. При счете вверх при превышении этого значения генерируется событие Timer Overflow и устанавливается флаг TOF2, а счетчик сбрасывается в 0. При счете вниз из нулевого состояния генерируется событие Timer Underflow и устанавливается флаг TUF2, а в счетчик загружается значение TMx_PSARR. Частота полного цикла счета будет определяться выражением

F2 = F (CK_TC2) / (PSARR + 1) ,

где F (CK_TC2) — частота входных счетных импульсов счетчика CT2, PSARR — значение регистра TMx_PSARR.

Каскадный режим (Cascade)

В каскадном режиме счетчик CT2 выполняет функцию предделителя для основного счетчика CT1. Счетчик CT2 переключается под действием импульсов сигнала TMx_CK_TC2, а счетчик CT1 — по завершению каждого цикла CT2. В остальном счетчики настраиваются независимо. Частота FC полного цикла счета CT1 будет определяться выражением

FC = F (CK_TC2) / [ (ARR + 1)·(PSARR + 1) ] .

Совмещенный режим (Full-Counter)

В совмещенном режиме оба счетчика объединяются в единый счетчик с общей разрядностью 16 (для таймеров TM00/01) или 32 (для остальных таймеров). Счетчик CT1 представляет старшие разряды (High), а счетчик CT2 — младшие разряды (Low). Единый счетчик переключается под действием импульсов сигнала TMx_CK_TC2. В таймерах TM00/01, TM10 и TM20 возможен счет только вверх, в остальных таймерах — в обе стороны согласно значению бита TMx_CR0.TMx_DIR. Значение автозагрузки счетчика формируется из значений регистра TMx_ARR (старшие 8 или 16 бит) и TMx_PSARR (младшие 8 или 16 бит). При наступлении события Timer Overflow единого счетчика устанавливаются оба флага TOF и TOF2. При наступлении события Timer Underflow устанавливаются оба флага TUF и TUF2. Частота FF полного цикла счета будет определяться выражением

FF = F (CK_TC2) / (2N ·ARR + PSARR + 1) ,

где N — разрядность одного счетчика (8 или 16) в зависимости от типа таймера.

Событие обновления счетчиков

В таймере формируются два внутренних сигнала обновления счетчиков TMx_UEV и TMx_UEV2. Схема их формирования показана на следующем рисунке.

Схема формирования сигналов TMx_UEV и TMx_UEV2

Схема формирования сигналов TMx_UEV и TMx_UEV2

Сигнал TMx_UEV активируется при завершении каждого цикла счетчика CT1. В поле TMx_TRG.TMx_UEV_SEL определяется событие активизации: TOF, TUF или оба (по-умолчанию). В последнем случае можно генерировать событие программно установкой бита TMx_CR0.TMx_USW_EN, а также можно использовать сигнал TMx_TRGI_EX при установке бита TMx_CR0.TMx_UEX_EN. Сигнал TMx_TRGI_EX формируется из сигнала TMx_TRGI (см. описание далее) при установленном бите разрешения TMx_CR0.TMx_EX_EN с опциональным инвертированием при установленном бите TMx_CR0.TMx_EX_INV.

Сигнал TMx_UEV2 активируется при завершении каждого цикла счетчика CT2 по событиям TOF2 и TUF2. Сигналы TMx_UEV и TMx_UEV2 могут быть выбраны источником выходного триггерного сигнала TMx_TRGO, если в поле TMx_TRG.TMx_TRGO_MDS установлено соответствующее значение.

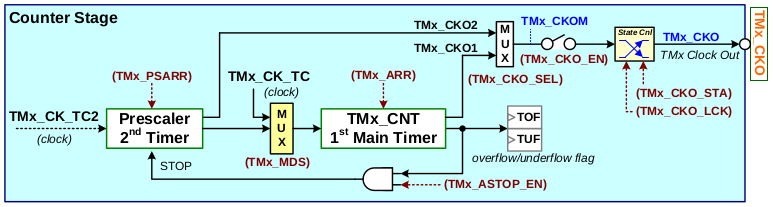

Выходной сигнал таймера CKO и функция автостопа

В каждом таймере имеется возможность коммутации выходного сигнала счетчиков на внешний вывод МК TMx_CKO. Схему иллюстрирует следующий рисунок.

Схема формирования сигнала TMx_CKO

Схема формирования сигнала TMx_CKO

Источником сигнала TMx_CKOM в зависимости от значения поля TMx_CKO.TMx_CKO_SEL может быть:

сигнал TMx_CKO1 с выхода счетчика CT1,

сигнал TMx_CKO2 с выхода счетчика CT2 (по-умолчанию).

Если установлен бит TMx_CKO.TMx_CKO_EN, сигнал TMx_CKOM проходит на выходной узел формирования сигнала TMx_CKO. Выходной сигнал формируется с помощью T-триггера: при каждом импульсе сигнала TMx_CKOM логическое состояние выхода TMx_CKO изменяется на противоположное. Таким образом, на выходе TMx_CKO формируется сигнал, частота которого в 2 раза ниже частоты сигналов TMx_CKO1 или TMx_CKO2. Начальное состояние выхода TMx_CKO определяется битом TMx_CKO.TMx_CKO_STA, изменение значения этого разряда возможно при одновременной записи логической »1» в разряд TMx_CKO_LCK этого же регистра.

В таймере имеется возможность автоматической остановки счетчика CT2 при завершении цикла счетчика CT1. Данная функция включается установкой бита TMx_CR0.TMx_ASTOP_EN. Счетчик CT2 продолжит считать после программного сброса флагов TOF или TUF (в зависимости от направления счета), при этом в совмещенном режиме единый счетчик начнет считать с начального состояния. Если установлен бит TMx_CR0.TMx_ACLEAR_EN, то при срабатывании автостопа также сбрасываются флаги TOF и TUF.

Счетчик повторений

В состав таймеров TM20/26 и TM36 (кроме МК MG32F02A032) входит дополнительный блок, предназначенный для остановки счетчиков после заданного числа циклов счета. Блок основан на 8-разрядном счетчике обратного отсчета Repetition Counter (далее — RCT). В поле TMx_RCNT регистра TMx_RCNT по чтению и записи доступно значение счетчика, а в поле TMx_RARR — значение для его перезагрузки после достижения нуля. Работа счетчика разрешается установкой бита TMx_CR0.TMx_RC_EN. Останов счета основного счетчика CT1 при завершении цикла счета RCT разрешается установкой бита TMx_CR0.TMx_RC_STP. По завершению одного цикла счета RCT активируется флаг RTUF.

Источник тактовых импульсов для RCT выбирается в поле TMx_CLK.TMx_RC_CKS из числа следующих:

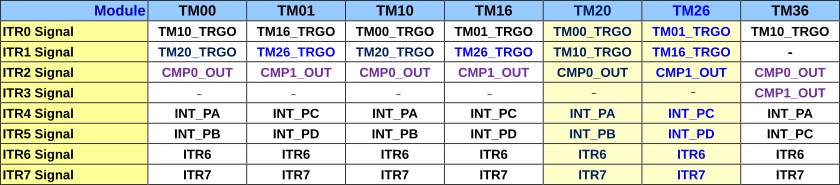

Блок формирования входного триггерного сигнала

Все настройки блока осуществляются через регистр TMx_TRG. Входной триггерный сигнал таймера TMx_TRGI в зависимости от значения поля TMx_TRG_MUX формируется из одного из сигналов TMx_ETR, TMx_ITR, TMx_IN0 или TMx_IN1 (аналогично сигналу CK_TMx_EXT). В поле TMx_ITR_MUX выбирается один из восьми доступных для данного таймера источников сигнала TMx_ITR согласно приведенной ниже таблице.

Источники входного триггерного сигнала TMx_ITR

Источники входного триггерного сигнала TMx_ITR

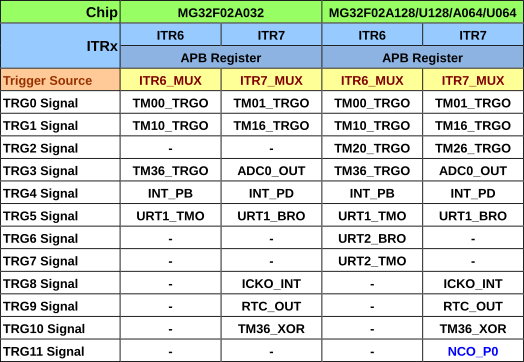

Общесистемные триггерные сигналы ITR6 и ITR7 для всего МК выбираются через поля APB_ITR6_MUX и APB_ITR7_MUX регистра APB_CR2 согласно следующей таблице.

Источники триггерных сигналов ITR6 и ITR7

Источники триггерных сигналов ITR6 и ITR7

Для управления счетчиками используются следующие три сигнала:

Reset (TMx_RST, TMx_RST2) — для сброса счетчика в 0 при возрастающем счете или для перезагрузки значения из регистров

TMx_ARR/TMx_PSARRпри убывающем счете;Gated Clock (TMx_GT, TMx_GT2) — для отключения подачи счетных импульсов на вход счетчиков;

Trigger (TMx_TR, TMx_TR2) — для запуска счетчика по сигналу в соответствии с установленным условием.

Сигнал TMx_TRGI может быть использован для формирования одного из трех управляющих сигналов для каждого счетчика. Формируемый сигнал и активный уровень определяются полями TMx_TRGI_MDS и TMx_TRGI2_MDS для счетчиков CT1 и CT2 соответственно. Схема формирования управляющих сигналов счетчиков приведена на следующем рисунке.

Схема формирования управляющих сигналов счетчиков

Схема формирования управляющих сигналов счетчиков

Счетчики CT1 и CT2 могут быть сброшены программно установкой битов TMx_TRG.TMx_RST_SW и TMx_TRG.TMx_RST2_SW соответственно. Для возобновления счета эти биты должны быть сброшены. Также возможно отключение подачи счетных импульсов на входы счетчиков установкой битов TMx_TRG.TMx_GT_SW и TMx_TRG.TMx_GT2_SW соответственно. В совмещенном режиме сброс единого счетчика осуществляется установкой бита TMx_TRG.TMx_RST_SW, а отключение подачи счетных импульсов на вход — установкой бита TMx_TRG.TMx_GT_SW.

Блок формирования выходного триггерного сигнала

На следующем рисунке показана общая схема формирования выходного (триггерного) сигнала таймера TMx_TRGO. Не все указанные события могут быть доступны в конкретном типе таймера.

Схема формирования выходного триггерного сигнала

Схема формирования выходного триггерного сигнала

Все настройки блока также осуществляются через регистр TMx_TRG. Событие для формирования сигнала TMx_TRGO определяется значением поля TMx_TRGO_MDS. Сигнал TMx_TRGO может быть использован как входной сигнал (управляющий или счетный) для других периферийных модулей МК и может быть выведен на внешний вывод МК (см. таблицу AFS на конкретный тип МК). Сигнал TMx_TRGO может быть проинвертирован, если будет установлен бит TMx_TRGO_INV.

Сигналом TMx_TRGO можно управлять программно путем установки и сброса бита TMx_TRGO_SW, если в качестве источника выбран SW (9). Если в качестве источника выбирается событие UEV, то в поле TMx_UEV_SEL можно задать один из трех вариантов формирования выходного сигнала: по переполнению счетчика CT1, по достижению нуля счетчиком CT1, либо оба события (по-умолчанию). Остальные события будут рассмотрены далее.

Таймеры TM00/01 и TM10/16

Данные таймеры представляют собой базовый вариант с минимальным функционалом, поэтому не включают часть дополнительных функций. Их общая часть соответствует приведенной выше функциональной схеме за исключением того, что сигналы TMx_IN0 и TMx_IN1 не поддерживаются. Таймеры TM00/01 отличаются от TM10/16 только разрядностью счетчиков (8 и 16 соответственно). Таймер TM16 отличается возможностью счета вниз для счетчика CT1.

Таймеры TM20/26

Функциональная схема

Функциональная схема таймеров TM20/26 приведена на следующем рисунке.

Функциональная схема таймеров TM20/26

Функциональная схема таймеров TM20/26

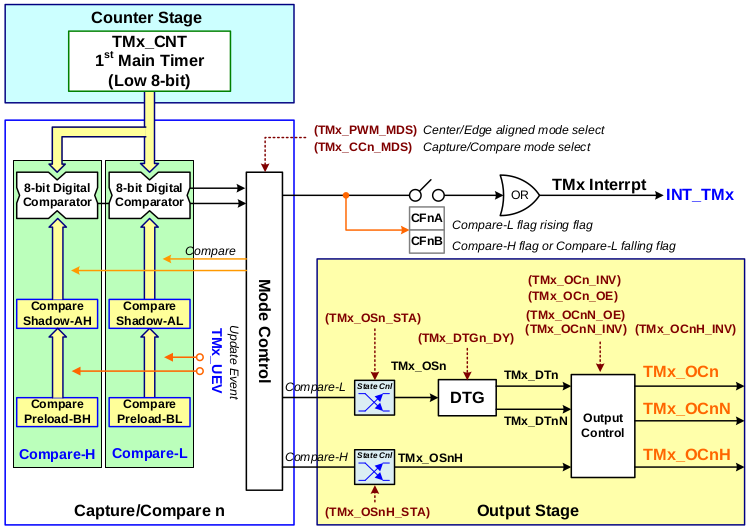

Часть дополнительных функций включает двухканальную схему захвата/сравнения, состоящую из следующих блоков:

блок формирования входных управляющих сигналов для каждого канала таймера (Input Stage),

блок захвата/сравнения (Capture/Compare),

блок формирования выходных сигналов для каждого канала таймера (Output Stage).

В составе каждого блока захвата/сравнения имеются два 16-разрядных регистра CCnA и CCnB, программно доступные по чтению и записи как TMx_CCnA и TMx_CCnB, где n — номер канала 0 или 1. Схема может работать в одном из следующих режимов, задаваемом в поле TMx_CCMDS.TMx_CCn_MDS:

NOP(0) — схема отключена;16bit_IC(1) — захват по входному сигналу,16bit_OC(2) — выход по сравнению в режиме 16 бит,8bitx2_OC(3) — два выхода по сравнению в режиме 8 бит,16bit_PWM(4) — 16-битный формирователь ШИМ-сигнала,8bitx2_PWM(5) — два 8-битных формирователя ШИМ-сигнала.

Рассмотрим каждый из режимов работы подробнее.

Захват по входному сигналу

В этом режиме (16bit_IC) в регистрах CCnA и CCnB сохраняется состояние счетчиков в момент срабатывания входного триггера. Схема захвата для одного канала приведена на следующем рисунке.

Схема захвата

Схема захвата

Каждый канал имеет один вход, на который подается сигнал TMx_ISn, где n — номер канала 0 или 1. Этот сигнал поступает с выхода блока Edge Select, в котором определяется активный фронт входного триггерного сигнала TMx_INn согласно значению поля TMx_ICCR.TMx_ICn_TRGS: 0 — отключен, 1 — нарастающий (передний), 2 — спадающий (задний), 3 — оба фронта. Источник сигнала TMx_INn выбирается в поле TMx_ICCR.TMx_ICn_MUX из следующих:

внешний вывод МК TMx_ICn,

внутренний сигнал таймера TMx_ITR (см. схему блоков Counter Stage и Trigger Control выше),

выход компаратора CMPn_OUT.

Если в поле TMx_ICCR.TMx_ICn_TRGS выбрано срабатывание по одному из фронтов (1 или 2), то в зависимости от режима работы счетчиков схема работает следующим образом:

в раздельном и каскадном режимах в регистре CCnA сохраняется значение счетчика CT1 при первом срабатывании триггера, а в регистре CCnB — значение счетчика CT1 при втором срабатывании триггера;

в совмещенном режиме 32-битное значение единого счетчика сохраняется при каждом срабатывании триггера: старшие 16 бит — в регистре CCnA, младшие 16 бит — в регистре CCnB.

После первого срабатывания триггера и сохранения значения счетчика активируется флаг CFnA, а после второго срабатывания — флаг CFnB, показывая тем самым готовность данных для считывания. Если после этого данные из регистров CCnA и CCnB не были востребованы программой, к началу следующего события захвата возникает состояние «Overrun».

Если в поле TMx_ICCR.TMx_ICn_TRGS выбрано срабатывание по обоим фронтам (3), то схема работает следующим образом:

в раздельном и каскадном режимах в регистре CCnA сохраняется значение счетчика CT1 при нарастающем фронте импульса сигнала TMx_INn, а в регистре CCnB — значение счетчика CT1 при спадающем фронте импульса;

в совмещенном режиме 32-битное значение единого счетчика сохраняется в регистрах CCnA и CCnB при каждом срабатывании триггера.

Флаг CFnA активируется после сохранения значения единого счетчика при нарастающем фронте импульса, а флаг CFnB — при спадающем. Если после этого данные из регистров CCnA и CCnB не были востребованы программой, к началу следующего события захвата также возникает состояние «Overrun».

При возникновении состояния «Overrun» в зависимости от значения поля TMx_CR1.TMx_OVRn_MDS (отдельно для каждого канала) происходит следующее:

Overwritten (0) — регистры CCnA и CCnB перезаписываются новыми данными (по-умолчанию),

Keep (1) — регистры CCnA и CCnB не перезаписываются, сохраняются старые данные.

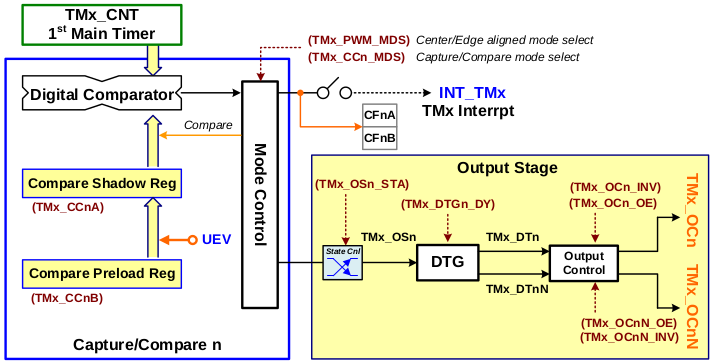

Генерация сигналов сравнения и ШИМ в 16-битном режиме

В данных режимах каждый регистр CCnA используется в качестве «теневого» 16-разрядного регистра (Shadow), с которым фактически сравнивается значение счетчика CT1. Регистр CCnB (TMx_CCnB) используется для предварительной загрузки значения сравнения (Preload) из программы. Специальный бит TMx_CCMDS.TMx_OC_LCK управляет синхронным обновлением регистров CCnA для всех каналов таймера. Когда бит установлен (locked), новые данные из регистров CCnB не загружаются в регистры CCnA, пока бит не будет сброшен. После сброса бита (unlocked, по-умолчанию) регистры CCnA будут синхронно обновлены после завершения очередного цикла счета (по сигналу TMx_UEV).

На следующем рисунке показана схема сравнения и формирования выходных сигналов в 16-битном режиме.

Схема 16-битного сравнения и ШИМ

Схема 16-битного сравнения и ШИМ

Основным выходным сигналом блока сравнения является TMx_OSn. В режимах 16bit_OC и 8bitx2_OC его начальный уровень задается битом TMx_OSCR.TMx_OSn_STA (по-умолчанию 0). Изменение значения этого бита возможно при одновременной записи логической »1» в разряд TMx_OSn_LCK этого же регистра. Алгоритм управления сигналом зависит от режима работы.

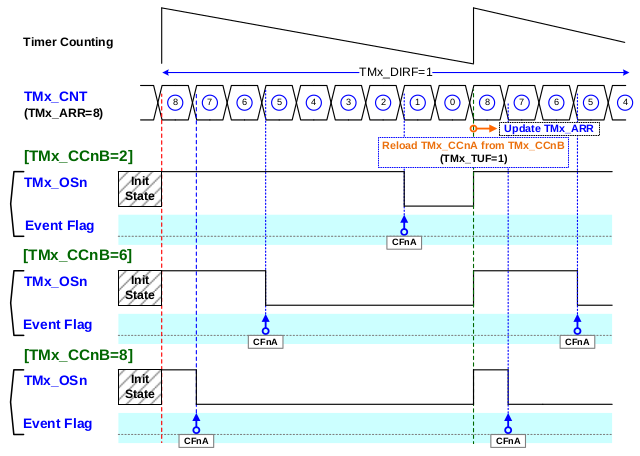

В режиме генерации сигнала сравнения (16bit_OC) при счете вверх уровень сигнала TMx_OSn изменяется на противоположный в момент достижения счетчиком CT1 значения CCnB, при этом активируется флаг CFnA. При достижении этого же значения в следующем цикле счета уровень сигнала TMx_OSn возвращается к начальному, при этом также активируется флаг CFnA. Временная диаграмма работы таймера показана на следующем рисунке.

Временная диаграмма работы таймера в режиме 16-битного сравнения

Временная диаграмма работы таймера в режиме 16-битного сравнения

Здесь коэффициент счета CT1 ARR (значение регистра TMx_ARR) выбран равным 8, показаны сигналы TMx_OSn для двух разных начальных уровней при OCnB=2 и для варианта высокого начального уровня при OCnB=8. Если значение OCnB больше ARR, состояние сигнала TMx_OSn не изменяется.

В режиме формирования ШИМ-сигнала (16bit_PWM) в начале цикла счетчика CT1 сигнал TMx_OSn переходит в состояние высокого уровня. При счете вверх в момент достижения счетчиком значения CCnB сигнал TMx_OSn переходит в состояние низкого уровня. Флаг CFnA активируется только в момент достижения значения CCnB. Длительность одного цикла счета составляет (ARR+1) тактов, а коэффициент заполнения — CCnB/(ARR+1) тактов. Пример временной диаграммы работы таймера показан на рисунке.

Временная диаграмма работы таймера в режиме 16-битной ШИМ

Временная диаграмма работы таймера в режиме 16-битной ШИМ

Здесь показаны случаи при значениях OCnB — 2, 6 и 8. Если значение OCnB больше ARR, сигнал TMx_OSn всегда остается в состоянии высокого уровня. Если значение OCnB равно нулю, сигнал TMx_OSn всегда остается в состоянии низкого уровня. Настройка начального уровня в поле TMx_OSn_STA в режиме ШИМ не используется.

В режиме формирования ШИМ-сигнала (16bit_PWM) при счете вниз сигнал TMx_OSn переходит в состояние низкого уровня в момент переключения счетчика CT1 со значения CCnB на (CCnB-1), при этом также активируется флаг CFnA. Если значение OCnB больше значения ARR, сигнал TMx_OSn всегда остается в состоянии низкого уровня. Если значение OCnB равно нулю, сигнал TMx_OSn всегда остается в состоянии высокого уровня. Пример временной диаграммы работы таймера в таком режиме показан на следующем рисунке.

Временная диаграмма работы таймера в режиме 16-битной ШИМ с обратным отсчетом

Временная диаграмма работы таймера в режиме 16-битной ШИМ с обратным отсчетом

Генерация сигналов сравнения и ШИМ в 8-битном режиме

На следующем рисунке показана схема сравнения и формирования выходных сигналов в 8-битном режиме.

Схема 8-битного сравнения и ШИМ

Схема 8-битного сравнения и ШИМ

В 8-битных режимах регистр CCnA разделяется на два 8-битных теневых регистра — старший CCnAH и младший CCnAL. Аналогично разделяется регистр загрузки CCnB на соответствующие старший CCnBH и младший CCnBL регистры. Сравнение выполняется отдельно для младшего (L) и для старшего (H) регистров, причем в сравнении участвуют только младшие 8 разрядов счетчика CT1. Соответственно, в каждом канале таймера формируется второй выходной сигнал TMx_OSnH сравнения старшего регистра, а сигналом сравнения младшего регистра остается TMx_OSn.

Начальный (неактивный) уровень сигнала TMx_OSnH задается битом TMx_OSCR.TMx_OSnH_STA. Изменение значения этого бита возможно при одновременной записи логической »1» в разряд TMx_OSnH_LCK этого же регистра.

Флаг CFnA активируется при совпадении в младшей части (L), а флаг CFnB — при совпадении в старшей (H) в обоих режимах 8bitx2_OC и 8bitx2_PWM.

Блок формирования выходных сигналов каналов сравнения

Рассмотрим блок формирования выходных сигналов одного канала таймеров TM20/26.

Блок формирования выходных сигналов таймеров TM20/26

Блок формирования выходных сигналов таймеров TM20/26

В общем случае имеется три типа выходных сигналов схемы сравнения (n — номер канала):

TMx_OCn — основной сигнал сравнения или ШИМ-сигнал,

TMx_OCnN — комплементарный к TMx_OCn сигнал,

TMx_OCnH — сигнал сравнения в старшей части для 8-битных режимов.

Для каждого из сигналов можно выбрать инвертирование установкой соответствующих битов TMx_OCn_INV, TMx_OCnN_INV и TMx_OCnH_INV в регистре TMx_OCCR1.

Сигнал TMx_OCn может быть выведен на три разных вывода, каждый из которых включается независимо. Таким образом, на внешние выводы («пины») МК от каждого канала можно вывести всего 5 сигналов: TMx_OCn0, TMx_OCn1, TMx_OCn2, TMx_OCnN и TMx_OCnH. Вывод сигналов TMx_OCn{0,1,2} и TMx_OCnN разрешается установкой соответствующих разрядов TMx_OCn_OE{0,1,2} и TMx_OCnN_OE в регистре TMx_OCCR0.

Возможно включение небольшой задержки сигналов канала 1 по отношению к сигналам канала 0 путем установки бита TMx_OCCR1.TMx_ODLY_SEL. Согласно User Guide, величина задержки составляет 3–5 нс, ее зависимость от тактовой частоты не указывается.

Таймер TM36

Функциональная схема

Функциональная схема таймера TM36 приведена на следующем рисунке.

Функциональная схема таймера TM36

Функциональная схема таймера TM36

Таймер TM36 отличается от TM20/26 следующими функциональными возможностями:

4 канала в схеме захвата/совпадения,

схема формирования «мертвого» времени для режима ШИМ (DTG),

возможность генерации «центрированных» ШИМ-сигналов,

отключение выходов по входному сигналу (блок Break Input Source),

работа в режиме DMA.

Далее рассмотрим те функции и блоки, которые отличаются от таймеров TM20/26.

Захват по входному сигналу

В данном блоке добавлена возможность использования на каналах 0 и 3 внутреннего сигнала TMx_XOR, который формируется на выходе схемы «Исключающее ИЛИ» из внешних сигналов IC0, IC1 и IC2. Сигналы от компараторов CMP0_OUT и CMP1_OUT как входные доступны только для каналов 0 и 1.

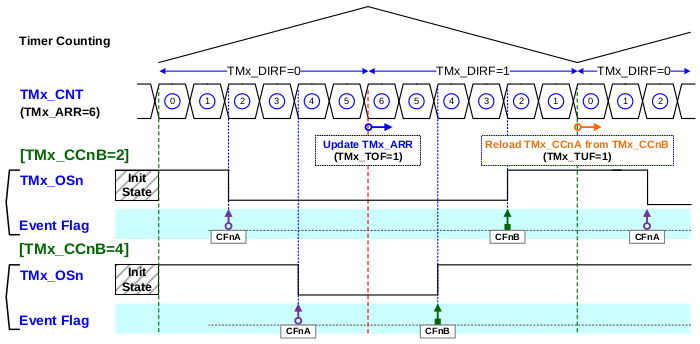

Генерация «центрированных» ШИМ-сигналов в 16-битном режиме

В таймере TM36 в поле TMx_PWM.TMx_PWM_MDS возможно включение режима ШИМ с выравниванием выходных импульсов всех каналов по центру. Общий цикл формирования ШИМ-сигнала увеличивается до 2·ARR тактов по сравнению с обычным выравниванием с циклом длительностью (ARR+1) тактов.

В начале цикла сигнал TMx_OSn находится в состоянии высокого уровня, счетчик CT1 начинает считать вверх от 0 до значения ARR. При достижении счетчиком значения CCnB сигнал TMx_OSn переходит в состояние низкого уровня и активируется флаг CFnA. В момент, когда значение счетчика изменяется с (ARR-1) на ARR, генерируется событие Timer Overflow и активируется флаг TOF. Этот момент является центром отрицательного импульса длительностью 2·(ARR-CCnB) тактов.

Далее счетчик продолжает считать вниз. При достижении счетчиком значения CCnB сигнал TMx_OSn возвращается в состояние высокого уровня и активируется флаг CFnB. В момент, когда значение счетчика изменяется с 1 на 0, генерируется событие Timer Underflow и активируется флаг TUF. Этот момент является центром положительного импульса длительностью 2·CCnB тактов. Далее счетчик продолжает считать от 0 вверх и цикл повторяется. Временная диаграмма работы таймера показана на следующем рисунке.

Временная диаграмма работы таймера в режиме 16-битной ШИМ с выравниванием по центру

Временная диаграмма работы таймера в режиме 16-битной ШИМ с выравниванием по центру

В режиме формирования ШИМ-сигнала 8bitx2_PWM флаг CFnA активируется при совпадении в младшей части (L) при счете вверх, а флаг CFnB активируется при совпадении в младшей части (L) при счете вниз.

Формирование «мертвого» времени

В блок формирования выходных сигналов каналов 0–2 добавлена схема формирования «мертвого» времени DTG (Dead Time Generator). На следующем рисунке показаны временные диаграммы работы схемы.

Временная диаграмма управления мертвым временем

Временная диаграмма управления мертвым временем

Формирование ШИМ-сигнала в каждом канале осуществляется с помощью дополнительных внутренних комплементарных сигналов TMx_DTn и TMx_DTnN, которые далее используются как выходные сигналы TMx_OCn и TMx_OCnN. Нарастающий фронт сигнала TMx_DTn задерживается относительно нарастающего фронта сигнала TMx_OSn, а нарастающий фронт сигнала TMx_DTnN задерживается относительно спадающего фронта сигнала TMx_OSn. В итоге между положительными импульсами сигналов TMx_DTn и TMx_DTnN возникает постоянная задержка, величина которой устанавливается в поле TM36_PWM.TM36_DTG_DY в периодах сигнала TMx_CK_DTG. Задержка одинаковая для всех каналов и по-умолчанию равна 0, т.е. формирования «мертвого» времени не происходит. Сигнал TMx_CK_DTG формируется на выходе делителя частоты из тактового сигнала CK_TMx, коэффициент деления 1, 2, 4 или 8 задается в поле TM36_CLK.TM36_DTG_DIV. Формирование «мертвого» времени может быть полезно при управлении «верхним» и «нижним» силовыми ключами в мостовой и полумостовой схемах для исключения сквозного тока в моменты переключения.

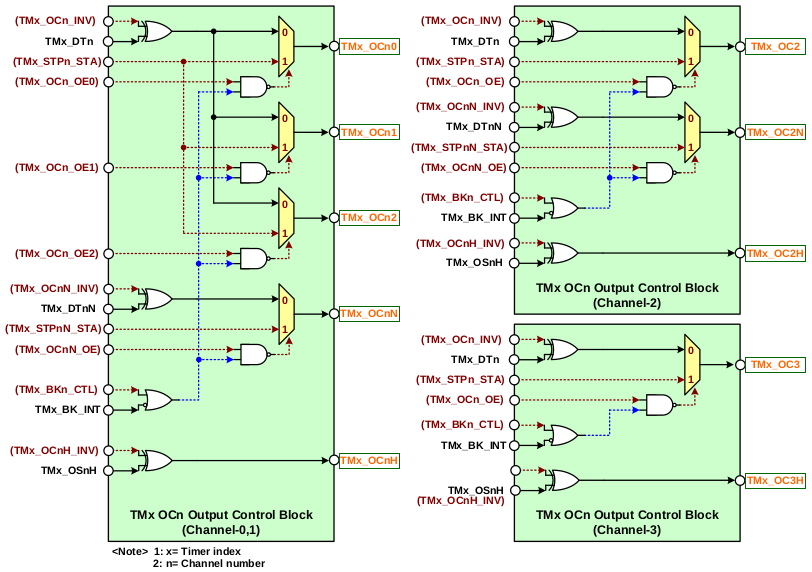

Блок формирования выходных сигналов каналов сравнения

В таймере TM36 схемы формирования выходных сигналов каналов сравнения 2 и 3 отличаются от каналов 0,1 (см. рисунок).

Блок формирования выходных сигналов таймера TM36

Блок формирования выходных сигналов таймера TM36

В каналах 0,1 для формирования сигналов TMx_OCn{0,1,2} и TMx_OCnN вместо сигналов TMx_OSn и TMx_OSnN используются сигналы TMx_DTn и TMx_DTnN. Канал 2 имеет только три внешних вывода TMx_OC2, TMx_OC2N и TMx_OC2H, а канал 3 — два вывода TMx_OC3 и TMx_OC3H. Во всех каналах для управления выходными сигналами TMx_OCn добавлена возможность использования внешнего сигнала TMx_BK_INT.

Флаги событий и прерывания

Флаги событий всех типов таймеров собраны в регистре TMx_STA, а биты разрешения прерываний — в регистре TMx_INT. Перечень событий и соответствующих флагов прерываний приведен в следующей таблице.

Разряд | Флаг события | Бит прерывания | Название события | Описание | Наличие |

|---|---|---|---|---|---|

0 | DIRF | - | Main Timer up/down counting | Направление счета счетчика CT1 | TM16, TM26, TM36 |

2 | BKF | BKIE | Break input | Сигнал отключения выходов | TM36 |

3 | EXF | EXIE | External trigger | Срабатывание внешнего триггерного сигнала | все |

4 | TOF | TIE | Main Timer overflow | Переполнение счетчика CT1 | все |

5 | TOF2 | TIE2 | 2nd Timer overfloww | Переполнение счетчика CT2 | все |

6 | TUF | TIE | Main Timer underflow | Переход через 0 при счете вниз счетчика CT1 © Habrahabr.ru |