[Перевод] История первого чипа с миллионом транзисторов. Часть 1

27 февраля 1989 года Intel Corp. представила первый в мире микропроцессор с 1 миллионом транзисторов. Он стал первым подобным чипом компании, где использовалась уменьшенная архитектура набора команд.

Команда разработчиков чипов Intel с миллионом транзисторов

Команда разработчиков чипов Intel с миллионом транзисторов

Одно только количество транзисторов уже стало огромным шагом вперёд: в предыдущем микропроцессоре Intel 80386 их было всего 275 000. Забавно, что новинка компании изрядно шокировала пользователей. Отчасти дело в том, что новый чип нарушил традицию Intel в обеспечении совместимости с более ранними процессорами, а ещё потому, что компания три года тщательно скрывала свою разработку.

Новый процессор, получивший обозначение i860, начал разрабатываться в 1986 году примерно в то же время, что и 80486 (преемник популярных Intel 80286 и 80386). Эти два чипа имеют примерно одинаковую площадь и используют одну и ту же технологию CMOS 1 мкм. Разработка велась на заводе компании в Хиллсборо, штат Орегон.

Освободившись от ограничений совместимости с семейством процессоров x86, секретная команда N10 начала практически с чистого листа.

Крестовый поход одного человека

Чистый лист недолго оставался чистым. Лесли Кон, главный архитектор проекта, уже получил прозвище Мистер RISC. Он мечтал заняться микропроцессором RISC с тех пор, как присоединился к Intel в 1982 году. На первую попытку ушло почти 18 месяцев, но технологии того времени не позволяли использовать достаточное количество транзисторов на одном чипе для достижения желаемой производительности. Позднее была сделана ещё одна попытка разработки, которая закончилась ничем, так как Intel решила не инвестировать в этот технологический процесс.

Жан-Клод Корне, вице-президент и генеральный менеджер микрокомпьютерного подразделения Intel в Санта-Кларе, увидел в N10 возможность обслуживать рынок высокопроизводительных микропроцессоров. Он предсказывал, что этот чип выйдет за рамки утилитарной линейки микропроцессоров и станет оборудованием для инженерных и научно-исследовательских сообществ высокого уровня.

Разработчики вели обсуждения с потенциальными клиентами в индустрии суперкомпьютеров, графических рабочих станций и миникомпьютеров, что привело к появлению новых требований к будущему чипу. Производители суперкомпьютеров хотели, чтобы математический сопроцессор (сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля) мог обрабатывать векторы. В итоге, чтобы избежать узких мест в производительности, весь чип был разработан в 64-битной архитектуре. Это стало возможным благодаря 1 миллиону транзисторов.

Поставщики графических рабочих станций, со своей стороны, призвали разработчиков Intel сбалансировать производительность целочисленных вычислений с производительностью операций с плавающей запятой и сделать чип способным воспроизводить трёхмерную графику.

Производители миникомпьютеров хотели скорости и подтвердили, что RISC — единственный путь к высокой производительности. Они также подчеркнули высокую пропускную способность, необходимую для работы приложений баз данных.

Команда Intel думала и о конкурентах, таких как MIPS Computer Systems Inc., Sun Micro Systems Inc. и Motorola Inc., поэтому понимала, что их чип с архитектурой RISC не будет первым на рынке, однако 64-битная технология означала, что они опередят 32-битные технологии конкурентов. Планировалась и другая архитектура с управлением памятью, кэшем, операциями с плавающей запятой и другими функциями на одном чипе, что было недостижимой для конкурентов универсальностью.

Окончательное решение было принято вице-президентом и генеральным директором группы технологий и разработки компонентов компании. Ему импонировало рвение Кона, которое тот проявлял к созданию сверхбыстрого RISC-микропроцессора, но чувствовал, что у Intel не хватает ресурсов для инвестирования в такой проект. К тому же некоторые руководители Intel явно колебались. Однако ближе к концу 1985 года было решено, что время чипов RISC пришло.

В тот момент, когда было принято решение, в январе 1986 года, стало по-настоящему жарко. Чип Intel RISC должен был выйти на рынок до того, как конкурентные проекты прочно там укоренятся. А поскольку проект стартовал одновременно с 486, им пришлось бы конкурировать, так что разработчики постоянно следили и прилагали все усилия, чтобы N10 постоянно опережал 486.

Подбор персонала

Как только проект был утверждён, Сай Вай Фу, инженер завода в Хиллсборо, переехал в Санта-Клару и присоединился к Кону в качестве соруководителя группы. Фу и Кон были уже знакомы, они оба учились в Калифорнийском технологическом институте в Пасадене, и вновь воссоединились в Intel, чтобы работать над RISC. Фу изо всех сил пытался собрать группу талантливых инженеров. Помимо своего желания преодолеть барьер в миллион транзисторов, он следовал собственной философии управления: расширить кругозор инженеров, бросив им вызов за пределами их областей знаний.

Хон П. Сит, инженер-конструктор, также выбрал N10 вместо 486, потому что с 486 ему пришлось бы работать над логикой управления, и он многое об этом знал. А N10 нужны были люди для работы над модулем с плавающей запятой, о которой разработчик почти не знал, поэтому ему было интересно учиться.

Помимо «беглецов», как назвал их менеджер группы 486 Джон Кроуфорд, группа N10 привлекла трёх специалистов по проектированию памяти из групп разработки технологий Intel, что было важно, поскольку внутри чипа должно было быть много памяти. Также Кон и Фу взяли на работу нескольких инженеров, только что окончивших учебные заведения. Количество инженеров выросло до 20. Это на восемь больше, чем они планировалось, но гораздо меньше, чем было в команде 486.

Проект на бумаге

В первые месяцы 1986 года Кон усовершенствовал свои идеи относительно архитектуры N10. Предполагалось, что и N10, и 486 будут иметь толщину около 10 мм, и это вызывало некоторые опасения. Но чип становился менее функциональным, если пытаться сделать его тоньше. И пришлось признать, что иначе никак. Получилось даже больше. Фактически размеры i860 — 10 на 15 мм.

Кон начал с требования к высокой производительности для целочисленных вычислений, большого кэша для данных и инструкций, а также специализированной схемы для быстрых вычислений с плавающей запятой. В то время как большинству микропроцессоров требуется от 5 до 10 тактовых циклов для выполнения операции с плавающей запятой, цель Кона состояла в том, чтобы сократить это время до одного цикла с помощью конвейерной обработки. Он также хотел, чтобы шина данных была 64-битной, но со 128-битной шиной между кэшем данных и секцией с плавающей запятой, чтобы секция с плавающей запятой не попадала в бутылочное горлышко при доступе к данным. Подобно суперкомпьютеру, чип должен был бы выполнять векторные операции, а также параллельно выполнять разные инструкции.

Лесли Кон, главный архитектор вычислительного микропроцессора Intel с 1 миллионом транзисторов (слева) и Сай-Вай Фу, руководитель проекта (справа).

Лесли Кон, главный архитектор вычислительного микропроцессора Intel с 1 миллионом транзисторов (слева) и Сай-Вай Фу, руководитель проекта (справа).

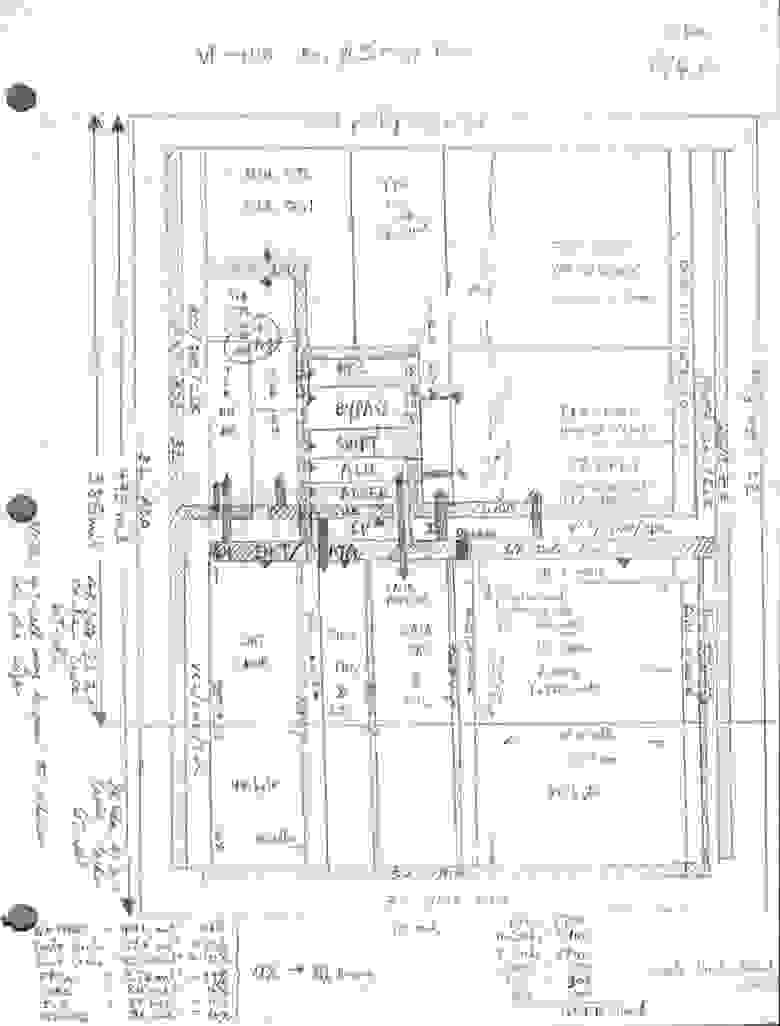

В начале апреля Фу взял карандаш и лист бумаги и набросал схему чипа, разделённую на восемь разделов: целочисленное ядро RISC, блок подкачки, кэш инструкций, кэш данных, сумматор с плавающей запятой, умножитель с плавающей запятой, регистры с плавающей запятой и контроллер шины. Он также раздумывал над рядом вопросов: например, взять ли для области кэша размер строки 32 байта. (Строка любой длины — это набор ячеек памяти, наименьшая единица памяти, которую можно перемещать туда и обратно между кэшем и основной памятью.) Хотя меньший размер строки немного улучшил бы производительность, в этом случае пришлось бы менять форму, что сделало бы его неудобным для размещения на чипе. Поэтому был выбран наименьший размер строки, который только возможен при условии сохранения нужной формы.

Черновик также фактически прикончил одну из идей Кона: кэш данных, разделённый на четыре 128-битных отсека для создания четырёхстороннего параллелизма, называемого четырёхсторонним ассоциативным набором. Когда Фу нарисовал план, он понял, что разделение на четыре не сработает. С двумя отсеками данные могут течь из кэша по прямой линии в модуль с плавающей запятой. При четырёхстороннем параллелизме пришлось бы сгибать сотни проводов. Он увидел, что отказ от четырёхстороннего разделения приведёт к снижению производительности всего на 5 процентов, поэтому выбрал двухсторонний кэш.

На черновике в итоге остался блок пустого пространства. «Я понимал, что не следует уплотняться по максимуму, пока не знаешь деталей, потому что всё увеличивается», — сказал Фу. В итоге пустое пространство было заполнено и потребовалось даже немного больше места. Затем, ближе к концу процесса проектирования, инженер извиняющимся тоном сказал: «Когда я складывал эти блоки вместе, я добавлял их неправильно. Я пропустил 250 микрон».

Это была простая ошибка, которую тяжело исправить. Нужно найти место для 250 микрон, но в технологических процессах добавление сотни микрон здесь или там может значительно снизить производительность. Разработчики испробовали все способы, какие только могли придумать, чтобы компенсировать ущерб, но в конце концов, пришлось увеличить чип.

Черновик Сай-Вай Фу

Черновик Сай-Вай Фу

Поскольку эскиз Фу делил чип на восемь блоков, команду тоже поделили на восемь групп по два-три инженера, в зависимости от сложности блока. Группы начали работу над логическим моделированием и проектированием схем, в то время как Кон продолжал дорабатывать архитектурные спецификации.

Энергопотребление поначалу вызывало серьёзные опасения. Кон и Фу подсчитали, что чип должен потреблять 4 Вт на частоте 33 мегагерца. Фу разделил бюджет мощности между командами, выделив полватта туда, ватт туда. «Я сказал им уйти, сделать свой дизайн, а затем, если превысите свой бюджет, вернуться и сказать мне».

Особое беспокойство вызывали широкие шины. Разработчики обнаружили, что одна ячейка памяти на микросхеме управляет длинной линией передачи с ёмкостью от 1 до 2 пикофарад; к тому времени, когда достигается пункт назначения, сигнал становится очень слабым и нуждается в усилении. Для кэш-памяти требовалось около 500 усилителей, примерно в 10 раз больше, чем для микросхемы памяти. Как и большинство статических ОЗУ, эти усилители потребляли 2,5 Вт — более половины энергопотребления всего чипа. Создание SRAM с использованием методов схемотехники, заимствованных из технологии динамической RAM, сократило это значение примерно до 0,5 Вт.

«Оказалось, что в то время как некоторые группы превышали свой энергетический бюджет, другие в него укладывались, хотя я намеренно занизил цифры. Я хотел их немного напугать, чтобы они не вышли за рамки и не сожгли слишком много энергии», — сказал Фу. В паспорте фактического чипа заявлено 3 Вт.

Одна инструкция, один такт

Чтобы достичь цели по производительности, разработчики сделали выполнение каждой инструкции за один такт чем-то вроде религии. Это потребовало целый ряд новаторских поворотов. Для RISC-процессоров характерно использование чуть менее двух тактов на инструкцию, поэтому цель команды N10 — одна инструкция на такт — казалась достижимой, но такие скорости необычны для многих других функций чипа.

Необходимо было разработать новые алгоритмы для обработки сложений и умножений с плавающей запятой за один цикл в конвейерном режиме. Алгоритмы с плавающей запятой входят в число 20-ти нововведений чипа.

Однако деление с плавающей запятой занимает от 20 до 40 циклов, и разработчики заранее поняли, что им не хватит места на микросхеме для специальной схемы, необходимой для такой редкой операции.

Разработчики сумматора и множителя с плавающей запятой привели логику округления чисел в соответствие со стандартами IEEE, что снизило производительность. (Компьютеры Cray Research Inc., например, отвергают эти стандарты для повышения производительности.) Хотя некоторые инженеры N10 хотели более высокой производительности, выяснилось, что клиенты предпочитают соответствие стандартам.

Тем не менее, разработчики нашли способ добиться трёхмерной графики, которая требуется инженерам и учёным, без болезненных компромиссов. Помогло включение небольшого количества дополнительных схем в оборудование для операций с плавающей запятой, что увеличило размер чипа всего на 3 процента, но повысило скорость обработки графических вычислений в 10 раз, до 16 миллионов 16-битовых элементов изображения в секунду.

С процессором RISC для выполнения загрузки из кэш-памяти за один такт обычно требуется дополнительный порт записи регистра, чтобы предотвратить помехи между информацией о загрузке и результатом, возвращаемым из арифметико-логического устройства. Команда N10 придумала, как использовать один и тот же порт для обеих частей информации в одном цикле и таким образом сэкономить без потери скорости.

Быстрый доступ к инструкциям и данным является ключевым моментом для RISC-процессора: поскольку инструкции просты, их может потребоваться больше. Разработчики создали и запатентовали новые методы схемотехники, чтобы обеспечить доступ за один цикл к большой кэш-памяти через очень большие шины, потребляющие всего 2,5 Вт.

«Существующие части SRAM могут получить доступ к данным за сопоставимое время, но они потребляют много энергии», — сказал Кон.

Никакого раздутого элегантизма

Миллион транзисторов означал, что большая часть двух с половиной лет разработки была потрачена на проектирование схем. Восемь групп, работающих над разными частями чипа, требовали тщательного координирования, чтобы каждая часть гарантированно работала с остальными после сборки.

Прежде всего, это была философия дизайна N10: никакого раздутого элегантизма. «Раздутый элегантизм убил много чипов», — сказал Роланд Альберс, руководитель группы разработчиков схем. Разработчики схем, по его словам, не должны изобретать велосипед. Если типичный цикл составляет 20 наносекунд, а установленная технология ведёт к 15 нс, инженер должен принять это и перейти к следующей схеме.

Временные параметры были задокументированы в первоначальных спецификациях проекта и обновлялись на еженедельных встречах, которые Альберс собирал после фактического проектирования схем.

Чтобы гарантировать, что схемы различных блоков микросхемы будут чётко соединяться, Альберс и его разработчики написали руководство, описывающее их работу. Вместе с инженерами из отдела САПР Intel он разработал графическую среду моделирования цепей, с помощью которой инженеры вводили схемы моделирования, включая паразитную ёмкость устройств и межсоединений, в графическом, а не буквенно-цифровом виде. Затем выходные данные анализировались на рабочей станции в виде графических сигналов.

На еженедельных собраниях каждый инженер, завершивший часть проекта, представлял свои результаты. Остальные должны были убедиться, что он не идёт на ненужный риск и придерживается установленной методологии, а также, что его часть будет интегрироваться с другими частями чипа.

У Intel были инструменты для работы на высокуровневом языке, имитирующего логику чипа. Стоит ли их использовать? Такие инструменты экономят время и устраняют ошибки, допущенные разработчиками-людьми, но, как правило, схемы получаются не слишком компактными. Собственные инструменты Intel для проектирования компоновки сократили плотность примерно вдвое и замедлили работу на одну треть по сравнению с ручным проектированием схем. Коммерчески доступные инструменты, по словам инженеров Intel, работают ещё хуже.

Решить, когда и где использовать эти инструменты, было достаточно просто: те части логики с плавающей запятой и ядра RISC, которые управляют данными, должны были разрабатываться вручную, как и кэши, потому что они требовали большого количества повторений. Некоторые ячейки повторяются сотни, даже тысячи раз (ячейка SRAM повторяется 100 000 раз), поэтому при ручной упаковке они занимают в два раза меньше места.

Однако с логикой управления, где повторений мало или совсем нет, экономия времени считалась оправданной, особенно потому, что автоматическое создание схемы позволяло вносить изменения в последнюю минуту для исправления работы чипа.

Около 40 000 транзисторов из более чем миллиона чипов были размещены автоматически, а около 10 000 — вручную и воспроизведены для производства оставшихся 980 000. «Если бы нам пришлось делать эти 40 000 вручную, это добавило бы к графику работ несколько месяцев и возникло бы больше ошибок», — рассказывал Роберт Г. Вилонер, один из инженеров компании.

Эти инструменты для создания компоновки использовались в Intel и раньше, так что команда была уверена, что они будут работать. Вопрос был в том, сколько места займут автоматически спроектированные схемы. По словам Альберса, «это заняло немного больше времени, чем мы думали, что вызвало некоторые проблемы ближе к концу, поэтому нам пришлось немного увеличить размер кристалла».

Продолжение следует…