[Перевод] Аппаратные трояны под микроскопом

Хотя индустрия кибербезопасности в основном сфокусирована на атаках на программное обеспечение, не стоит забывать о влиянии на безопасность аппаратных дефектов более низкого уровня, например, тех, которые касаются полупроводников. За последние несколько лет площадь атаки на уровне кремния сильно расширилась. Так как в производстве интегральных схем (ИС) используется всё более сложная микроэлектроника, риски пороникновения дефектов в эти системы возрастает.

Процесс проектирования интегральных схем (ИС)

В этой статье мы расскажем об аппаратных троянах, в том числе о списках соединений, подготовке кристаллов, снимках электронных микроскопов и тестировании цепей. Также мы создадим собственную архитектуру и схему аппаратного трояна, которая будет проанализирована при помощи Klayout.

Прежде чем погрузиться в исследование аппаратных троянов, давайте узнаем, как проектируются кремниевые чипы, чтобы в дальнейшем мы могли изучить их при помощи реверс-инжиниринга. Можно начать с поведенческого уровня процесса. Register-transfer level (RTL, уровень межрегистровых передач) определяет, как располагаются регистры и логические вентили.

Конструкция схемы D-триггера

RTL-проектирование существенно упростилось в 1983 году, когда Министерство обороны США разработало первый hardware description language (HDL, язык описания аппаратуры) для документирования поведения архитектур application-specific integrated circuit (ASIC, интегральных схем специального назначения). Приблизительно в то же время появились VHDL и Verilog, которые и по сей день являются двумя самыми популярными HDL. Эти языки разработаны в качестве специализированного компьютерного «жаргона» для программирования цифровых логических схем. Если мы возьмём показанную выше RTL-диаграмму и преобразуем её в код на Verilog, то он будет выглядеть так:

always @(posedge clk)

begin

Q <= D;

end

assign D = ~Q;

Этот простой фрагмент кода можно синтезировать в архитектуру логического вентиля. Логический синтез — это автоматизированный процесс преобразования кода на HDL-языке наподобие Verilog или VHDL в оптимизированное представление на уровне вентилей. При реверс-инжиниринге снимков кремниевых кристаллов первая задача — понять то, как преобразовать все эти слои в список соединений транзисторов. Гляда на нечто с вентилем XOR, имеющим два входа, без наличия значков компонентов RTL, заменяющих транзисторы, мы можем разработать такую схему:

Схема соединений вентиля XOR

Для создания этой схемы соединений комплементарной структуры металл-оксид-полупроводник (КМОП) понадобилось всего шесть транзисторов. Далее в нашем экскурсе в процессе реверс-инжиниринга мы преобразуем этот список соединений в RTL-схему, а затем в HDL, показанные на изображениях и во фрагментах кода выше.

Для обнаружения аппаратных троянов нам нужен голый кристалл, а также некоторая подготовка, о которой я расскажу далее. Я не буду касаться процесса извлечения из корпуса и снятия слоев интегральных схем, поскольку уже написал об этом статью, но вам необходимо понимать, как получить эти крошечные кремниевые кристаллы и как получить их изображения.

Аппаратный троян может представлять собой цепь, вредящую работе или снижающую надёжность электронной системы (например, интегральной схемы). Схемы подвержены этому типу атак на уровне физической структуры или на уровне вентилей. В частности, трояны уровня вентилей — это функциональные модификации или параметрические отклонения от предусмотренного назначения компонента, которых можно достичь добавлением или удалением вентилей. Труднообнаружимые трояны можно использовать для ослабления надёжности криптопроцессора путем:

- снижения эффективной энтропии генератора случайных чисел;

- передачи нападающему информации о внутренней работе процессора.

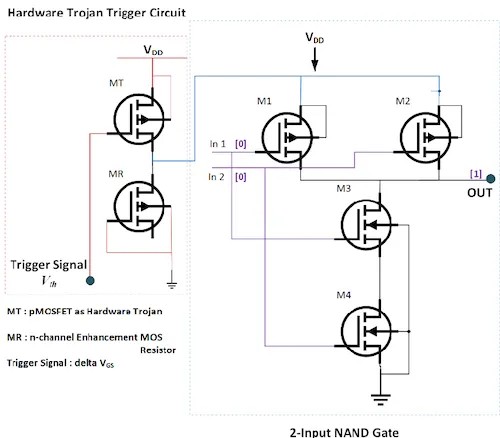

Ниже представлен пример аппаратного трояна, срабатывающего благодаря пороговому напряжению (HTVth) в комбинационной схеме (вентиль NAND с двумя входами).

Согласно статье Ingress of Threshold Voltage-Triggered Hardware Trojan in the Modern FPGA Fabric — Detection Methodology and Mitigation, HTVth проектируются таким образом, чтобы:

- задача передачи схемы трояна была линейной;

- чувствительность к температуре и изменениям порогового напряжения была очень высокой;

- изменения на выходе должны были достаточно высокими для изменения входа;

- сохранялась незначительная временная деградация и устойчивость к изменениям параметров техпроцесса.

Троянские схемы должны сохранять низкое энергопотребление, без ущерба для эффективности срабатывания полезной нагрузки. Показанная выше схема не потребляет ток в спящем состоянии, поэтому её сложно обнаружить. Методики наподобие анализа сигнатур энергопотребления не смогут с уверенностью сказать, что в данный конкретный вентиль NAND внедрен троян.

В этом примере нападающий с лёгкостью может контролировать выход вентиля NAND с двумя входами. При A(1) NAND B(0) == AB(1) мы ожидаем, что 1 и 0 на входе должны дать на выходе высокое напряжение. Однако, благодаря трояну уравнение A NAND B будет иметь результат, противоположный ожидаемому. Аппаратный троян (HWT) может так же легко менять определенные входные контакты или подменить ожидаемые результаты. Такая закладка может помочь получить доступ к встроенным учётным данным, ключам, коду и многому другому.

Существует множество способов внедрения троянов, потому что существует множество разных типов троянов.

Один из них умеет размещать фиксированные входы, подающие питание на двойной flip flop таким образом, что микросхема все равно пройдет встроенный built-in self-test (BIST). Это может упростить обход механизма безопасности режима отладки. Другой тип открывает возможность для атак по сторонним каналам. Третий тип (троян этапа компоновки) может быть инъецирован во множество разных точек, особенно если в единую структуру объединено несколько IP-ядер. В принципе, одна архитектура может пасть жертвой нескольких троянов, созданных разными группами злоумышленников.

RTL-вставка — один из самых популярных способов внедрения аппаратных троянов. Сам троян может быть объектом системного уровня, преобразуемым в зловредный RTL или может быть внедрён на этапе компоновки ASIC. Кроме того, троян может маскировать подготовку, изменяя данные для маскировки схемы, которая уже находится в производстве. Это реализуется при помощи технологий повышения разрешения (resolution enhancement technology, RET), такими как optical proximity correction (OPC), которая корректирует волновое поведение света при травлении наномерных атрибутов на самых современных интегральных схемах. Подробнее об этом можно прочитать в статье Википедии, посвящённой Tape-out.

Изменение маски может, например, поменять полярность легирующей примеси в транзисторе, с n-типа на p-тип, или наоборот. Исследователи из Horst Görtz Institute for Semiconductor Security заявляют, что это крайне сложно обнаружить, особенно если изменения выполняются после завершения контроля. Подлог позволяет внести изменения непосредственно перед изготовлением маски.

p-примесь с изменённым размером используется для воздействия на поведение ячейки AOI (иллюстрация из «Hardware Trojan attacks and countermeasures»)

В показанном выше случае, представленном Бекером и соавторами, инвертор можно модифицировать для получения неверного выходного значения. Например, сигнал Vdd может быть постоянно высоким, если поменять маску p-примеси на версию n-типа; или же величина Vdd может быть изменена уменьшением ширины транзистора p-channel metal-oxide semiconductor (PMOS). На изображении выше p-примесь охватывает всю область Vdd, однако в схеме трояна (справа) она занимает только половину транзисторов на стороне Vdd.

Трояны, способные воздействовать более чем на один путь, имеют более высокие шансы быть обнаруженными. При этом, маловероятно, что трояны с низкой переходной вероятностью повлияют на энергопотребление схемы. Даже если цепи подобраны из некритических путей без общих сегментов, выявить трояны при помощи технологий на основе задержек будет чрезвычайно сложно. Этот метод тестирования был испробован на схеме Ethernet MAC 10GE, где чип спроектирован по техпроцессу 90 нм. В нее был внедрен компараторный троян, который контролирует состояние шины данных. Как показано выше, логика компараторов переключается при изменении параметров шины данных, а значит, потребляет значительное количество энергии.

Компараторный троян

Как видите, вставка троянов на уровне RTL или даже вентилей — достаточно сложная задача, и при неправильной реализации такая модификация может иметь множество последствий, например, общее увеличение энергопотребления или возникновение сбоев.

Обнаружено, что анализ сигналов побочных каналов (side-channel signal analysis) и анализ вероятности изменения питания (power transition probability analysis) показали самое высокое и точное число цепей и переходных вероятностей благодаря тому, что они могут выявлять аномалии питания, возникающие из-за работы компараторов. Исследователи показали, что этот метод лучше таких техник, как анализ задержек и структурный анализ (которые не обнаруживают неисправностей, которые можно было найти в схеме).

Если посмотреть на трояны с точки зрения топологии, ситуация немного изменится. Чаще всего при проектировании схем остается много неиспользуемого пространства или даже целых областей, подвергаемых химически-механической полировке (CMP). Элементы троянов, размещенные в областях, не используемых в схеме, сильнее влияют на энергопотребление, чем все перечисленные выше способы.

Был разработан метод анализа топологии схемы и выявления возможных мест размещения элементов троянов, занимающих неиспользуемое пространство. Определяется распределение элементов и пустых зон в топологии схемы, после чего выявляются возможные места для элементов (троянской — прим. переводчика) схемы.

Применение оптических методик реверс-инжиниринга может многое открыть исследователю. Для выявления троянов можно использовать распространенные микроскопы, например, составные микроскопы, стереомикроскопы и даже микроскопы, применяемые в металлургии. Однако отраслевые стандарты обычно требуют применения сканирующих электронных микроскопов(СЭМ), потому что ИС становятся всё меньше. Для дальнейших исследований необходимы более продвинутые технические возможности. В процессе подготовки чипа к выявлению скрытых троянов некоторые операции проводят при помощи легирования, требующего применения реагентов для химического травления.

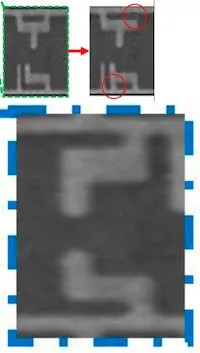

Как показано на увеличенном изображении ниже, вентиль исходного дизайна (КМОП-инвертор) модифицирован с изменением полярности при помощи легирования отдельных частей активной поверхности вентиля.

Изображение трояна с СЭМ на 130-нанометровом чипе (иллюстрация из «The State-of-the-Art in IC Reverse Engineering»)

Согласно исследованию, проведённому Университетом Северной Каролины, подобным образом им удалось установить выход транзистора на конкретное значение и/или даже менять допустимую нагрузку по току.

Университет Флориды провел на специальном КМОП-чипе похожее исследование по обнаружению троянов при помощи различных напряжений электронного пучка. Благодаря этой методике они смогли использовать быструю электронную микроскопию, обработку изображения и алгоритмы компьютерного зрения для выявления вставок, изъятий и модификаций при сравнении чипа без троянов и с IC Under Authentication (IUA).

Как говорилось выше, для подготовки чипа к визуализации необходима подготовительная работа, потому что электроны не могут проникнуть через толстый слой подложки из диоксида кремния (SiO2). Наиболее популярный способ удаления SiO2 — это механическая полировка, поскольку её проще контролировать, чем, например, погружение чипа в плавиковую кислоту, как описано в моей предыдущей статье.

Чтобы обеспечить равномерное утоньшение подложки, исследователи использовали VarioMill. Это устройство использует лазерно-химическое травление, адаптивную микрообработку при помощи пятиосевого ЧПУ и VIS/IR-спектрометрию для уменьшения толщины покрытия до 1 мкм.

Цель здесь заключается в том, чтобы сделать СЭМ-снимки IUA и сравнить их с эталонной ИС. Для создания качественного снимка IUA СЭМ нужно задать определённые параметры, такие, как напряжение электронного пучка, угол обзора, продолжительность выдержки (время) и разрешение. Микроскоп можно запрограммировать на съёмку всей ИС с заданными параметрами.

Вариации СЭМ-снимков с разными напряжениями пучка (изображение из «Detecting Hardware Trojans»)

Для симуляции действий трояна исследователи внесли изменения на уровне легирования и затем получили их изображение при помощи СЭМ. В некоторых из этих примеров атакующий потенциально мог заменить вентиль NAND на вентиль NOR, который, по сути, реализует зловредную логику при помощи таких методов, как модификация активной области, маскировка элементов на первом металлическом слое или вставка/удаление логики в активной области (например, добавление инвертора).

Наверху: NAND/NOR, внизу: инвертор (изображение из «Detecting Hardware Trojans»)

В современных микроконтроллерах и CPU от десятков тысяч до миллиардов вентилей, и, чтобы проанализировать их, потребуется множество изображений с микроскопа. Вот почему автоматизация является ключевым фактором при сборе информации как об обычных микросхемах, так и о схемах с троянами.

Перспективными оказались и другие проверенные методы, в частности, тестирование задержек путей. В йельском эксперименте исследователи вставили троян на основе двухбитного компаратора рядом с входом DES-ядра микросхемы. Задержки путей используются для создания фингерпринтов номинального чипа. Каждый путь в списке соединений включается в данные трассировки. Каждый фингерпринт описывает один аспект из общих характеристик подлинной конструкции чипа. Затем микросхемы валидируются при помощи сравнения их параметров задержек путей с фингерпринтами, которые достаточно значимы в случае крошечных троянских схем. В итоге, исследователи пришли к выводу, что подлинными можно считать только те чипы, где точки выборки (sample points) находятся на пересечении всех заданных множеств во всем пространстве фингерпринтов или вблизи него. Если одно или несколько пространств точек выборки расположено далеко от такого пересечения, то считается, что в чип встроен троян.

Далее мы рассмотрим то, как создать аппаратный троян (Hardware Trojan, HWT) при помощи опенсорсных инструментов Electronic Design Automation (EDA), чтобы показать, как это выглядит на уровне дизайна произвольного чипа.

Изучив аппаратные трояны по множеству различных источников, будет интересно создать собственный троян от RTL до GDSII, в котором мы сможем изучить свой чип при помощи ПО 3D-рендеринга наподобие GDS3D. Прелесть проектирования собственного инфицированного чипа заключается в том, что мы можем посмотреть, как использовать для этого инструменты с открытым исходным кодом, сможем взглянуть на интегральную схему без микроскопа, а также сможем увеличить ее настолько, насколько захотим, используя ПО.

Давайте рассмотрим структуру чипа на уровне вентилей обычной логической схемы AND-OR с четырьмя входами, и сравним её с той же структурой, содержащей троян. Мы преобразуем схему в код на Verilog, а затем воспользуемся или QFlow с OSU PDK, или Openlane с Skywater130 PDK для создания файлов GDSII, чтобы изучить структуру ASIC, будто через увеличительное стекло.

Структура с инъецированным трояном (из «Exposing Hardware Trojans in Zero-Knowledge»)

В работе Димитриса Моуриса, Шарля Гуера и Нектариоса Георгиоса Тсоутсоса, вентили помечены в порядке анализа (сначала G1, потом G2 и так далее). В строках таблиц также указана трассировка исполнения, показывающая вывод четырёх регистров State Machine (SM), определённых переменными r0 — r3. Выделенные и подчёркнутые значения в таблицах показывают, какая переменная симуляции была перезаписана после анализа вентиля. На диаграмме (a) показана схема, выводящая 1, когда на все четыре входа подан сигнал HIGH. На диаграмме (b) показана та же схема, что и на (a) после инъецирования примера трояна, который активируется только тогда, когда все входы установлены на 1.

Существует два способа преобразования логики на уровне вентилей в Verilog: вручную или при помощи инструмента Digital. Можно нарисовать схему, после чего программа преобразует её в выбранный нами HDL. Я выберу более легкий второй вариант.

module non_active_hwt (

A,

B,

C,

D,

Y

);

input A;

input B;

input C;

input D;

output Y;

assign Y = ((((A & B) | (C & D)) | (C & D)) & D);

endmodule

Сгенерированный код Verilog для структуры, которая не содержит троян, достаточно прост. Вывод Y зависит от четырёх входов, проходящих через логический AND в трёх группах, пока две группы подвергаются OR для вывода, чтобы ещё раз выполнился AND со входом D. Теперь давайте взглянем на код, сгенерированный с инъецированным трояном.

module active_hwt (

A,

B,

C,

D,

Y

);

input A;

input B;

input C;

input D;

output Y;

assign Y = ((((A & B) & (C & D)) ^ (((A & B) | (C & D)) | (C & D))) & D);

endmodule

Он достаточно сильно похож на код без трояна, однако содержит операцию XOR вместе с дополнительным AND со входами C и D. Можно воспользоваться EDA Playground для симуляции волновых паттернов, применив для обеих схем простую тестовую среду. Если вы незнакомы с процессом написания тестовых сред, то можете изучить, как они пишутся, посмотрев мой код. По сути, мы тестируем входы A, B, C и D, чтобы проверить, насколько сложно будет заметить разницу с точки зрения формы сигнала. Помните, что осциллограмма должна демонстрировать активацию трояна только в случае 4'b1111, все остальные входные и выходные сигналы должны отзеркаливать друг друга.

Сверху: без вставки HWT, снизу: со вставленным трояном

Обе схемы очень похожи друг на друга в том, как переключается Y, но если приглядеться к форме сигнала на выходе без аппаратного трояна, то можно увидеть разницу. Когда A, B, С и D переключены на 1, то на выходе Y ожидается 1. Обратите внимание, что, когда мы тестируем те же входы с кодом, куда вставлен троян, на выходе Y при активации всех четырёх контактов получается 0. То есть мы нашли триггер трояна, а обе архитектуры RTL ведут себя почти идентично. В 54 строке тестового кода видно, что если бы мы забыли протестировать все входы, находящиеся в активном состоянии, то сгенерированные формы сигналов для обеих схем были бы идентичными.

Давайте перенесём эти схемы на этап подготовки к изготовлению и посмотрим, насколько сложно будет выявить различия между архитектурами ASIC. Мы можем сделать это, выполнив процесс установки QFlow, при котором будут установлены все зависимости наподобие yosys, netgen, graywolf, qrouter и magic. При помощи QFlow GUI выможете указать на файл Verilog, который хотите подготовить к синтезу.

В раскрывающемся меню technology есть множество опций, я решил выбрать последний PDK, то есть OSU018. Это значит, что проектирование будет выполняться в масштабе 180 нм. Выполнив синтез, пройдя через процесс размещения, STA, маршрутизации и так далее, вы получите файл .gds, находящийся в папке /layout/. При помощи Klayout мы сможем открыть файл GDSII в программе.

Структура компоновки и маршрутизации для схемы без аппаратного трояна

Этот простой дизайн ИС разбит на несколько очень простых логических вентилей. Первый — это AOI21×1 — вентиль-инвертор AND-OR с тремя входами, имеющий функцию Y=!((A&B)|C).

Подложка AOI21×1

При снятии слоёв видно, что наш дизайн соответствует функции AOI и содержит шесть транзисторов PNP и NPN. Если сравнить это с дизайном AOI21×1 в архитектуре со вставленным HWT, то они выглядят совершенно одинаково. На самом деле, обе архитектуры содержат BUFX2 (неинвертирующий буфер [Y=A]), INVX1 (Инвертор [Y=!A]) и NAND2×1 (вентиль NAND с двумя входами [Y=!(A&B)]). Давайте посмотрим, какие стандартные элементы появились в инфицированной схеме.

Структура компоновки и маршрутизации для схемы с аппаратным трояном

Как видите, троян уже не такой незаметный, как на уровне RTL-симуляции или при вставке троянов на уровне легирования, поскольку теперь, похоже, в схеме есть дополнительная пара вентилей. На нашем дизайне видно, что рядом с исходным элементом NAND2×1 появился NAND3×1. Кроме того, добавился ещё один вентиль NAND с двумя входами рядом с неинвертирующим буфером.

Подложка обоих вентилей NAND

Слева мы видим четыре транзистора, составляющих вентиль NAND с двумя входами, а выход Y этого вентиля соединён со входом A вставленного вентиля NAND с тремя входами (справа), который влияет на выход этого вентиля. Этот дополнительный вентиль состоит из шести транзисторов, то есть в инфицированном дизайне ИС добавилось лишних десять транзисторов. Где же они все соединяются, чтобы повлиять на физический выходной контакт?

Физический выход Y

Снова вернув слои, мы видим, что на верхнем металлическом (зелёном) слое есть два физических контакта, вход D и выход Y. Два дополнительных вентиля NAND, вставленных в этот дизайн, в конечном итоге повлияют на выход этого контакта при выполнении конкретного условия-триггера; в нашем случае это момент, когда на всех физических контактах входа будет значение 1. Сравнивая наш код Verilog с дизайном ИС, можно увидеть сходство между ними и понять, почему сложно отслеживать подобные проблемы на некоторых этапах подготовки к изготовлению. Мы можем посмотреть на 3D-модель, чтобы увидеть, как это будет выглядеть на кристалле.

Отрендеренная в 3D топология (сверху: без HWT, снизу: с HWT)

Если бы не дополнительные заполнители (две большие пустые оранжевые и жёлтые области) на нижнем дизайне с HWT, которые были автоматически размещены и маршрутизированы при помощи QFlow, схемы выглядели бы практически идентично, потому что два описанных выше дополнительных вентиля особо ничего не добавляют к дизайну.

Возможно, вы задаётесь вопросом, в какой ситуации этот троян может нанести вред? Хороший вопрос! Представьте, что если на всех этих четырёх входных контактах сигнал HIGH, то и на выходе ожидается HIGH, который позволяет ИС зафиксировать процесор в безотладочном состоянии. После того, как из-за нашей атаки дизайн изменился, при сигнале HIGH на всех контактах на выходе будет LOW. Это переведет CPU в состояние отладки, что позволит атакующим узнать приватную информацию о вашей SoC (System on Chip) и получить интеллектуальную собственность, которая не должна была стать общедоступной.

В этой статье мы рассмотрели небольшую часть способов, которыми можно внедрять трояны, изучили способы их выявления и спроектировали с нуля собственный троян. Благодаря этому исследованию мы смогли в реальности увидеть, как выглядел бы инфицированный чип на разных этапах производственного цикла.

Вот репозиторий, в котором содержатся все файлы HDL и файлы проектирования, которые я создал на этапе исследования при размещении и маршрутизации своей ИС с трояном: https://github.com/ryancor/HWT-Verilog.

Особая благодарность одному из редакторов этой статьи, Мэттью Венну и его курсу Zero to ASIC, который вдохновил меня взяться за изучение проектирования чипов.