Согласование импедансов: симуляторы и симуляция. Часть 2

Согласование импедансов: как сломать и как починить

Согласование импедансов: симуляторы и симуляция. Часть 1

Согласование импедансов: симуляторы и симуляция. Часть 2

В предыдущей статье мы познакомились с общей идеологией симуляции при согласовании импедансов на примере бесплатного ПО. Посмотрим теперь, каких результатов можно ожидать от пакетов, которые используются в промышленности и стоят денег.

Для начала посчитаем импеданс дорожек на плате. Возьмём для примера две дорожки из этой статьи.

Обе дорожки расположены на двухслойной плате из текстолита FR4 (диэлектрическая проницаемость ε=4,6) толщиной 1,5 мм и имеют длину 40 сантиметров каждая. Номинальная ширина первой — 1,05 мм. Она была выбрана так, чтобы импеданс дорожки был близок к 50 Омам. Номинальная ширина другой дорожки — 0,125 мм. Это минимальная ширина дорожки для стандартных печатных плат на производстве «Резонита».

Номинальная толщина фольги — 18 мкм. Однако технологические особенности производства приводят к тому, что 18 мкм превращаются в 45 мкм на внешних слоях и в 15 мкм на внутренних. Также, на внешние слои накладывается паяльная маска толщиной 25 мкм и диэлектрической проницаемостью ε=3,5. Об этом «Резонит» упоминает отдельно. Кроме того, в результате травления сечение проводника принимает форму не прямоугольника, а трапеции.

При изготовлении печатных плат «Резонит» опирается на вычисления «Si8000». И для стандартного материала FR4 «Резонит» делает допуск на импеданс ±10%. При ширине дорожки 1,05 мм результаты вычисления импеданса калькуляторами в различных пакетах будут следующие:

Вполне объяснимо, что «Saturn PCB Design Toolkit», который не учитывает ни технологически изменённую толщину проводника, ни форму сечения дорожки, ни наличие маски, показывает несколько худший результат, чем остальные пакеты.

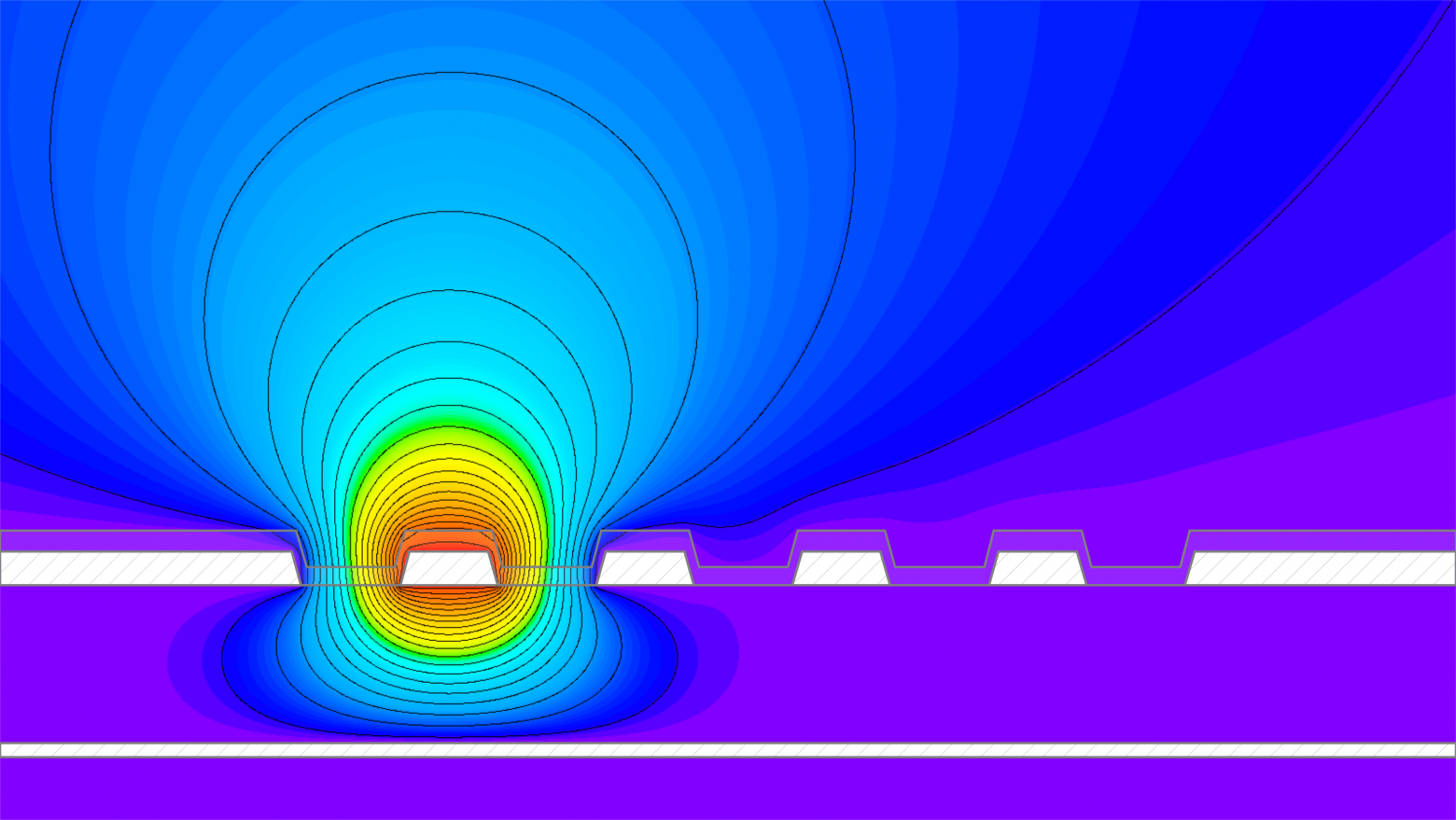

О влиянии сечения проводника и формы маски на импеданс

Для каждого случая на схеме указан номинальный импеданс и разница в процентах по сравнению с трапециевидным сечением и конформной (обтекающей поверхность) маской.

С уменьшением ширины проводника данные факторы влияют всё сильнее и на дорожке шириной 0,125 мм результаты вычислений бесплатных пакетов оказываются заметно хуже, чем у платных. Однако использование бюджетных материалов (имеющих значительный разброс геометрических и электрических параметров) и технологии производства могут сделать результаты особо точной симуляции также не слишком осмысленными.

Воспользуемся двумя пакетами («ADS» и «HyperLynx») для симуляции отражений в вышеупомянутых дорожках. Для этого необходимо экспортировать проект печатной платы из САПР. В случае использования САПР любительского уровня, вроде «Sprint Layout», с экспортом будет проблема. Классический формат печатных плат «Gerber» рассматривает топологию просто как последовательность вырезов в фольге. Симулятору же нужна информация о том, что считать началом и концом дорожки и о том, какие элементы присоединены к ней. То есть нужна библиотека элементов, схема их соединения («нетлист») и сопоставление этой схемы с топологией платы. Существует ряд форматов, которые сохраняют данную, расширенную информацию о плате (к примеру «Specctra» или «ODB++»). Подобные форматы в большинстве случаев проприетарны и потому генерируются только платными САПР. Однако, если вы используете платный симулятор, логично предположить, что и САПР для трассировки плат у вас также платный.

Отдельно следует отметить два момента. Во-первых, «ODB++» может формироваться как в виде отдельного файла, так и в виде папки. Поэтому при импорте путь может указываться именно к папке, что не совсем обычно. Во-вторых, пакеты симуляции не всегда стабильно работают с длинными путями, пробелами в названиях и кириллицей.

HyperLynx

Итак, для «HyperLynx» последовательность будет следующая. После открытия «HyperLynx SI PI Thermal» откроем проект печатной платы при помощи «File→Open ODB++». Может появиться несколько предупреждений о том, что часть топологии находится за границами платы и том, что некоторые цепи не разведены и «HyperLynx» может попробовать их провести. Пропустим эти предупреждения и откажемся от каких-либо улучшений топологии со стороны «HyperLynx». Откроется окно редактора «BoardSim», которое будет выглядеть так:

Формат «ODB++» сохраняет данные о слоях. Однако, если слои не были настроены должным образом в САПР, имеется возможность отредактировать электрические и геометрические параметры материала после экспорта непосредственно в симуляторе.

Откроем редактор слоёв.

Вкладка «Basic» будет выбрана по умолчанию.

Внесём указываемые производителем печатных плат значения диэлектрической проницаемости и толщины (в микрометрах).

Пометим тип нижнего слоя, как «Plane» — опорный слой (это потребуется в дальнейшем).

Также в этом редакторе можно отключить видимость некоторых слоёв, если большое количество дорожек на различных слоях мешает восприятию или выделению отдельных дорожек.

Настроив слои и нажав «Ok», щёлкнем правой кнопкой мыши по дорожке и в открывшемся контекстном меню выберем пункт «Select Net »<название цепи>». Если в цепи присутствуют пассивные компоненты, то выделение пройдёт сквозь них. В данном случае автоматически выделятся все три цепи: от микросхемы до резистора, между резисторами и от резистора до разъёма.

Укажем модели компонентов, подключённых к цепи и настроим их.

Для этого:

Откроем пункт главного меню «Models → Assign Models/Values by Net…»

Выберем микросхему ПЛИС — «DD1».

Откроем окно выбора модели выходного буфера.

Выберем модель, её необходимо предварительно скопировать в папку »C:\MentorGraphics\HLVX.2.10\SDD_HOME\hyperlynx64\Libs»

Выберем тип выходного буфера «max5_ttl33_io_d16» и нажмём «Ok».

После этого в окне «Assign Models» в группе «Buffer settings» появится изображение буфера и возможность выбора его типа. Выберем «Output». Затем в списке «Pins» выберем резистор R9 и установим ему номинал 0 Ом. А потом сделаем тоже самое с резистором R10.

Разъёму «XW8» (по сути, входу осциллографа) модель назначается почти также, как и микросхеме «DD1». Только в качестве модели следует выбрать уже имеющуюся в библиотеке «probes_mod.ibs», а в качестве версии входного буфера — »10pf-scope-probe». Напомню, у осциллографа MSOX4154A ёмкость входа приблизительно равна 8пф.

Закроем окно «Assign Models» и обратим внимание на небольшую проблему.

При текущей постановке задачи, симулятор будет считать, что аналогово-цифровой преобразователь осциллографа находится в отверстии на конце исследуемой дорожки. Тогда, как в реальности до него ещё 3,5 сантиметра разъёма. И ещё 0,5 сантиметра высоты разъёма SMB на плате, а также 1,0 сантиметр продолжения разъёма BNC внутри осциллографа. В отсутствие согласования мы получим приблизительно три видимых всплеска. Или, за вычетом первого фронта, 5 фронтов. На каждом из которых разница по времени между реальностью и симуляцией будет увеличиваться на 12,5% относительно длительности всплеска.

Чтобы симуляция максимально близко повторила реальность сделаем следующее. Выберем в главном меню пункт «Export → Net To → Free-Form Schematic…». Если в редакторе слоёв все слои указаны, как «Signal» и нет ни одного слоя «Plane», то «HyperLynx» выдаст предупреждение. Однако мы уже настроили нижний слой, как «Plane» — у нас всё в порядке. В открывшемся окне нажмём кнопку «Export». Появится окно редактора «LineSim», в котором выходной буфер ПЛИС будет соединён со входом осциллографа длинной цепочкой элементов «Transmission Line» (в начале которой также будет пара резисторов), имитирующих дорожку на плате.

Приблизим конец модели дорожки, который примыкает ко входу осциллографа. Выделим и удалим линию, соединяющую последний элемент «Transmission Line» со входом осциллографа. Выделим и слегка отодвинем сам вход.

Добавим в получившийся разрыв новый элемент «Transmission Line».

Дважды щёлкнем по нему и во вкладке «Transmission-Line Type» появившегося окна «Edit Transmission Line» выберем тип «Cable». Автоматически станет активна вкладка «Cables», где мы выберем «RG-174» (кабель 50-омный, как и разъёмы платы и осциллографа) и зададим длину 5 сантиметров в поле «Cable length». Нажмём «Ok».

Соединим получившийся имитатор разъёмов с дорожкой и входом осциллографа. Для этого просто наведём указатель на контакт элемента «Transmission Line», зажмём левую кнопку мыши, протянем линию до контакта другого элемента и отпустим кнопку мыши.

В принципе возможна более качественная и точная симуляция разъёмов и переходников, но для неё потребуются модели этих разъёмов.

Наконец, настроим симуляцию и запустим её.

Для этого:

В главном меню выберем пункт «Simulate SI → Run Interactive Simulation…».

Поставим переключатель «Stimulus» в положение «Per-Net/Pin» и нажмём на появившуюся кнопку «Assign…».

В окне «Assign Stimulus» нажмём кнопку «Edit Stimulus…».

В окне «Edit Stimulus» выберем тип последовательности «Custom».

Там же выберем длительность одного бита 500нс.

Нарисуем последовательность »0101».

Сохраним данную последовательность под каким-нибудь названием (например, «sequence»). Затем нажмём в окне «Edit Stimulus» кнопку «Ok».

Выберем для выходного буфера ПЛИС («DD1») в колонке «Stimulus» окна «Assign Stimulus» нашу появившуюся последовательность «sequence» и нажмём «Ok».

Установим в окне «Digital oscilloscope» (как на настоящем осциллографе) смещение по времени 100нс и деление временно́й шкалы 100нс.

Снимем галочку напротив «DD1» и оставим её у «XW8». Сейчас нам нужна только та осциллограмма, которую зафиксировал бы настоящий осциллограф.

Нажмём «Start Simulation»!

Через некоторое время «HyperLynx» отобразит осциллограмму. Её совпадение с реальностью гораздо точнее, чем в бесплатном «MicroCap».

Advanced Design System

Для начала создадим проект: «File→ New→ Workspace…». Далее возможно пойти двумя путями. Если САПР поддерживает формат «ODB++» — воспользуемся импортом: «File→ Import→ Design…», затем в поле «File type» открывшегося окна выберем «ODB++ File Format», либо «ODB++ Directory Format» и нажмём «Ok». Появится окно, предлагающее, по-сути, импортировать из «ODB++» данные о слоях. Со всем соглашаемся, нажимая «Ok».

Если САПР не поддерживает «ODB++» («Sprint Layout», например), либо импорт по каким-либо причинам произошел с ошибками, либо нам просто доступны лишь файлы топологии в формате «Gerber», то в «ADS» есть возможность сделать импорт и из них.

Как собрать проект в ADS из герберов

После создания нового проекта откроем технологические настройки через главное меню главного окна ADS: «Options → Technology → Technology Setup…»

Установим галку «Enable Units» и укажем в качестве единицы измерения миллиметры.

Установим галку «Enable Database Resolution» и нажмём «Ok».

Нажмём кнопку создания новой топологии в главном окне ADS.

В появившемся окне укажем название нашей платы и нажмём «Create Layout»

Появится окно мастера создания слоёв. Так как мы будем настраивать слои вручную чуть позже, то преждевременное создание списка слоёв нам не нужно. Выберем пункт «Custom», нажмём кнопку «Finish» и в появившемся мастере нажмём «Cancel»

Откроется окно редактора топологии, в главном меню которого мы выберем пункт «File → Import…»

В качестве типа импортируемых файлов выберем «Gerber/Drill»

Откроем диалоговое окно выбора файлов и выберем все необходимые нам: слои топологии, слои маски и файл сверловки. Здесь возможен одновременный выбор сразу нескольких файлов. Нажмём «Ok» и в редактор добавится топология.

Нажмём на кнопку редактора списка слоёв на панели инструментов (либо в главном меню «EM → Substrate…»). Так как в проекте нет ни одного списка слоёв, то появится окно создания нового списка.

В этом окне дадим название новому списку…

…выберем шаблон для нового списка и нажмём «Create Substrate»

Удалим лишний слой. Для этого в схеме слоёв (либо в таблице) нажмём правую кнопку мыши на диэлектрике и в открывшемся контекстном меню выберем «Delete With Upper Interface»

При импорте файлов топологии «ADS» для каждого из них автоматически создал название для слоя. Выберем в выпадающем списке таблицы слоёв соответствующие названия для каждого слоя фольги.

Точно также выберем в таблице отверстий название для слоя отверстий.

Установим толщину слоёв диэлектрика и фольги, не забыв про выбор единиц измерения.

Для каждого слоя фольги установим угол, задающий трапециевидности проводников.

А также зададим тип влияния проводников на вышележащий диэлектрик, как «Expand the substrate». Это потребуется для задания толщины паяльной маски.

Добавим паяльную маску. Для этого нажмём правой кнопкой мыши на самых крайних диэлектриках с типом материала «AIR» и выберем в контекстном меню «Insert Substrate Layer»

Откроем окно свойств материалов, выделив в таблице слоёв диэлектрик и нажав кнопку на правой панели (либо через пункт главного меню «Technology → Material Definition…», вкладка «Dielectrics»).

Зададим диэлектрическую проницаемость маски согласно данным производителя печатных плат. У «Резонита» это — 3,5 (в «ADS» значение по умолчанию — 3,3).

Выделим по очереди каждый слой паяльной маски и на правой панели выберем для него название из списка, сформированного по итогам импорта топологии.

Зададим для слоёв паяльной маски тип материала и толщину.

Теперь необходимо создать отдельные компоненты. Процесс создания компонентов во многом повторяет процесс создания платы: нужно нажать ту же самую кнопку в главном окне «ADS», придумать название и импортировать соответствующий файл топологии. Однако если файл топологии был создан со смещённой точкой начала координат, то для удобства дальнейшего размещения компонентов на плате имеет смысл их отцентрировать.

Для этого:

Нажмём правой кнопкой мыши по свободному пространству в редакторе топологии и выберем в контекстном меню пункт «Preferences…»

В появившемся окне на вкладке «Grid/Snap» установим удобный для нас масштаб сетки.

Выделим все контактные площадки компонента (доступно выделение по «Ctrl+A»). Нажмём правой кнопкой на любом из них и в контекстном меню выберем пункт «Create Group»

Затем перетащим компонент в начало координат.

Теперь необходимо указать, каким контактным площадкам соответствуют выводы. Для этого:

Снова выберем пункт «Preferences…» в контекстном меню. Перейдём на вкладку «Placement»

По умолчанию стрелка — символ вывода — может быть гигантского размера. Укажем размер стрелки.

У вывода имеется название и оно также может иметь гигантский для наших масштабов размер. Зададим подходящий размер на вкладке «Component/Pin Text»

Нажмём на кнопку создания нового вывода, но лучше…

…выберем в контекстном меню пункт «Pin → Create One Pin From Selection». Так расстановка выводов будет происходить чуть удобнее. В редакторе имеется возможность нажать также «Pin → Create Multiple Pins From Selection». Иногда это удобно, но редактор не всегда угадывает последовательность, в которой следует именовать выводы.

После того, как все выводы расставлены, следует выделить всё (и выводы и контактные площадки) и на панели справа выбрать название того слоя, на который предполагается в дальнейшем поместить компонент.

Аналогичным образом создадим остальные компоненты. Важный момент: редактор топологии в «ADS» — это всё же не САПР уровня «Altium Designer». И компонент в нём — это не тип с экземплярами, которым можно менять свойства в широком диапазоне. С точки зрения повторного использования, максимум возможного в редакторе — это создать, к примеру, конденсатор 0402, а затем использовать его точные копии на всей плате. Причём у таких конденсаторов будет идентично всё — и номинал и слой, на котором их можно использовать. Хотим другой слой или другой номинал — создаём новый компонент.

После создания всех необходимых компонентов, для удобства их использования, создадим в главном окне «ADS» папку.

Затем при помощи «Drag-and-Drop» перетащим все компоненты в неё.

После этого, при помощи того же «Drag-and-Drop» перетащим все компоненты на плату и расставим их по своим местам.

У интересующий нас (с точки зрения симуляции) дорожки выделим любой сегмент.

Затем на панели справа в строке свойства «Net Name» нажмём кнопку и откроем окно «Edit Net»

В этом окне установим галку напротив «Force net on selected objects»

Убедимся, что в разделе «Net operations for on selected objects» выбрана операция «Put objects on net»

Зададим какое-либо имя цепи, к примеру — «LINE_MAIN». Затем повторим всё с пункта 4 по пункт 8 для всех нужных нам цепей. Также не забудем про земляной полигон, которому желательно задать имя цепи «GND», предварительно выделив его просто щёлкнув по нему левой кнопкой мыши.

После всех этих действий проект будет столь же хорош, как и в случае его экспорта напрямую из «ODB++».

Выделим список слоёв без красной галочки на логотипе и удалим его (через нажатие правой кнопкой мыши и пункт контекстного меню, либо нажав «Delete»). Затем отредактируем параметры слоёв печатной платы. Откроем редактор слоёв, дважды щёлкнув по оставшемуся списку слоёв.

В данном случае у нас не экспортировалась паяльная маска (потому, что её не было в самом «ODB++»). Добавим материал паяльной маски.

Откроем редактор материалов «Technology → Material Definition…»

На вкладке «Dielectrics» добавим материал нажав на кнопку «Add Dielectric»

Дадим материалу маски какое-либо имя («Solder_mask», например) и отредактируем его диэлектрическую проницаемость.

Нажмём «Ok»

Добавим слои маски, щёлкнув правой кнопкой мыши по внешним слоям диэлектрика и выбрав в контекстном меню «Insert Substrate Layer»

Настроим толщину и материал каждого слоя. Для десятичных разрядов следует использовать точку. Калькулятор импеданса в редакторе слоёв поймёт и запятую, но наличие запятой приведёт в дальнейшем (при создании симуляции) к ошибке.

Выделим слой фольги.

Укажем для него «Expand the substrate». Это будет означать, что толщина вышележащего слоя диэлектрика должна быть равна сумме толщины слоя фольги и толщины, прописанной в свойствах самого слоя этого диэлектрика. Повторим данное действие для другого слоя фольги.

Укажем угол, задающий трапециевидность сечения проводника.

Сохраним всё, закроем редактор слоёв, вернёмся в главное окно «ADS» и откроем редактор топологии, дважды щёлкнув по иконке импортированной топологии.

Мы можем добавить кнопку вызова редактора симуляции на панель инструментов…

…и вызывать редактор, нажимая на эту кнопку. Или можем вызывать его из главного меню «Tools → SIPro/PIPro → Open Setup…»

Если ни одной симуляции не настроено, то появится диалоговое окно, предлагающее назвать новую симуляцию и выбрать для неё список слоёв (если у вас несколько списков слоёв, будьте внимательны, выбрав не тот список вы получите ошибочные результаты симуляции). Нажмём «Ok»

Выделим и удалим лишние, в данном случае, симуляции. Оставим только «PA-SI Analysis»

Выделим интересующие нас цепи. Можно приближать-отдалять топологию при помощи колёсика мышки и выделять цепи прямо на топологии.

Назначим выделенным цепям через контекстное меню (открытое нажатием правой кнопкой мыши) тип «Signal»

Перенесём выделенные цепи и землю в раздел «Nets» симуляции «PA-SI Analysis» при помощи «Drag-and-Drop»…

…либо при помощи пункта контекстного меню «Add to Analysis…»

Выделим три цепи в разделе «Nets» симуляции и выберем пункт контекстного меню «Create Ports or Component Model Groups…»

«ADS» предлагает внедрить резисторы R9 и R10 в дорожку в качестве компонентов, а портами дорожки назначить соответствующий контакт ПЛИСа и разъёма. Нам это подходит, нажмём «Ok» и в древе симуляции появятся два порта и компонент с двумя экземплярами.

Дважды щёлкнем в древе симуляции по компоненту, чтобы открыть окно настройки моделей.

В разделе «Model List» окна настройки моделей компонента нажмём кнопку «Add» и выберем в списке «Lumped» — сосредоточенный элемент. При необходимости можно задать значения сопротивления, индуктивности и ёмкости, но сейчас оставим в полях нули и нажмём «Done»

Запустим расчёт дорожки, нажав на символ «шестерёнка». «ADS» предложит сохранить всё, соглашаемся и ждём, пока расчёт завершится.

Наконец сгенерируем компонент дорожки, который можно будет использовать в редакторе схем. Для этого в древе симуляции в разделе «Results» дважды щёлкнем по пункту «Generate Sub Circuit…». Откроется схема компонента, закроем её, закроем редактор симуляции и перейдём в главное окно «ADS»

Нажав кнопку на панели инструментов главного окна «ADS», создадим новую схему.

Перенесём на схему сгенерированный компонент дорожки при помощи «Drag-and-Drop» прямо из главного окна «ADS».

Выделим компонент дорожки. При необходимости, развернём его нужной стороной к будущему осциллографу, используя комбинацию клавиш «Ctrl+R»

Выберем нужные нам компоненты и добавим их на схему. Компоненты можно найти либо через поиск по названию, либо поискав вручную в соответствующих палитрах — как в «MicroCap». Нам потребуются: источник прямоугольных импульсов «VtPulse» и источник постоянного напряжения «V_DC» из палитры «Source-Time Domain»; буфер «IBIS_IO» (именно «IBIS_IO», а не «IBIS_O», иначе из модели подтянется только выход «TDO» — единственный чистый выход) из палитры «Signal Integriny-IBIS»; длинная линия (имитатор разъёмов) — «TLINP» из палитры «Tlines-Ideal»; резисторы и конденсатор (для имитации входной ёмкости осциллографа) из палитры «Basic Components» и настройка симуляции переходного процесса «Tran» из той же палитры.

Откроем окно редактирования параметров компонента, дважды щёлкнув на схеме по имитатору разъёмов.

По умолчанию импеданс «TLINP» равен 50 Омам. Так что установим только длину (50 мм) и диэлектрическую проницаемость диэлектрика (для RG-174 — это полиэтилен, 2,3) — величины, влияющие на время прохождения сигнала.

Откроем параметры симуляции переходного процесса и установим время симуляции 1000нс и максимальный шаг симуляции 0,1нс.

Откроем параметры источника прямоугольных импульсов и установим напряжения логических уровней в 0,0В и 3,3В, длительность переднего и заднего фронтов в 0,1нс, ширину импульса в 500нс, период — в 1000нс и задержку перед первым импульсом — 100нс.

Откроем параметры буфера и укажем путь к модели «IBIS».

На вкладке «Pin» выберем модель выхода «max5_ttl33_io_d16»

Добавим зе́мли и соединим все элементы линиями.

Выберем линию, выходящую из имитатора разъёма.

Дадим ей какое-либо имя, например «oscilloscope»

Запустим симуляцию.

Через некоторое время симуляция завершится и автоматически откроется редактор графиков.

В редакторе графиков на палитре инструментов нажмём на прямоугольный график. Курсор превратится в прямоугольник с габаритами будущего графика. Щёлкнем им по полю, откроется редактор свойств графика.

В редакторе выберем названный нами ранее вход осциллографа — «oscilloscope»

Добавим его в список линий графика…

…нажмём «Ok» и посмотрим на него!

После того, как мы сохраним график, он появится в древе объектов проекта главного окна «ADS» и будет доступен для просмотра.

Данный график также совпадает с реальностью достаточно хорошо.

Итак, можно просимулировать любую печатную плату. А затем в несколько итераций внести изменения, сводящие все негативные электромагнитные явления к разумному минимуму. Однако, чтобы изменения были осмысленны, а количество итераций — минимально, есть смысл уделить внимание наиболее типичным потенциальным источникам нарушения целостности сигналов. К примеру — переходным отверстиям. Но о них — в другой раз.

Выражаю большую благодарность за демоверсии пакетов:

HyperLynx: АО «Нанософт»

ELCUT: ООО «Тор»

ADS: московскому подразделению «Keysight» и лично Сергею Баранчикову за невероятно детальную техническую поддержку!