Метастабильность триггера и межтактовая синхронизация

Удивительный факт, но многие студенты, успешно прошедшие курс цифровой электроники, остаются в неведении о таком явлении, как метастабильность (либо считают его столь малозначимым, что примерно через 2 дня после экзамена напрочь забывают). Между тем, сбои в работе устройства, вызванные метастабильностью диагностируются крайне трудно. Если вы узнали себя в таком студенте, и если вы хоть как-то связаны с разработками на базе цифровых микросхем — крайне рекомендую к прочтению данный текст. Возможно, что потратив 10 минут сейчас вы сэкономите многие дни, проведенные за отладкой в будущем. Вспомнить бы что такое триггерКлассический D-триггер является базовой единицей хранения информации в современных цифровых микросхемах. На высоком уровне абстракции он представляет из себя устройство памяти с входом данных D, выходом данных Q, а также входным управляющим тактовым сигналом (clk — clock в английской терминологии). Все сигналы здесь — логические, могут пребывать либо в логическом 0 (далее »0») либо в логической 1 (далее »1»). Абсолютное значение напряжений в вольтах нас пока не интересует. При поступлении на тактовый вход фронта сигнала, т.е. перехода из »0» в »1», триггер запоминает текущее значение на входе данных D и передает его на выход Q. Во всех прочих ситуациях триггер продолжает хранить свое старое значение. Также у триггера могут присутствовать и другие управляющие сигналы, в частности сигнал асинхронного сброса aclr, устанавливающий триггер в »0», невзирая на другие входы.

Вспомнить бы что такое триггерКлассический D-триггер является базовой единицей хранения информации в современных цифровых микросхемах. На высоком уровне абстракции он представляет из себя устройство памяти с входом данных D, выходом данных Q, а также входным управляющим тактовым сигналом (clk — clock в английской терминологии). Все сигналы здесь — логические, могут пребывать либо в логическом 0 (далее »0») либо в логической 1 (далее »1»). Абсолютное значение напряжений в вольтах нас пока не интересует. При поступлении на тактовый вход фронта сигнала, т.е. перехода из »0» в »1», триггер запоминает текущее значение на входе данных D и передает его на выход Q. Во всех прочих ситуациях триггер продолжает хранить свое старое значение. Также у триггера могут присутствовать и другие управляющие сигналы, в частности сигнал асинхронного сброса aclr, устанавливающий триггер в »0», невзирая на другие входы. Любой триггер имеет два временны́х параметра (требования), которые необходимо выполнять для корректной работы:

Любой триггер имеет два временны́х параметра (требования), которые необходимо выполнять для корректной работы:

Ts — setup time — время предустановки. Время в течение которого сигнал на входе D должен оставаться стабильным перед приходом фронта тактового сигнала;

Th — hold time — время удержания. Время в течение которого сигнал на входе D должен оставаться стабильным после прихода фронта тактового сигнала;

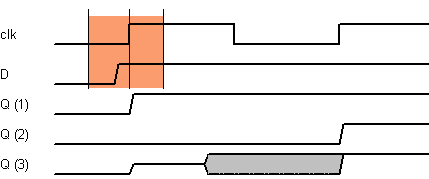

Сумма этих двух параметров дает нам временно́е окно в окрестностях фронта тактового сигнала в течение которого входные данные должны быть стабильны. Аналогичные параметры есть и для других входов, в частности для входа асинхронного сброса (их называют recovery and removal time). Невыполнение данных требований приводит к неопределенному состоянию триггера. В простейшем случае это будет либо «старое» либо «новое» значение пришедшее на вход данных D в непосредственной близости от фронта клока, но какое именно — неизвестно. Во многих ситуациях с этим можно смириться. На следующей картинке выходы Q (1) и Q (2) — две реализации срабатывания триггера при нарушении входных временных параметров.

Сумма этих двух параметров дает нам временно́е окно в окрестностях фронта тактового сигнала в течение которого входные данные должны быть стабильны. Аналогичные параметры есть и для других входов, в частности для входа асинхронного сброса (их называют recovery and removal time). Невыполнение данных требований приводит к неопределенному состоянию триггера. В простейшем случае это будет либо «старое» либо «новое» значение пришедшее на вход данных D в непосредственной близости от фронта клока, но какое именно — неизвестно. Во многих ситуациях с этим можно смириться. На следующей картинке выходы Q (1) и Q (2) — две реализации срабатывания триггера при нарушении входных временных параметров. Монета, зависшая в воздухе

Однако иногда при нарушении временных параметров происходит выход за границы «цифрового мира» и вместо того, чтобы принять состояние четко соответствующее »0» или »1», выход триггера начинает болтаться в промежуточном состоянии с напряжением примерно соответствующим половине напряжения между »0» и »1». Грубая аналогия из «механического мира» вынесена в заголовочную картинку. В стабильном положении шарик находится слева или справа. Чтобы он попал в другое состояние — его нужно толкнуть. Если сделать это достаточно сильно — он без проблем перевалит за вершину и очутится с другой стороны (нормальное переключение триггера). Если толкнуть слишком слабо — сразу скатится назад. Если же вы человек везучий, то есть шанс, что толкнув шарик, вы заставите его застыть ровно на вершине.Именно этот эффект и называется метастабильностью. На картинке выше этот вариант обозначен как Q (3). В конечном итоге триггер «свалится» в одно из определенных состояний, но точно сказать когда это произойдет невозможно. Время пребывания триггера в метастабильном состоянии является вероятностной величиной и зависит от технологических параметров элементной базы, температуры и т.п. На осциллографе эта картина выглядит примерно вот так (синим цветом показан входной сигнал, нарушающий временные параметры триггера, розовым — выход триггера):

Монета, зависшая в воздухе

Однако иногда при нарушении временных параметров происходит выход за границы «цифрового мира» и вместо того, чтобы принять состояние четко соответствующее »0» или »1», выход триггера начинает болтаться в промежуточном состоянии с напряжением примерно соответствующим половине напряжения между »0» и »1». Грубая аналогия из «механического мира» вынесена в заголовочную картинку. В стабильном положении шарик находится слева или справа. Чтобы он попал в другое состояние — его нужно толкнуть. Если сделать это достаточно сильно — он без проблем перевалит за вершину и очутится с другой стороны (нормальное переключение триггера). Если толкнуть слишком слабо — сразу скатится назад. Если же вы человек везучий, то есть шанс, что толкнув шарик, вы заставите его застыть ровно на вершине.Именно этот эффект и называется метастабильностью. На картинке выше этот вариант обозначен как Q (3). В конечном итоге триггер «свалится» в одно из определенных состояний, но точно сказать когда это произойдет невозможно. Время пребывания триггера в метастабильном состоянии является вероятностной величиной и зависит от технологических параметров элементной базы, температуры и т.п. На осциллографе эта картина выглядит примерно вот так (синим цветом показан входной сигнал, нарушающий временные параметры триггера, розовым — выход триггера):

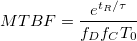

Почему метастабильность — это плохо? Во-первых, это состояние само по себе неопределенно и порождает неизвестный результат в последующих элементах. Более того, во многих случаях выходной сигнал одного триггера подается сразу на несколько других элементов, которые из-за неидеальности технологической базы могут иметь немного разные пороги срабатывания. А значит, один и тот же сигнал может трактоваться как »1» в одном месте и как »0» в другом. Это может привести к рассинхронизации работы различных частей устройства и общему сбою (т.е. такой ситуации из которой устройство само выйти неспособно). Более того, если метастабильное состояние продержалось до прихода следующего тактового сигнала, то оно может ввести следующий в цепочке триггер так же в метастабильное состояние. Вероятность этого невысока, т.к. диапазон входных напряжений при котором триггер попадает в метастабильность чрезвычайно узкий. Однако с учетом того, что подобная ситуация будет происходить регулярно с высокой частотой (современные схемы могут работать на частотах до 1 ГГц, а то и выше) это событие вполне реально. Опять таки, вероятность такого события можно оценить с учетом параметров устройства, частоты тактирования и частоты изменения данных. Общая формула оценки времени наработки на отказ выглядит следующим образом:  , гдеt_R — временной интервал «защиты» от метастабильности. Для грубой оценки можно считать, что равен 0 для одного триггера, периоду тактового сигнала за вычетом задержек на предустановку и распространение для второго триггера и плюс по периоду для каждого последующего;\tau — параметр зависящий от технологии, для современных устройств единицы/десятки пикосекунд; T_0 — временное окно попадания в метастабильность. Десятки/сотни пикосекунд; f_c — частота тактового сигнала. Сотни мегагерц; f_D — частота изменения данных. В диапазоне от 0 до f_c. Для современной аппаратуры период попадания первого триггера в цепочке в метастабильное состояние измеряется микро/миллисекундами, второго — часами, третьего — миллиардами-триллионами лет.

, гдеt_R — временной интервал «защиты» от метастабильности. Для грубой оценки можно считать, что равен 0 для одного триггера, периоду тактового сигнала за вычетом задержек на предустановку и распространение для второго триггера и плюс по периоду для каждого последующего;\tau — параметр зависящий от технологии, для современных устройств единицы/десятки пикосекунд; T_0 — временное окно попадания в метастабильность. Десятки/сотни пикосекунд; f_c — частота тактового сигнала. Сотни мегагерц; f_D — частота изменения данных. В диапазоне от 0 до f_c. Для современной аппаратуры период попадания первого триггера в цепочке в метастабильное состояние измеряется микро/миллисекундами, второго — часами, третьего — миллиардами-триллионами лет.

Эффект метастабильности может возникнуть в нескольких классических ситуациях:

Явное нарушение параметров Ts и Th триггера. Обычно возникает, когда устройство пытаются заставить работать на частоте, на которой оно физически работать не может из-за слишком длинных путей распространения сигналов. Данная ситуация контролируется временным анализатором и при нормальной работе (при выполнении временных требований) встречаться не должна.

Нарушение временных параметров по входам асинхронного сброса. Удивительно, но несмотря на то, что сброс асинхронный, он должен быть синхронен тактовому сигналу того триггера, который сбрасывает, т.е. его временные параметры декларируются относительно фронта тактового импульса. Об этом часто забывают, подавая сброс откуда ни попадя. Опять-таки, если сигнал сброса порожден с помощью того же тактового сигнала, как и тактовый сигнал сбрасываемого триггера, то временной анализатор разберется самостоятельно.

Сигналы, подаваемые синхронно (на той же частоте с известной задержкой) из других устройств — здесь простейший временной анализ (т.е. декларирование только тактовой частоты) не работает и необходимо явно задавать временные характеристики ваших входных/выходных сигналов. Это является отдельной непростой (но вполне разрешимой) задачей временного анализа.

И, наконец, самый тяжелый случай — сигналы передаются асинхронно, может быть совсем на другой тактовой частоте (и с неизвестными сдвигами фазы) относительно приемных триггеров. Их источником может быть как внешнее оборудование (хоть кнопка на плате или последовательный порт) так и блоки той же микросхемы, работающие на другой тактовой частоте. Именно об этой ситуации и пойдет дальнейший разговор.

Но сперва несколько слов о том, откуда же берется множество тактовых сигналов. Безусловно, самый простой и приятный вариант — когда тактовый сигнал только один. Тогда работать с проектом просто и удобно. К сожалению это возможно лишь для совсем простых устройств. Любое более-менее сложное устройство обычно общается с несколькими внешними устройствами/интерфейсами, каждый из которых может иметь свой собственный тактовый сигнал. К примеру, нам надо принять данные с АЦП, буферизировать их во внешней динамической памяти после чего передать по Ethernet. В этом случае у нас будет как минимум 3 несвязанных друг с другом тактовых домена — интерфейса АЦП, системной шины и DDR-памяти, а так же клок Ethernet-интерфейса. А значит перед нами стоит задача корректно передавать данные (а так же параметры, управляющие сигналы, флаги статуса и т.п.) между этими тактовыми доменами.

Но сперва несколько слов о том, откуда же берется множество тактовых сигналов. Безусловно, самый простой и приятный вариант — когда тактовый сигнал только один. Тогда работать с проектом просто и удобно. К сожалению это возможно лишь для совсем простых устройств. Любое более-менее сложное устройство обычно общается с несколькими внешними устройствами/интерфейсами, каждый из которых может иметь свой собственный тактовый сигнал. К примеру, нам надо принять данные с АЦП, буферизировать их во внешней динамической памяти после чего передать по Ethernet. В этом случае у нас будет как минимум 3 несвязанных друг с другом тактовых домена — интерфейса АЦП, системной шины и DDR-памяти, а так же клок Ethernet-интерфейса. А значит перед нами стоит задача корректно передавать данные (а так же параметры, управляющие сигналы, флаги статуса и т.п.) между этими тактовыми доменами.

Как бороться

Для начала плохая новость: полностью эффект метастабильности побороть невозможно, поэтому всегда остается вероятность того, что ближайшая АЭС внезапно взорвется или ваш самолет внезапно упадет. Однако рядом простых действий можно данную вероятность значительно уменьшить, примерно сравняв с вероятностью того, что завтра вострубит архангел Рафаил и объявит Судный День. Общая тактика понятна: ставим подряд несколько триггеров (как показывает формула выше, для реалистов вполне достаточно двух синхронизирующих триггеров) после чего данными можно пользоваться. Однако есть ряд технических нюансов, которые зависят от рода передаваемых данных.Самый простой случай — передается псевдостатический скалярный (одноразрядный) сигнал. Например сигнал выбора режима и т.п. — переключающийся крайне редко. В этом случае нашей единственной заботой является защита от метастабильности — ставим два триггера приемной частоты и дело в шляпе. С неопределенностью 1 такт (нас не волнующей) он будет передан от источника к приемнику.

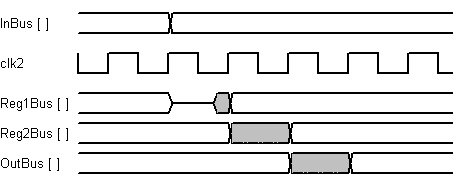

Сигнал разрешения длительностью 1 такт. Сложность заключается в том, что при несовпадении частот есть высокая вероятность либо совсем потерять сигнал (если приемная частота ниже исходной) либо растянуть его на несколько тактов, что тоже не здорово. Общий подход, применяемый в этом случае — «удлинить» сигнал не несколько тактов, перенести его в новый тактовый домен известным способом и там выделить событие фронта, заново сформировав сигнал длительность 1 такт.

Общий подход, применяемый в этом случае — «удлинить» сигнал не несколько тактов, перенести его в новый тактовый домен известным способом и там выделить событие фронта, заново сформировав сигнал длительность 1 такт.

Многоразрядная шина, передающая единое псевдостатическое значение (например конфигурационный параметр). Казалось бы, все просто — ставь по паре триггеров на каждый разряд шины — что еще надо? Однако нам известно, что после выхода из метастабильного состояния триггер может принять как старое, так и новое значение. Более того, даже без входа в метастабильность, просто за счет чуть отличающихся параметров триггер одного из разрядов может успеть защелкнуть новое значение, а триггер другого — старое. В данном случае в течение как минимум 1 такта на выходе шины будет присутствовать некорректное значение. Оно не будет равно ни старому, ни новому из поданных на вход. Для каких-то схем это может не иметь значения, а для каких-то может быть важно. Поэтому стараются создать более надежную схему с сигналом-подтверждением, указывающим в какой момент можно безопасно перещелкнуть входные данные на выход.

В данном случае в течение как минимум 1 такта на выходе шины будет присутствовать некорректное значение. Оно не будет равно ни старому, ни новому из поданных на вход. Для каких-то схем это может не иметь значения, а для каких-то может быть важно. Поэтому стараются создать более надежную схему с сигналом-подтверждением, указывающим в какой момент можно безопасно перещелкнуть входные данные на выход.

И, наконец, самый сложный случай — поток данных, передающихся из одного тактового домена в другой. Если данные относительно редкие (1 слово данных на 10 и более тактов клока), то можно реализовать схему с рукопожатием, аналогичную предыдущему пункту. Но как быть, если данные идут на каждом такте (или близко к тому)? Здесь нам на помощь придет специальный аппаратный блок — двухпортовая память с независимыми тактовыми сигналами. Такая память есть как в современных FPGA, так и в технологических библиотеках для заказных микросхем. Ее можно писать и читать совершенно независимо через два отдельных порта. Единственным ограничением является одновременное обращение на запись и чтение по одному и тому же адресу памяти — оно может привести к неопределенному результату. На основе такого блока памяти зачастую создается модуль FIFO, который позволяет с одной стороны записывать данные из одного тактового домена, а с другой — забирать в другой тактовый домен. Заодно логика FIFO следит за тем, чтобы не происходило обращения к одной и той же ячейке памяти.

Заключение Напоследок хочется подвести итог и дать несколько полезных советов: Чем меньше тактовых сигналов, тем проще работа с вашим проектом Базовым сихронизатором является два (или более) стоящих друг за другом триггера Между всеми асинхронными тактовыми доменами должен быть продуман механизм передачи данных. Лучше всего еще на этапе системного проектирования нарисовать тактовую структуру проекта Все внешние сигналы, асинхронные по отношению к вашему устройству, в том числе сигналы асинхронного сброса, должны быть синхронизированы Внутри одного модуля лучше использовать только один клок Если внутри модуля больше одного клока, то для каждого внутреннего сигнала нужно четко представлять, каким клоком он формируется и как потом используется. Надежнее закодировать прямо в имени сигнала Будьте особо внимательны на верхнем уровне проекта: именно здесь очень часто происходит ошибочное подключение сигнала из одного тактового домена в другой без пересинхронизации Тактовые сигналы, порожденные на внутренних модулях умножения частот (PLL/DCM/MMCM и т.п.) обычно синхронны, они рассматриваются временным анализатором и для них пересинхронизация данных чаще всего не требуется. Хотя и не помешает. Современные средства проектирования стараются самостоятельно обнаруживать ситуации передачи данных между тактовыми доменами. Например Design Assistant у Альтеры (встроен в Quartus), ALINT у Aldec. Стоит прислушиваться к выдаваемым предупреждениям и советам И в завершение несколько комментариев по возможным техническим вопросам.Временные диаграммы рисовались с помощью простой бесплатной программы TimingEditor. Некоторые проекты собирались в Quartus — исключительно из-за удобства его схемного редактора. Все то же самое может быть (и должно быть!) реализовано на чистом HDL (VHDL/Verilog). Если хочется более глубокого понимания физики метастабильности, то подробнее данную тематику можно изучить по ключевым словам metastability и clock domain crossing. Например, довольно подробное исследование Steve Golson «Synchronization and Metastability» и более краткий документ Ran Ginosar «Metastability and Synchronizers», а так же многие другие доступны в интернете.

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.