Логисторная логика

Логисторная логика это набор концепций, применение которых может позволить ускорить вычисления, сократить затраты энергии на вычисления и увеличить плотность транзисторов на кристалле без существенного изменения техпроцесса. Она находится в разработке и статья ниже является лишь первичным результатом. Мы надеемся что она вызовет интерес в научных кругах и среди энтузиастов и разработка будет продолжена.

Логисторная логика предполагает:

Параллельно — последовательное, а не последовательное как в CMOS, выполнение операций на уровне логических элементов (альтернатива CMOS)

Не стандартный метод кодирования 0 и 1

Использование Логисторов (тип транзисторов)

Использование двуполярного питания

Использование «grid array» расположения гейтов (вертикально и горизонтально на виде сверху)

В процессорах математические операции описываются логическими схемами, которые представлены последовательным подключением CMOS транзисторных сборок.

Время выполнения этих операций определяется суммой времен выполнения каждой из последовательно подключенных транзисторных CMOS сборок

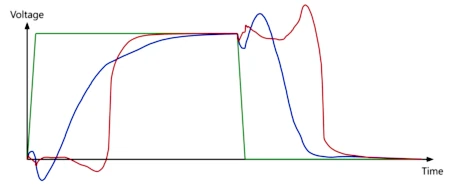

Чтобы продемонстрировать задержки, возникающие при последовательном подключении CMOS сборок представим симуляцию, выполненную в LTSpice на основе реальных spice моделей 10нм FinFET:

На графике ниже виден исходный сигнал (зеленый) и задержки, возникающие после двух (синий) и после 4-х инверторов (красный)

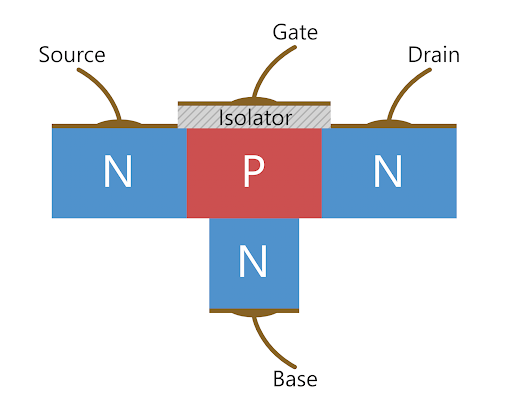

Предлагается новый тип транзистора — логистор:

В логисторе выходной сигнал (между Source и Drain) «изолирован» от управляющего сигнала — между Gate и Base, соответственно логисторы могут также использоваться вместо оптронов

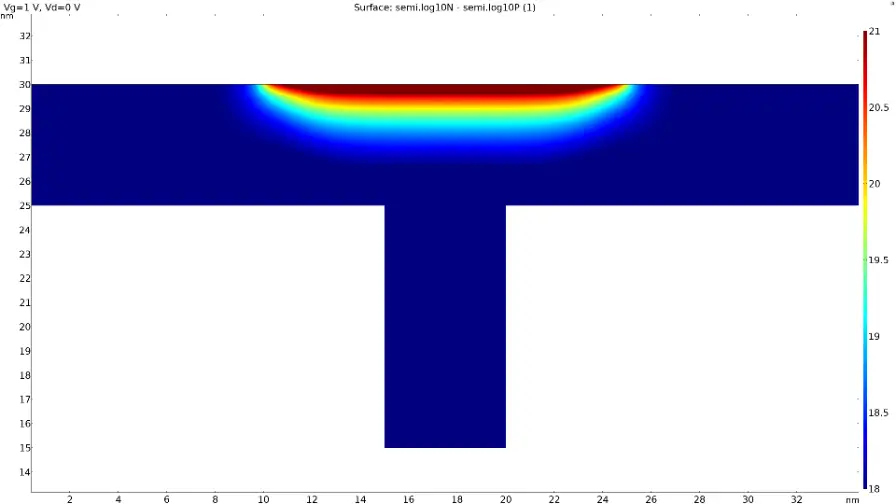

В comsol semiconductor была произведена симуляция логистора, которая показала возникновение канала между Source и Drain при подаче положительного напряжения на Gate и отрицательного на Base. Ниже показан канал при отсутствии и наличии напряжения между Source и Drain:

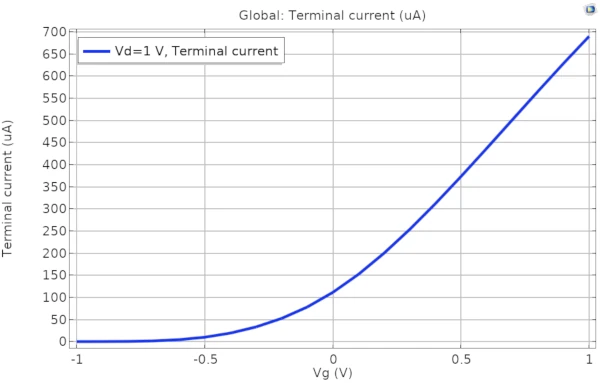

Расчетная Вольт-Амперная характеристика логистора:

Благодаря двуполярному питанию, которое будет описано ниже, не требуется обеспечивать полное «запирание» логистора при закороченных Gate и Base, благодаря чему возможен подбор профиля допинга при котором логистор «качественнее» запирается и позволяет пропускать втрое большие токи чем NMOS при прочих равных.

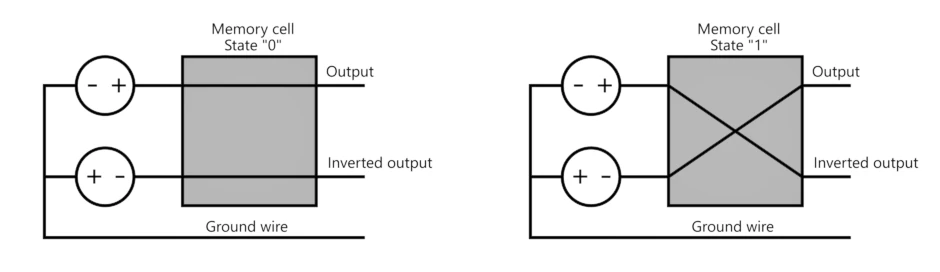

Входные значения в ALU, построенном на базе логисторной логики должны иметь ниже описанный метод кодирования 0 и 1:

Где выходное значение — это напряжение между выходами и землей. Как видно, каждый бит передается по двум проводам.

Единичные логические операции в логисторной логике принципиально описываются следующим образом:

Где «результат» — наличие (1) или отсутствие (0) пути

В логисторной логике логические цепи отличны от CMOS, TTL и других технологий. В случае отсутствия ограничения степени параллельности (в «полной» логисторной логике) цепи строятся таким образом, чтобы при выполнении операции не возникало «to Gate» операций. Другими словами в ALU запрещена подача сигнала с Drain на Gate.

В результате операции выполняются параллельно, а не последовательно как у CMOS

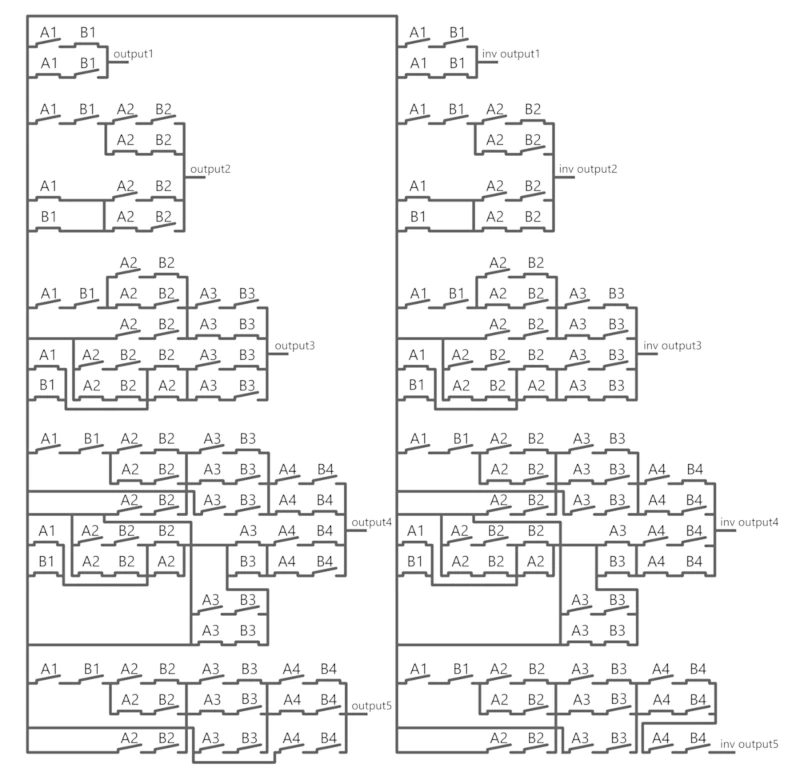

Пример построения «полной» логисторной схемы для сумматора двух 4-х битных чисел

A1, A2, A3, A4; B1, B2, B3, B4 — биты первого и второго числа; outputs — результат

Инвертированные входы представлены как проводящие ключи, не инвертированные — не проводящие

В логисторной логике формат выхода не регламентирован и может не совпадать с форматом входа, поэтому правая часть (комплиментарная) не обязательна и приведена для понимания метода составления комплиментарных схем.

В полной логисторной логике каждый выход должен иметь независимую логическую схему.

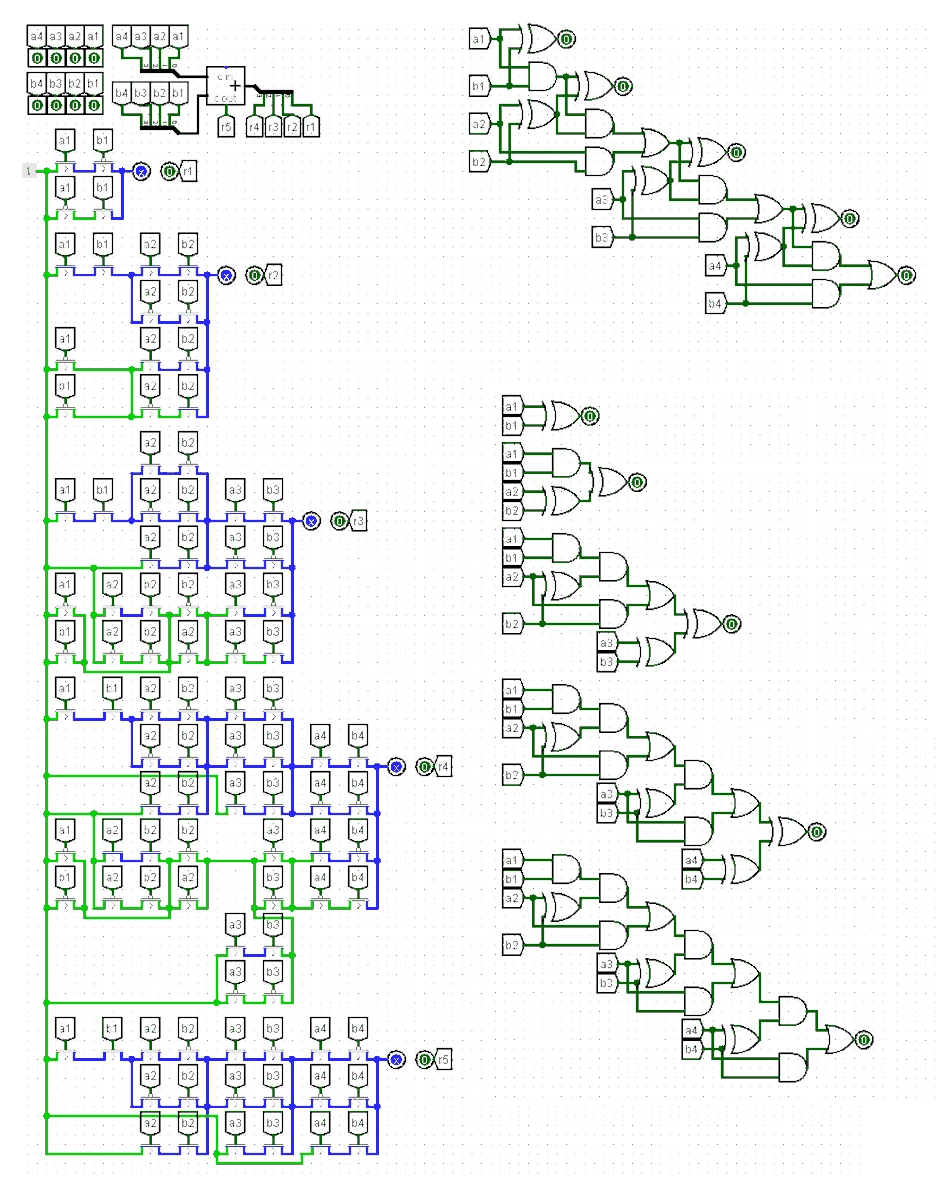

Ниже представлена симуляция в Logisim без комплиментарной части. справа сверху — стандартная схема сумматора; справа снизу — схема необходимая для построения полных логисторных схем

Далее представлена симуляция логисторного сумматора двух 3-х битных чисел в falstad:

Для подтверждения работоспособности логической части логисторной логики была запроектирована в EasyEDA и изготовлена на JLCPcb плата:

Виду того что логисторы не существуют, были использованы оптроны. Плата работает и выдает ожидаемые значения, что неопровержимо доказывает верность логической части логисторной логики.

Для достижения высокой плотности размещения логисторов рекомендуется объединить Base всех логисторов и разместить Base на обратной стороне Substrate. Gates рекомендуется располагать горизонтально и вертикально. Source и Drain соседних Логисторов необходимо объединять, так что к одному Source / Drain будут присоединяться 4 Gate

Стоит обратить особое внимание на то что в статье описана логисторная логика без ограничения степени параллельности (полная), где степень параллельности — примерное количество Gates которое может запитываться с одного Drain. Для увеличения производительности обязательно использование ограничения степени параллельности. При этом исчезает требование — использовать независимую схему для каждого выходного бита. Использование каскадирования перед логисторной логикой для увеличения токов для насыщения большого количества Gates — является очевидным, но наихудшим решением

По техническим причинам коллектив далее не может продолжать работу над проектом и описать оптимальное решение внедрения ограничения степени параллельности, а также не обладает ресурсами для реализации чипа на базе логисторной логики, поэтому материал передаются в доработку научному сообществу и энтузиастам

Разработано в ЛНМО; Авторы: Артем Родичкин, Анна Евсеева, Полина Маслова, Семен Архипов, Инна Миронова, Чечулин Михаил