Cхема > плата > ПЛИС

На Хабре есть статьи для начинающих ПЛИСоводов, есть статьи с обзорами средств трассировки печатных плат. На некоторые из них я уже ссылался в своей первой статье о создании печатных плат. Во второй статье про SimBank в комментариях у меня состоялся диалог о сложности разработки ПЛИС и поддержки проектов с ней. Было высказано мнение, что легче собрать несколько простых устройств вместо одного сложного. Иногда так действительно проще. Когда речь идёт о двух, четырёх, восьми устройствах. Ряд можно продолжать с привычной вам кратностью. До преодоления порога комфорта. Два — это куча? А что делать, если есть желающие на 100 или 200 однотипных устройств? Использовать или не использовать ПЛИС в той или другой задаче каждый решает сам (или с коллегами).Сегодня хочу предложить вашему вниманию статью об особенностях создания печатной платы с ПЛИС. За основу возьмём инструмент «IO Designer» от компании Mentor Graphics. Кому-то может материал оказаться полезным, кому-то просто интересным, а кто-то может и не согласиться со мной.Для некоторых САПР, например Altium Designer, периодически выходят обновления с базами новых микросхем. (Если вы являетесь подписчиком на обновления). Для Cadence и OrCAD часто производители компонентов выкладывают библиотечные элементы схемных символов и ячеек для печатных плат. Для ExpeditionPCB от Mentor Graphics такая роскошь скорее исключение, чем правило. Про PADS (ещё один продукт для сквозного проектирования печатных плат от Mentor Graphics) не скажу, мне не приходилось с ним работать. В самой системе проектирования очень удобный менеджер библиотечных компонентов. Для построения посадочных мест компонентов для печатных плат в соответствии с требованиями стандарта IPC-7351 есть очень удачная программа «LP Wizzard». (Land pattern wizzard). Для создания графических схемных символов простых и не очень компонентов есть возможность импорта из файла. А для ПЛИС существует «IO Designer», который объединяет в себе символьную, схемную, платную (от печатной платы) и Verilog (VHDL) части проекта.IO Designer содержит базу знаний о большинстве FPGA и CPLD таких производителей ПЛИС как Xilinx, Altera, Lattice и Acctel. Вместе с выходом новых семейств у производителей ПЛИС MG выпускает обновления к базам ПЛИС. Но новую документацию на семейства микросхем всё равно придётся изучать.Допустим мы выбрали ПЛИС, изучили (ознакомились) её особенности и готовы творить.При создании проекта мы можем выбрать производителя ПЛИС, семейство ПЛИС, тип корпуса, и количество элементов. А так же указать скорость компонентов (для задания точного Part Number). У ПЛИС большинство контактов могут конфигурироваться, как на выход, так и на вход. На первый взгляд подсоединяй — не хочу. Сюда мы выведем контроллер SD карт, сюда RGMII для Ethernet PHY и т. д. Не тут-то было. При таком смелом обходе контактов по удобству мы можем наткнутся на массу подводных камней. Чтение документации позволит большинство из них избежать, но легче назначать контакты от этого не станет. И проект платы может превратится в сплошную кашу.

У ПЛИС большинство контактов могут конфигурироваться, как на выход, так и на вход. На первый взгляд подсоединяй — не хочу. Сюда мы выведем контроллер SD карт, сюда RGMII для Ethernet PHY и т. д. Не тут-то было. При таком смелом обходе контактов по удобству мы можем наткнутся на массу подводных камней. Чтение документации позволит большинство из них избежать, но легче назначать контакты от этого не станет. И проект платы может превратится в сплошную кашу. На данном изображении всё не так уж и плохо, потому что оно создано «искусственно» на основе проработанного проекта. Обычно с первого раза всё не так гладко. И на этапе добавления ПЛИС еще не все элементы расставлены на плате. Но специально отмечено, что сигналы с левого нижнего разъёма приходят не на самый нижний угол ПЛИС. В результате они пересекаются с с другими сигналами и при трассировке могут потребовать как дополнительных переходных отверстий, так и дополнительных слоёв платы. Что в итоге увеличит стоимость производства.Возможности настройки контактов также бывают очень ограничены. Хорошо если у нас плата создаётся под одно конкретное изделие. Есть выводы смежных элементов, создаём для них ответные шины/сигналы в ПЛИС. Запустили пробный проект в САПР для ПЛИС. Если всё удалось, то можно отдавать на трассировку.

На данном изображении всё не так уж и плохо, потому что оно создано «искусственно» на основе проработанного проекта. Обычно с первого раза всё не так гладко. И на этапе добавления ПЛИС еще не все элементы расставлены на плате. Но специально отмечено, что сигналы с левого нижнего разъёма приходят не на самый нижний угол ПЛИС. В результате они пересекаются с с другими сигналами и при трассировке могут потребовать как дополнительных переходных отверстий, так и дополнительных слоёв платы. Что в итоге увеличит стоимость производства.Возможности настройки контактов также бывают очень ограничены. Хорошо если у нас плата создаётся под одно конкретное изделие. Есть выводы смежных элементов, создаём для них ответные шины/сигналы в ПЛИС. Запустили пробный проект в САПР для ПЛИС. Если всё удалось, то можно отдавать на трассировку.

В качестве отступления: ЕМНИП на Xilinx Spartan-6 были специально назначенные выводы для память DDR которые потом удобно трассировались при правильном взаимном размещении микросхем на плате. И не было необходимости их потом перемещать менять местами.

Часто по ТЗ необходимо завести некую универсальность и наша плата в дальнейшем будет использоваться для нескольких проектов. У нас так проектируется центральная плата с процессором для работы со многими другими устройствами, своеобразная отладочная плата с ПЛИС, процессором и ОС «для своих». И тут нужно многое предусмотреть.Оставить, если нужен на разъёме один контакт для подачи синхронизации, или для вывода сигнала из PLL. Определится с направлениями сигналов на шине: вход, выход или двунаправленные. Если у нас центральная плата всегда мастер, то такие сигналы к шине адреса или управляющие можно сделать только на выход.Если у нас на шине есть ответ от ведомой платы типа WAIT или BUSY, то на мастер плате можно их можно назначить на выводы способные быть только входами. Также можно поступить с выводами определяющими присутствие платы.Такое предназначение, на первый взгляд, ограничивает возможности для последующей трассировки и перетасовки сигналов. Но как показывает практика, лучше такие ограничения знать заранее. А не просто назначать всем сигналам «Inout».

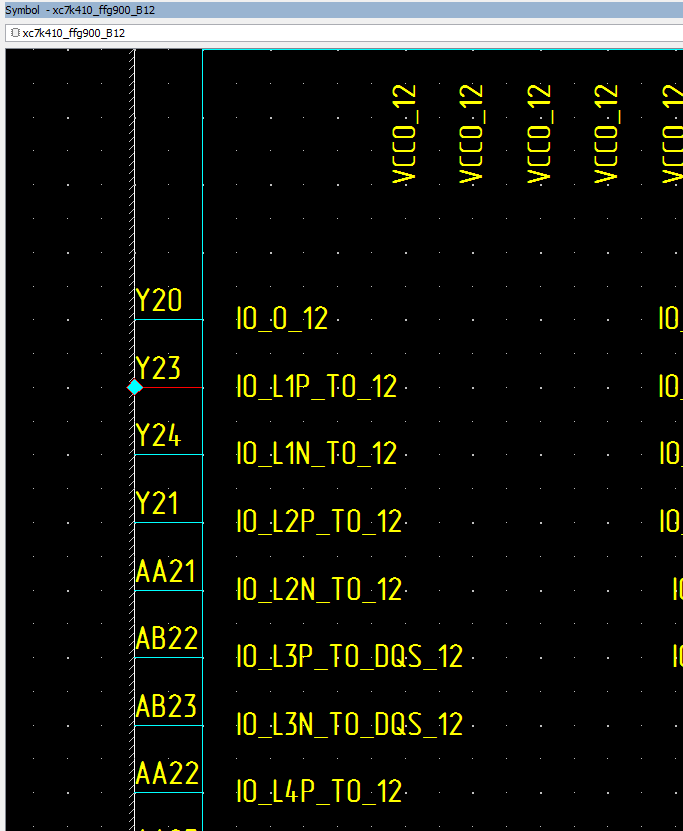

Мы можем выбрать файл откуда черпать список сигналов. Это может быть пробный проект, файл на Verilog или VHDL. Если пробный проект еще не делался, то мы можем не задавать такой файл. А потом просто создать сигналы в окне программы. Типы сигналов по умолчанию. Для одиночных сигналов и для дифференциальных.Далее мы можем назначить место куда мы потом будем выкладывать файл с нашим размещением контактов.Затем нужно определиться как мы хотим работать со схемой, нужны ли нам полноценные символы или достаточно только создания цепей в схемном проекте, а описания всех контактов у нас будут передаваться только в виде обменного фала с САПР ПЛИС.Мне всегда нравился вариант когда не нужно создавать схемных элементов, а все обмены идут через внутренние неведомые пути. Но, работая в коллективе, приходится принимать более приземлённые правила игры. Так, согласно корпоративному стандарту оформления схем мне всегда нужно было делить символ по банкам, выносить отдельно цепи конфигурации, земли, питания и прочие. Есть в таком разделении плюсы, но есть и минусы. Схемный символ приходилось делать мне. Для ПЛИС с 484 контактами не так сложно правильно сделать схемный символ, как может кому-то показаться. А вот для микросхемы с 1172 контактами это занятие весьма утомительно. Большинство названий контактов имеет длинные и похожие имена и в них легко запутаться. Можно генерировать все символы автоматом. Но тогда они не совпадают с «корпоративными» предпочтениями. В IOD легко можно создать символ по базе данных элементов просто перетаскивая мышкой из окна списка контактов в окно символа. Не скажу, что это также просто как играть в «Весёлую ферму», но на этом этапе мы просто можем мышкой назначать сигналы контактам микросхемы. При этом, можно указать как обозначать по названию, по функциональному назначению, по номеру контакта или по-своему. Я обычно выбираю отображение по функциональному назначению. Так как на мой взгляд такое название более информативно и тогда на схеме видно, что за сигнал сюда можно завести.

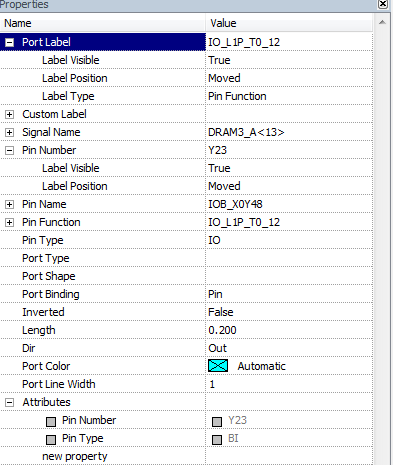

Если пробный проект еще не делался, то мы можем не задавать такой файл. А потом просто создать сигналы в окне программы. Типы сигналов по умолчанию. Для одиночных сигналов и для дифференциальных.Далее мы можем назначить место куда мы потом будем выкладывать файл с нашим размещением контактов.Затем нужно определиться как мы хотим работать со схемой, нужны ли нам полноценные символы или достаточно только создания цепей в схемном проекте, а описания всех контактов у нас будут передаваться только в виде обменного фала с САПР ПЛИС.Мне всегда нравился вариант когда не нужно создавать схемных элементов, а все обмены идут через внутренние неведомые пути. Но, работая в коллективе, приходится принимать более приземлённые правила игры. Так, согласно корпоративному стандарту оформления схем мне всегда нужно было делить символ по банкам, выносить отдельно цепи конфигурации, земли, питания и прочие. Есть в таком разделении плюсы, но есть и минусы. Схемный символ приходилось делать мне. Для ПЛИС с 484 контактами не так сложно правильно сделать схемный символ, как может кому-то показаться. А вот для микросхемы с 1172 контактами это занятие весьма утомительно. Большинство названий контактов имеет длинные и похожие имена и в них легко запутаться. Можно генерировать все символы автоматом. Но тогда они не совпадают с «корпоративными» предпочтениями. В IOD легко можно создать символ по базе данных элементов просто перетаскивая мышкой из окна списка контактов в окно символа. Не скажу, что это также просто как играть в «Весёлую ферму», но на этом этапе мы просто можем мышкой назначать сигналы контактам микросхемы. При этом, можно указать как обозначать по названию, по функциональному назначению, по номеру контакта или по-своему. Я обычно выбираю отображение по функциональному назначению. Так как на мой взгляд такое название более информативно и тогда на схеме видно, что за сигнал сюда можно завести. Из наблюдений могу отметить, что последние названия у Xilinx (для семейств 6 и 7 серии) получаются довольно кроткими и информативными.IO_L6N_T0_VREF_13IO — контакт ввода-выводаL6N — обозначение дифференциальной парыT0 — обозначение байта внутри которого можно производить свап сигналов данных для памяти (этот момент нужно уточнить!)VREF — сюда можно подавать внешнее опорное напряжение, если этого требует стандарт выбранного сигнала для банка и нет возможности подключить его внутри ПЛИС. 13 — номер банка.

Из наблюдений могу отметить, что последние названия у Xilinx (для семейств 6 и 7 серии) получаются довольно кроткими и информативными.IO_L6N_T0_VREF_13IO — контакт ввода-выводаL6N — обозначение дифференциальной парыT0 — обозначение байта внутри которого можно производить свап сигналов данных для памяти (этот момент нужно уточнить!)VREF — сюда можно подавать внешнее опорное напряжение, если этого требует стандарт выбранного сигнала для банка и нет возможности подключить его внутри ПЛИС. 13 — номер банка. У Altera тоже иногда попадаются нормальные функциональные обозначения, но чаще (моё субъективное мнение) трудновоспроизводимые названия контактов, которые потом не помещаются на лист со схемой. Возможно, если бы я делал схемы с большими объёмами памяти, умножителями или какие-нибудь коллайдеры, то мне бы пригодилось такое название.IO_DIFFIO_T18p__DATA15_DQ3T0_X9__DQ3T9_X18_DQ5T27_X36В этом случае выручает возможность указать Custom Label для имени контакта. И вписать руками необходимое название. Обычно я копирую функциональное назначение и сокращаю его до видаIO_T18p_DATA15_DQВ данном случаеIO — может использоваться для сигналов ввода-выводаT18p — это номер дифференциальной пары в верхнем сегментеDATA15 — этот контакт может быть использован для параллельной загрузки конфигурацииDQ — мне говорит, что это сокращение от функционального предназначения контакта (ещё могут быть DM и DQS)Это один из примеров, как можно назвать контакт на основе его функциональности и для какого-нибудь конкретного проекта, на первое место будет выведен какой-нибудь другой признак.Так, к примеру, у Altera при использовании LVDS сигналов нужно использовать внешнюю нагрузку. Для одних банков это нагрузочный резистор только на приёмной стороне, а для других — необходим еще и на выходе. Это можно отметить на схемном символе в свойстве Custom Label. Тоже касается сигналов PCI типа. Не для всех банков можно назначить стандарт шины 3.3V-PCI. И это тоже можно отметить на символе. Несмотря на всё большее вытеснение его стандартом PCIe в десктопных системах, в индустриальном исполнение он всё еще популярен. И некоторые заказчики ищут устройства именно в таком исполнении.Можно в символе добавить надпись, для всех контактов сразу. Это уменьшит количество текста внутри символа. Так как любая дополнительная информация будет перегружать символ и схему, тут нужен компромисс. Я такое делал для микросхем Xilinx, у которых есть микросхемы совместимые по контактам внутри одного корпуса с разным количеством логических элементов, но в «мелких» микросхемах часть контактов не задействована. Тогда в проекте часть схемы не запаивалась и можно было ставить более «лёгкую» микросхему. Учитывая это при раздаче контактов, потом можно сэкономить и на отсутствующих компонентах и на цене ПЛИС.Для удобства я делаю символы с разделением на банки. Исключение можно сделать для контактов конфигурации. Если проект имеет сложную структуру синхронизации, то в отдельный символ можно собрать входы CLK — локальные, глобальные и прочие. Контакты питания VCCO банков помещаются на символе вместе с банком или на отдельном — по желанию ГЛАВНОГО разработчика.Контакты питания ядра, VCCAUX, земли и прочего, чаще всего, выношу на отдельные символы.Якобы сейчас можно для всех контактов питания создать только цепь на схеме и не загромождать большим количеством однотипных контактов схему. У нас так делать не принято, поэтому я с такими опциями близко не знаком. Об этом можно ознакомится в справочной документации или из вебинаров и обучающих материалов в сети на сайте Mentor Graphics и его представителей.

У Altera тоже иногда попадаются нормальные функциональные обозначения, но чаще (моё субъективное мнение) трудновоспроизводимые названия контактов, которые потом не помещаются на лист со схемой. Возможно, если бы я делал схемы с большими объёмами памяти, умножителями или какие-нибудь коллайдеры, то мне бы пригодилось такое название.IO_DIFFIO_T18p__DATA15_DQ3T0_X9__DQ3T9_X18_DQ5T27_X36В этом случае выручает возможность указать Custom Label для имени контакта. И вписать руками необходимое название. Обычно я копирую функциональное назначение и сокращаю его до видаIO_T18p_DATA15_DQВ данном случаеIO — может использоваться для сигналов ввода-выводаT18p — это номер дифференциальной пары в верхнем сегментеDATA15 — этот контакт может быть использован для параллельной загрузки конфигурацииDQ — мне говорит, что это сокращение от функционального предназначения контакта (ещё могут быть DM и DQS)Это один из примеров, как можно назвать контакт на основе его функциональности и для какого-нибудь конкретного проекта, на первое место будет выведен какой-нибудь другой признак.Так, к примеру, у Altera при использовании LVDS сигналов нужно использовать внешнюю нагрузку. Для одних банков это нагрузочный резистор только на приёмной стороне, а для других — необходим еще и на выходе. Это можно отметить на схемном символе в свойстве Custom Label. Тоже касается сигналов PCI типа. Не для всех банков можно назначить стандарт шины 3.3V-PCI. И это тоже можно отметить на символе. Несмотря на всё большее вытеснение его стандартом PCIe в десктопных системах, в индустриальном исполнение он всё еще популярен. И некоторые заказчики ищут устройства именно в таком исполнении.Можно в символе добавить надпись, для всех контактов сразу. Это уменьшит количество текста внутри символа. Так как любая дополнительная информация будет перегружать символ и схему, тут нужен компромисс. Я такое делал для микросхем Xilinx, у которых есть микросхемы совместимые по контактам внутри одного корпуса с разным количеством логических элементов, но в «мелких» микросхемах часть контактов не задействована. Тогда в проекте часть схемы не запаивалась и можно было ставить более «лёгкую» микросхему. Учитывая это при раздаче контактов, потом можно сэкономить и на отсутствующих компонентах и на цене ПЛИС.Для удобства я делаю символы с разделением на банки. Исключение можно сделать для контактов конфигурации. Если проект имеет сложную структуру синхронизации, то в отдельный символ можно собрать входы CLK — локальные, глобальные и прочие. Контакты питания VCCO банков помещаются на символе вместе с банком или на отдельном — по желанию ГЛАВНОГО разработчика.Контакты питания ядра, VCCAUX, земли и прочего, чаще всего, выношу на отдельные символы.Якобы сейчас можно для всех контактов питания создать только цепь на схеме и не загромождать большим количеством однотипных контактов схему. У нас так делать не принято, поэтому я с такими опциями близко не знаком. Об этом можно ознакомится в справочной документации или из вебинаров и обучающих материалов в сети на сайте Mentor Graphics и его представителей.

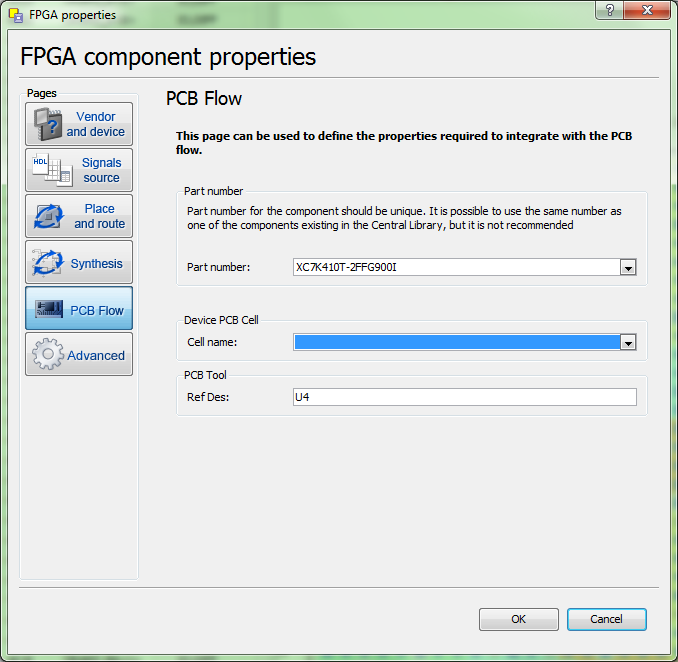

Созданные символы передаю прямо в проект схемы, указываю тип корпуса, произвожу аннотацию в плату и микросхема привязана к плате, схеме и IODesigner`у. Создание и присвоение сигналовКак было описано выше, мы можем сигналы экспортировать из файла или создать сами.

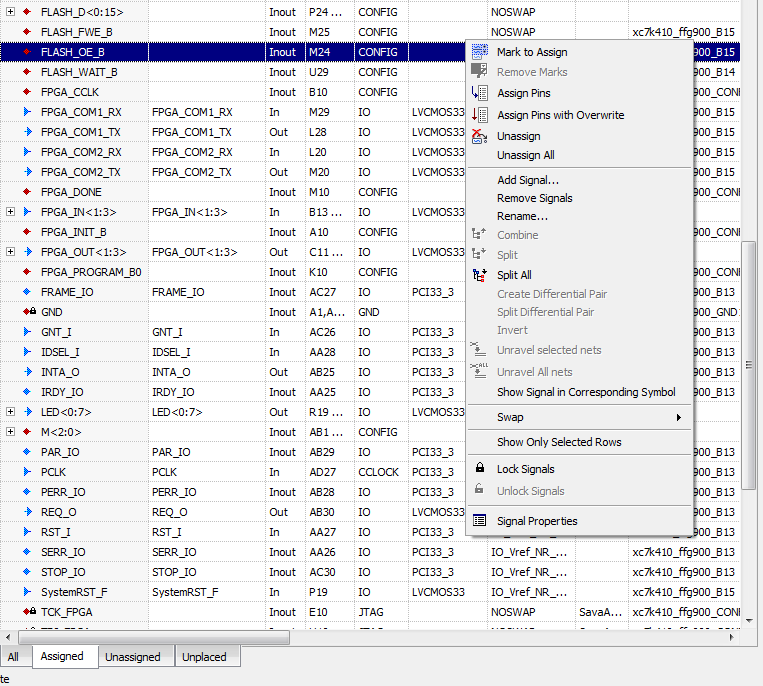

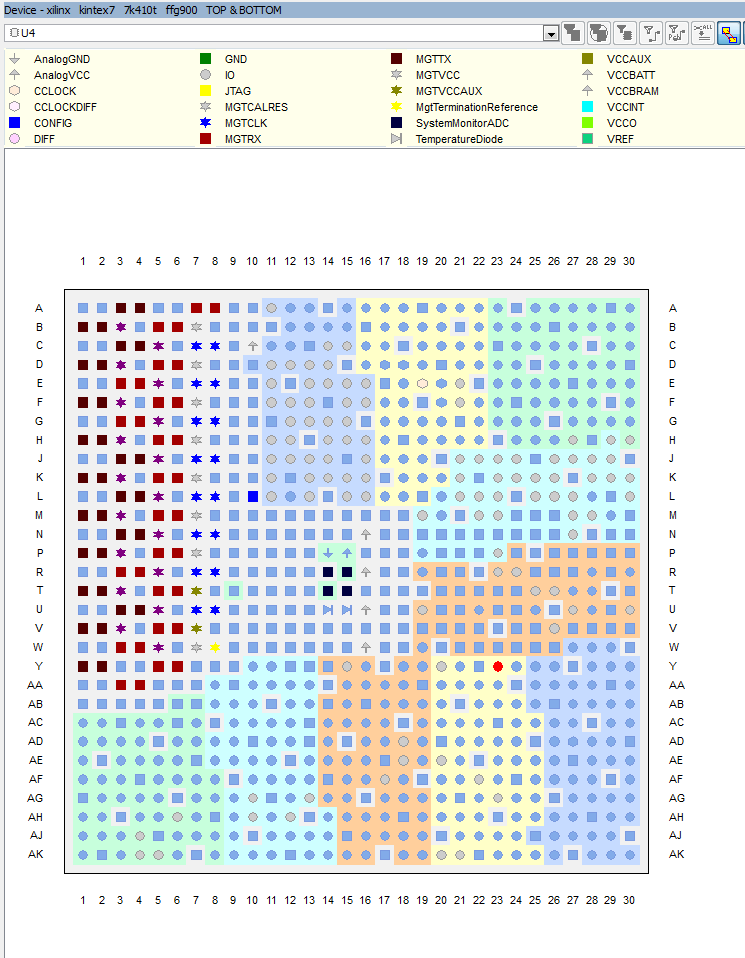

Создание и присвоение сигналовКак было описано выше, мы можем сигналы экспортировать из файла или создать сами. Присваивать сигналы можно как мышкой, так и через импорт/экспорт. Зажимая клавиши SHIFT, CTRL или ALT можно пере-присвоить сигналы на уже назначенные контакты. Или назначить все выбранные сигналы в один банк. Визуально банки отображаются разным цветом. Контакты разного типа отображаются разными значками. Можно включить отображение дифференциальных пар. Со временем занятые сигналы будут закрашены.

Присваивать сигналы можно как мышкой, так и через импорт/экспорт. Зажимая клавиши SHIFT, CTRL или ALT можно пере-присвоить сигналы на уже назначенные контакты. Или назначить все выбранные сигналы в один банк. Визуально банки отображаются разным цветом. Контакты разного типа отображаются разными значками. Можно включить отображение дифференциальных пар. Со временем занятые сигналы будут закрашены. Обновляем схему и видим на схеме символы уже с сигналами.

Обновляем схему и видим на схеме символы уже с сигналами. Смотрим как они подсоединились на плате. Обычно это уже показанная выше «каша».Иногда я сразу делаю просто список сигналов, чтоб они автоматом создались в системе, потом их в схемном редакторе перетаскиваю к другим элементам.Есть вариант импорта списка сигналов из схемы.Синхронизировав проект схемы, платы и IO Designer мы можем вызвать отображение сигналов в окне IO Designer. С идущими цепями от ПЛИС к подсоединённым к ней компонентам.Теперь мы можем расчесать наши сигналы. Причём всё это будет сделано автоматически в соответствии с введёнными нами правилами. Конфигурационные сигналы никуда не денутся. Также мы можем предварительно зафиксировать сигналы для предотвращения смены их расположения.

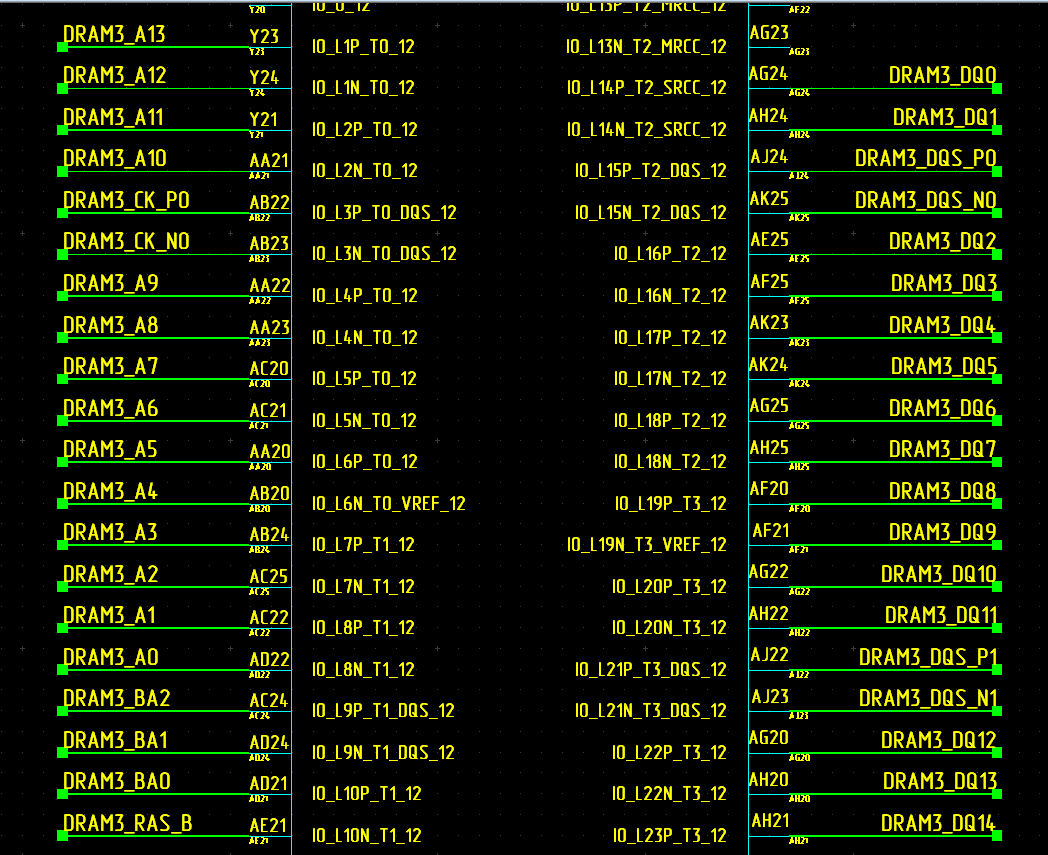

Смотрим как они подсоединились на плате. Обычно это уже показанная выше «каша».Иногда я сразу делаю просто список сигналов, чтоб они автоматом создались в системе, потом их в схемном редакторе перетаскиваю к другим элементам.Есть вариант импорта списка сигналов из схемы.Синхронизировав проект схемы, платы и IO Designer мы можем вызвать отображение сигналов в окне IO Designer. С идущими цепями от ПЛИС к подсоединённым к ней компонентам.Теперь мы можем расчесать наши сигналы. Причём всё это будет сделано автоматически в соответствии с введёнными нами правилами. Конфигурационные сигналы никуда не денутся. Также мы можем предварительно зафиксировать сигналы для предотвращения смены их расположения. Обратите внимание, что сигнал DRAM3_RESET_B, которому должен быть присвоен стандарт ввода/вывода LVCMOS_1.35V и он не может находится в одном банке с сигналами SSTL стандарта, назначен в банк 17, а все остальные сигналы DRAM3* в банк 12. Так как в системе всего четыре сигнала с LVCMOS_1.35V, то им назначен стандарт LVCMOS1.8V и поставлен преобразователь уровня.

Обратите внимание, что сигнал DRAM3_RESET_B, которому должен быть присвоен стандарт ввода/вывода LVCMOS_1.35V и он не может находится в одном банке с сигналами SSTL стандарта, назначен в банк 17, а все остальные сигналы DRAM3* в банк 12. Так как в системе всего четыре сигнала с LVCMOS_1.35V, то им назначен стандарт LVCMOS1.8V и поставлен преобразователь уровня. Несмотря на кажущуюся запутанность сигналов, они сейчас расправлены в соответствии с назначенными правилами. Для удобства работы с проектом в Quartus.На изображении видны расставленные компоненты, и тянущиеся к ним линии от ПЛИС. Иногда если не все компоненты расставлены не получается с первого раза разложить все контакты для беспроблемной трассировки. Хотя всё зависит от задачи.После такого распределения контактов уже можно отдавать схему на окончательную трассировку или трассировать самому.Также можно сделать экспорт в Verilog / VHDL файл. Можем сделать экспорт в *.ucf, *.pin или другой файл. Отдать его проектировщику ПЛИС для проведения пробного проекта, вдруг чего-то не учли. Но в маленьком коллективе не всегда получается сразу такое провести ввиду большой загруженности другими проектами. (Старые доработки, новые пожелания заказчиков или параллельные проекты).Ограничения.Есть у данного метода ограничения, которые я не всегда знаю как обойти. Но в основном они связаны с необходимостью делать много чего для универсальности и про запас. Приходится изобретать костыли и прочее. Так у Altera по умолчанию нельзя располагать дифференциальный сигнал рядом с дифференциальным. Компилятор выдаст предупреждение. Мы можем его обойти установив в Pin Planner Quartus параметр SLEW_RATE = 0 MHz. После чего компиляция успешно завершится. Даже если на самом деле у нас сигнал будет болтаться с частотой 20 МГц. В IODesigner такого параметра нет. В итоге на схеме эти контакты задействую последними или устанавливаю им такой тип сигнала, чтоб это не вызывало конфликта, например PCB сигнал или конфигурационный.Есть и другие ограничения, которые обычно обходятся. Но в целом, я к ним отношусь положительно, так как они заставляют еще раз заглянуть в документацию на микросхему гораздо раньше чем, приедет готовая плата.Для тех, кто работает в других системах проектирования некоторые вещи могут показаться не очевидными и возможно не нужными. Так, насколько я знаю (слышал), Altium позволяет настраивать компиляцию проекта для ПЛИС прямо в проекте со схемой и платой. Я не в курсе всех его возможностей. И для людей, которые проектируют в нём не нужен импорт в Quartus или ISE. Но у нас проект печатной платы делает один человек, проекты для ПЛИС другие люди. Я отдавая схему на трассировку стараюсь как можно правильнее описать сигналы, при этом предоставляю проектировщику печатной платы некую свободу действий на изменение контактов. Любые предупреждения, которые возникают мы согласовываем по мере их накопления.Напоследок хотелось бы сказать, что «IO Designer» не панацея. Он не превращает проектирование схемы, платы и проекта на ПЛИС в интерактивную игру и не освобождает от изучения документации на микросхемы. Но работать с таким инструментом гораздо приятнее. В статье описаны не все его преимущества. Также не могу судить о полноте библиотек для всех микросхем, так как мне приходилось работать лишь с некоторыми из семейств Altera и Хilinx. C Lattice мне как-то удалось чуть-чуть поработать на отладочном комплекте, но до схемы, а тем более до платы дело не дошло. С Actel я не работал вообще. Из замечаний по Xilinx могу отметить, что в моей версии нет прямой передачи файла ограничений в/из Vivado. Может с обновлениями выйдет. Но так как проект ПЛИС Xilinx веду не я, то в чём точно проблема — не разбирался. Мы обошлись экспортом через *.csv файл.Данная публикация не претендует на звание учебника по «IODesigner», для этого есть немало уроков от Mentor Graphics. Знаю, что на русском языке обучение ведёт компания Мегратек. www.megratec.ru.Также, насколько мне известно, Mentor Graphics готовит к выводу на рынок xPedition — новую версию системы проектирования. Что там добавят конкретно по IODesigner`у покажет время. Из тех презентаций которые я видел на меня произвели впечатление обновления 3D отображения в платах и проектирование устройств с несколькими платами в одном проекте.Также, помимо названных мной САПР, для печатных плат существуют и другие. У каждой найдётся список из преимуществ и список «чего в Y не хватает как в Х». И если я не назвал их преимущества по сравнению с вариантом работы через IOD — не обижайтесь. Можете написать об этом в комментариях. Или статью о том как вы проектируете ПЛИС в вашем САПР.

Несмотря на кажущуюся запутанность сигналов, они сейчас расправлены в соответствии с назначенными правилами. Для удобства работы с проектом в Quartus.На изображении видны расставленные компоненты, и тянущиеся к ним линии от ПЛИС. Иногда если не все компоненты расставлены не получается с первого раза разложить все контакты для беспроблемной трассировки. Хотя всё зависит от задачи.После такого распределения контактов уже можно отдавать схему на окончательную трассировку или трассировать самому.Также можно сделать экспорт в Verilog / VHDL файл. Можем сделать экспорт в *.ucf, *.pin или другой файл. Отдать его проектировщику ПЛИС для проведения пробного проекта, вдруг чего-то не учли. Но в маленьком коллективе не всегда получается сразу такое провести ввиду большой загруженности другими проектами. (Старые доработки, новые пожелания заказчиков или параллельные проекты).Ограничения.Есть у данного метода ограничения, которые я не всегда знаю как обойти. Но в основном они связаны с необходимостью делать много чего для универсальности и про запас. Приходится изобретать костыли и прочее. Так у Altera по умолчанию нельзя располагать дифференциальный сигнал рядом с дифференциальным. Компилятор выдаст предупреждение. Мы можем его обойти установив в Pin Planner Quartus параметр SLEW_RATE = 0 MHz. После чего компиляция успешно завершится. Даже если на самом деле у нас сигнал будет болтаться с частотой 20 МГц. В IODesigner такого параметра нет. В итоге на схеме эти контакты задействую последними или устанавливаю им такой тип сигнала, чтоб это не вызывало конфликта, например PCB сигнал или конфигурационный.Есть и другие ограничения, которые обычно обходятся. Но в целом, я к ним отношусь положительно, так как они заставляют еще раз заглянуть в документацию на микросхему гораздо раньше чем, приедет готовая плата.Для тех, кто работает в других системах проектирования некоторые вещи могут показаться не очевидными и возможно не нужными. Так, насколько я знаю (слышал), Altium позволяет настраивать компиляцию проекта для ПЛИС прямо в проекте со схемой и платой. Я не в курсе всех его возможностей. И для людей, которые проектируют в нём не нужен импорт в Quartus или ISE. Но у нас проект печатной платы делает один человек, проекты для ПЛИС другие люди. Я отдавая схему на трассировку стараюсь как можно правильнее описать сигналы, при этом предоставляю проектировщику печатной платы некую свободу действий на изменение контактов. Любые предупреждения, которые возникают мы согласовываем по мере их накопления.Напоследок хотелось бы сказать, что «IO Designer» не панацея. Он не превращает проектирование схемы, платы и проекта на ПЛИС в интерактивную игру и не освобождает от изучения документации на микросхемы. Но работать с таким инструментом гораздо приятнее. В статье описаны не все его преимущества. Также не могу судить о полноте библиотек для всех микросхем, так как мне приходилось работать лишь с некоторыми из семейств Altera и Хilinx. C Lattice мне как-то удалось чуть-чуть поработать на отладочном комплекте, но до схемы, а тем более до платы дело не дошло. С Actel я не работал вообще. Из замечаний по Xilinx могу отметить, что в моей версии нет прямой передачи файла ограничений в/из Vivado. Может с обновлениями выйдет. Но так как проект ПЛИС Xilinx веду не я, то в чём точно проблема — не разбирался. Мы обошлись экспортом через *.csv файл.Данная публикация не претендует на звание учебника по «IODesigner», для этого есть немало уроков от Mentor Graphics. Знаю, что на русском языке обучение ведёт компания Мегратек. www.megratec.ru.Также, насколько мне известно, Mentor Graphics готовит к выводу на рынок xPedition — новую версию системы проектирования. Что там добавят конкретно по IODesigner`у покажет время. Из тех презентаций которые я видел на меня произвели впечатление обновления 3D отображения в платах и проектирование устройств с несколькими платами в одном проекте.Также, помимо названных мной САПР, для печатных плат существуют и другие. У каждой найдётся список из преимуществ и список «чего в Y не хватает как в Х». И если я не назвал их преимущества по сравнению с вариантом работы через IOD — не обижайтесь. Можете написать об этом в комментариях. Или статью о том как вы проектируете ПЛИС в вашем САПР.