Altera Quartus Prime и ModelSim под Linux. Вводное руководство

В очередной раз, начав изучать что-то новое для себя, я столкнулся с типичной для меня проблемой: нет нигде быстро гуглящегося how-to и step-by-step руководства по быстрому созданию какой-либо простой конструкции на Verilog и описания способа эту конструкцию быстро симулировать без необходимости запуска кода в железе для проверки конечного результата. Я надеялся очень быстро найти готовый материал о том, как под Altera Quartus 20.1 и ModelSim 2020.1 под Linux всё по-быстрому сделать и идти дальше. В итоге не найдя ничего системно и последовательно описанного в одном месте я традиционно разобрался самостоятельно и решил это исправить своей очередной статьей на Хабре.

Возможно, этот материал поможет таким же как я новичкам на самом старте и позволит не растерять энтузиазм во время танцев по граблям. Всем, кто заинтересовался — добро пожаловать под кат.

Дисклеймер. Перед началом повествования, хотелось бы заранее оговориться, что основная цель, которую я преследую при написании этой статьи — рассказать о своем опыте. Я не являюсь профессиональным разработчиком под ПЛИС на языке SystemVerilog и могу допускать какие-либо ошибки в использовании терминологии, использовать не самые оптимальные пути решения задач, etc. Но отмечу, что любая конструктивная и аргументированная критика только приветствуется. Что ж, поехали…

❯ Постановка задачи

Итак. Представим, что вы абсолютный новичок в области ПЛИС aka FPGA и вот однажды вы услышали, интересные рассказы о том, что с помощью одного из языков описания аппаратуры (HDL) можно решать разнообразные задачи с очень высокой скоростью и при этом параллельно, т.е. одновременно. Первым вопросом, которым задался я как новичок когда услышал про ПЛИС —, а с чего начать? На тот момент мне казалось, что все начинается с отладок с нужным чипом и примеров. Я без особого понимания критериев отбора, чем отличаются Altera от Xilinx — быстренько заказал себе отладку на Cyclone IV и после того как получил — научился создавать и запускать простейшие проекты. Каждая правка исходного проекта и проверка сопровождалась ожиданием синтеза, роутинга, заливкой прошивки в ПЛИС для проверки и отладки с помощью светодиодов и кнопок и SignalTap. И чем сложнее были примеры — тем больше времени я тратил на ожидание синтеза, рассовывания пробников отладчика по сигналам и тут я начал задумываться о том, что возможно что-то тут я делаю не так. А если вспомнить, что SignalTap занимает в ПЛИС тоже некоторое количество логических блоков и в сложных проектах он уже не умещался в ПЛИС — ситуация точно требовала изменения подхода.

И тут я начал вникать в то, как организуют процесс разработки в среде профессионалов — я понял, что я упустил тут один очень важный шаг — симуляцию и тестирование с помощью т.н. testbench-ей.

Вникнув и разобравшись — я захотел поделиться своим опытом в этом материале и при написании этой статьи я поставил для себя несколько задач: разобрать вопрос создания простого проекта в Altera Quartus под Linux и как запустить его симуляцию в ModelSim, с попутным объяснением как решить возникающие проблемы, коих по ходу дела возникает немало (вполне возможно, что только у меня).

Задачи для меня и моего уровня вполне достижимые, давайте расскажу и покажу как я их решал.

❯ Общий flow разработки под ПЛИС

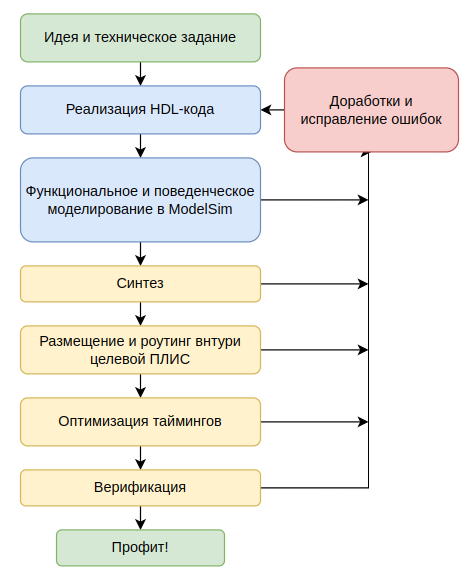

Вообще, отдельно стоит рассказать о том, как работают с ПЛИС профессионалы и что следует взять себе за ориентир. Ниже, я попытался обобщить в виде схемы свое представление о алгоритме разработки под ПЛИС. Коротко опишу каждый из этих этапов. Оговорюсь сразу, что в рамках этой статьи я рассмотрю только первые три интересующих нас этапа.

Идея и техническое задание. Пункт с вполне понятным смысловым наполнением. На этом этапе формируется идея будущего устройства, что он должен уметь делать, чего делать не должен. На основании идеи формируется уже техническое задание которое отражает в форме измеримых величин требования для конечного устройства.

Реализация HDL-кода. На этом этапе происходит основная часть работы — в HDL-коде реализуется конечный автомат или группа из таковых, вместе со всеми багами, корявостями и синтаксическими ошибками