TSMC начинает разработку техпроцесса 2 нм

Примечание. Радиус атома кремния составляет 110 пикометров или 0,11 нанометра. Термин «размер узла» в процессе фотолитографии с пометкой »14 нм»,»10 нм»,»7 нм»,»5 нм»,»3 нм» и »2 нм» является маркетинговым и не имеет отношения к геометрии транзисторов.

Один из лидеров полупроводниковой индустрии TSMC, похоже, не собирается хоронить закон Мура. Тайваньская компания сейчас ведёт массовое производство по технологическому процессу 7 нм (огромное количество заказов на процессоры Ryzen 3000 и графические карты Navi). Она вот-вот готова запустить 5 нм, а теперь объявила о начале исследований в области процесса с нормой 2 нм. Об этом сказано в годовом отчёте для акционеров, сообщает Digitimes.

В данный момент TSMC параллельно с Samsung налаживает производство технологического конвейера на 5 нм с использованием фотолитографии в глубоком ультрафиолете (EUV). Интересно, что единственным в мире производителем степперов для фотолитографии в глубоком ультрафиолете является голландская компания ASML. Это исключительно сложные машины весом 180 тонн и стоимостью порядка $170 млн каждая, компоненты для которых производят около 5000 поставщиков со всего мира.

Пока неизвестно, какие конкретные технологии TSMC собирается применить для нового технологического процесса, да и разработки пока в ранней стадии, так что пока рано говорить не то что о сроках запуска в производство, но даже об успехе этих разработок в принципе.

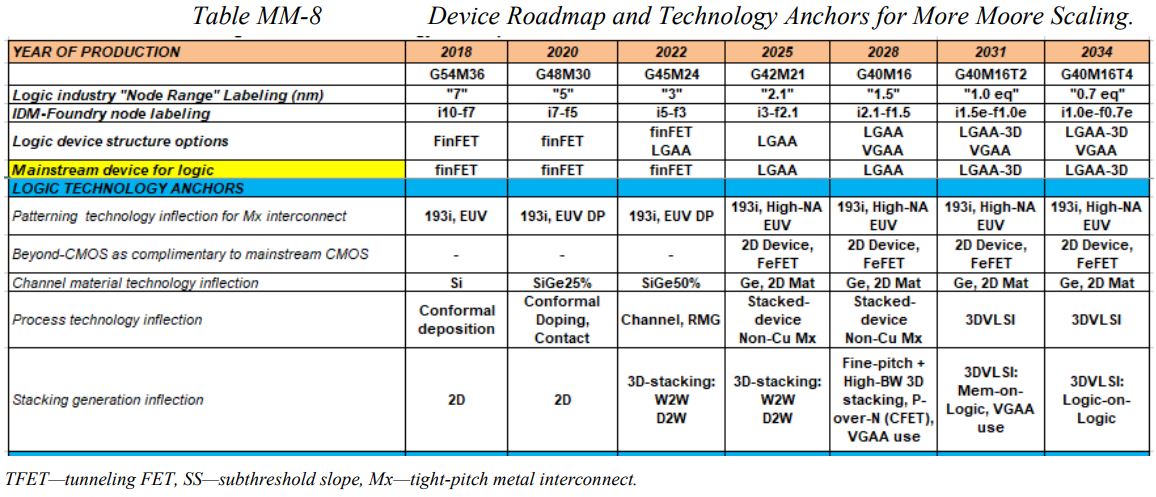

Однако TSMC придерживается своих долгосрочных планов, которые объявила ещё в 2018 году по девизом More Moore, что относится к продолжению масштабирования количества транзисторов на микросхемах в соответствии с законом Мура. Вот как TSMC очертила примерное развитие технологий до 2034 года:

Согласно этой «дорожной карте», транзисторы с размером узла 3 нм будут изготавливаться по архитектуре GAAFET и FinFET.

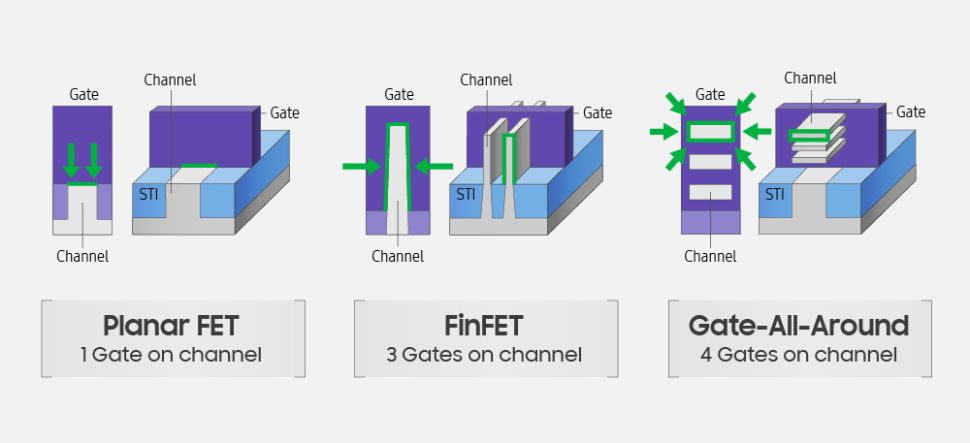

FinFET — трёхмерная архитектура, по которой сейчас изготавливаются транзисторы 7 нм и 5 нм. Возможно, её удастся применять и для 3 нм.

На смену FinFET должна прийти архитектура GAAFET (gate-all-around FET), её с 2000 года разрабатывает организация, в которую входят также IBM, Globalfoundries и Samsung. По информации источников, TSMC взвешивает разные варианты для 3 нм, включая нанослои, нанопровода и форсированные FinFET.

Как видно из названия, главной особенностью архитектуры GAAFET (gate-all-around FET) являются кольцевые затворы. Каналы транзисторов представляют собой нанопровода, сформированные из нескольких горизонтальных кремниевых «нанолистов», в то время как у FinFET канал транзистора представляет собой монолитную вертикальную конструкцию, что накладывает ограничения по масштабированию.

Внутренняя структура транзистора GAAFET 5 нм. Фото: IBM

В январе 2020 года южнокорейская компания Samsung сообщала о первых успехах в разработке транзисторов GAAFET по техпроцессу 3 нм. Вероятно, TSMC движется в том же направлении.

Иллюстрация: Samsung

Аббревиатура LGAA в плане TSMC относится к «горизонтальным» (lateral) GAAFET в 2D-процессоре, а «вертикальные» (VGAAFET) будут использоваться в неких 3D-структурах, о которых ещё ничего не известно.

Любопытно, что TSMC планирует ещё десятилетиями использовать 193-нм литографию, параллельно с фотолитографией в глубоком ультрафиолете.

В плане упоминается также технология high-NA EUV. Здесь NA означает произвольно количество измерений, то есть диапазон углов, под которыми система может принимать или излучать свет. То есть это нечто вроде «многомерной» фотолитографии как альтернатива многослойным конструкциям.

С запуском производство по техпроцессу 5 нм в 2020 году есть вероятность, что и дальше всё пойдёт по этому плану, так что можно ожидать 3 нм к 2022 году и 2 нм к 2024–2025 годам.