Сложные цепи из последовательных звеньев и параллельных шин — согласование цифрового сигнала внутри таких схем

Стоит оговорить изначально, что мои публикации всё-же относятся к мнению, а не туториалу, и следовали, до этой включительно, по причине недоработок и исправления ошибок. Потому что руководствуюсь, в первую очередь, учебником по схемотехнике («Цифровая схемотехника Шустов М.А), кому интересно — тут будет много цитат и схем из книги, а видение схемотехники производителями FPGA или её необходимые поправками в необходимых им целях (ну и главное — написать код, а конфигурацию чипа уже может получится подобрать подходящую, даже если этого не произойдёт — ничего, подожду когда начнут производить платы нужной конфигурации, а до этого — буду дальше развивать и работать над проектом с теми платами, что имеются в продаже) считаю всё-же вторичным, хоть и изучать будет необходимо. Нет согласующих резисторов в FPGA — что мешает реализовать целый ряд схем, но зато есть чем заменить их для цифрового сигнала внутри таких схем. Пытался найти в сети альернативу согласующему резистору для применения внутри синтезируемой схемы, поисковик выдал скромный результат поиска, содержанием которого оказалось ничего по существу — категоричное нет на всех форумах, и иногда что-то близкое, но моей задачи не решающее. Да и собственно в схеме развёрнуты две задачи — некоторый кэш нового типа и механизм управления таким кэшем, по сути — часть процессора нового типа.

В схеме много вникать. Если Вы не верите IDE Logisim Evolution — можете просто пройти мимо и не принимать тут изложенный материал во что-то нужное и полезное. Тем более что это в общем-то работа новичка, который просто развивает свой проект и взгляды в новых областях, сталкивается с новыми задачами и решает их новыми способами. Поэтому пока предмет мной не изучен достаточно — всё это остаётся в категории «мнение». И в конечной реализации процессора функционал кэша мостов может быть развернут, так как нигде не оговаривалось что это за триггер RUN, и в принципе его содержимое может быть изменено с нуля на единицу через дешифратор адресов кэша команд , если каждый такой триггер привязать к звену кэша моста для его запуска. То-есть ненужные ячейки кэша мостов, даже если прохождение сигнала прямое через ключи, тоже можно пропустить запуская его с нужной точки (ключи тоже срабатывают не мгновенно).

Далее стоит извиниться перед читателем, что писал про мгновенное срабатывание на логических элементах, где его не было по определению, мной их значки и симуляция использовались для ускорения отладки и создания схем — с ними быстрее. Теперь, после некоторой отладки применяю те значки, которые согласно цифровой схемотехнике.

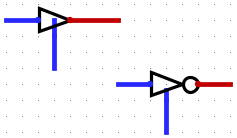

Что тут подразумевается под значками

Тут подразумевается электронный ключ или, как ещё называют, электронный ключевой элемент. Далее, где нужно, привожу цитатыиз книги »Цифровая схемотехника» основы построения от азов до вершин мастерства, автор Шустов М.А. Но привожу немного больше, чем использую в своих целях, привожу пояснения на этот предмет. Под спойлером можно пропустить, так как к проекту процессора отношения не имет, и в любом случае проекта не оставлю, поскольку слишком много инструментов и способов сделать кэш мостов очень эффективным.

Hidden text

Важно запомнить:

Электронный ключевой элемент — это электронное устройство, предназначенное для замыкания или размыкания цепи при воздействии на него управляющего сигнала.

Способ управления логическими элементами и представления сигналов в цифровой схемотехнике применяется потенциальный и импульсный.

Потенциальный способ управления заключается в том, что значениям логической единицы и нуля ставят в соответствие два заметно различимых уровня напряжения или тока.

В зависимости от того, какой из этих уровней соответствует значению логической единицы или нуля различают положительную и отрицательную логику. В положительной логике значению высокого уровня напряжения или тока соответствует значение логической единицы; в отрицательной — логического нуля вне зависимости от полярности напряжения или направления тока.

Это тут было к сведению. Ближе к тому теперь что подразумевается в моих схемах:

Импульсный способ управления заключается в том, что значению логической единцы / нуля ставится соответствие факт наличия / отсутствия импульса или его положительного отрицательного перепада, соответственно.

При потенциальном способе представления значение логической переменной может быть определено в любой произвольный момент времени. При импульсном прдставлении это может быть сделано в строго определённые моменты времени.

При потенциальном представлении возможен как синхронный, так и асинхронный съём информации. При импульсном представлении возможен только синхронный съём инофрмации.

Мной выбран цифровой способ представления. Некоторые недостатки:

Задержки сигналов при прохождении через логические элементы;

Электронные ключевые элементы (электронные ключи), согласно цифровой схемотехнике, не являются базовыми элементами цифровой логики.

Далее из книги, но немного сокращённо, что есть в цифровой схемотехнике. По функицональному признаку выделяют основные элементы и устройства цифровых интегральных микросхем:

электронный ключевой элемент (был описан ранее), базовые логические элементы (интегральные микросхемы содержащие электронные ключевые элементы и вполняющие базовые логические функции НЕ (инверсию), И (конъюкцию), ИЛИ (дизъюкцию), а также их комбинации И-НЕ, И-ИЛИ-Не и другие; драйверы, мультивибратор, одновибратор, триггер, синхронный тригер, триггер Шмитта, регистр, счётчик суммирующий, счётчик ревирсивный, дешифратор, шифратор, мультиплексор, демультплексор.

Книга очень хорошая, но материал привожу в сокращённом виде.

Электронные ключи входят в состав многих импульсных устройств. Основу любого электронного ключа составляет активный элемент (обычно транзистор), работающий в в ключевом режиме. Ключевой режим характеризуется двумя состояниями ключа: включено ; выключено.

Идеальных электронных ключей нет, и переход ключа из одного состояние в другое происходит не мгновенно, а в течении времени, обусловленного инерционностью активного элемента и наличием паразитных ёмкостей.

Исходя из того что под спойлером — оптимистичность данной занятки с собственным процессором не очень велика, но тем не менее учитывая, что все ключевые элементы, в работе схемы, требующие большой скорости прохождения сигнала без остановки (в зависимости от состояния каждого следующего по цепи звена — звено пропускается или запускается в работу) переключаются в включённое состояние задолго до требуемого момента времени прохождения сигнала и то, что функционал кэша мостов можно значительно расширять, то тем не менее можно надеяться на какой-то положительный эффект, и даже вполне не плохой.

Когда столкнулся с проблемой более точной отладки двух механизмов на схеме, то обнаружил что нужен согласующий резистор, без него всё вроде как и работает, но одна мысль что на некоторых проводах мелькает состояние ошибки ощущение доделаного дела быстро улетучило.

Hidden text

Один человек окрылённый мыслью, что счётчик команд намного экономинчее моей махины пристраиваемой мной к кэшу нового типа процессора нового типа (режим работы без счётчика команд. Но так-то нет дыма без огня и счётчик команд — цветочки, дешифратор адресов — вот что потребляет ресурсы, а счётчик — это всего лишь вишенка на вершине огромного торта ряда некоторых проблем. И поэтому мне не хочется оставлять своей идеи.

И почему я всё ещё не приступил к работе с своей платой — потому что нужно сначала было исправить все недоработки и ошибки.

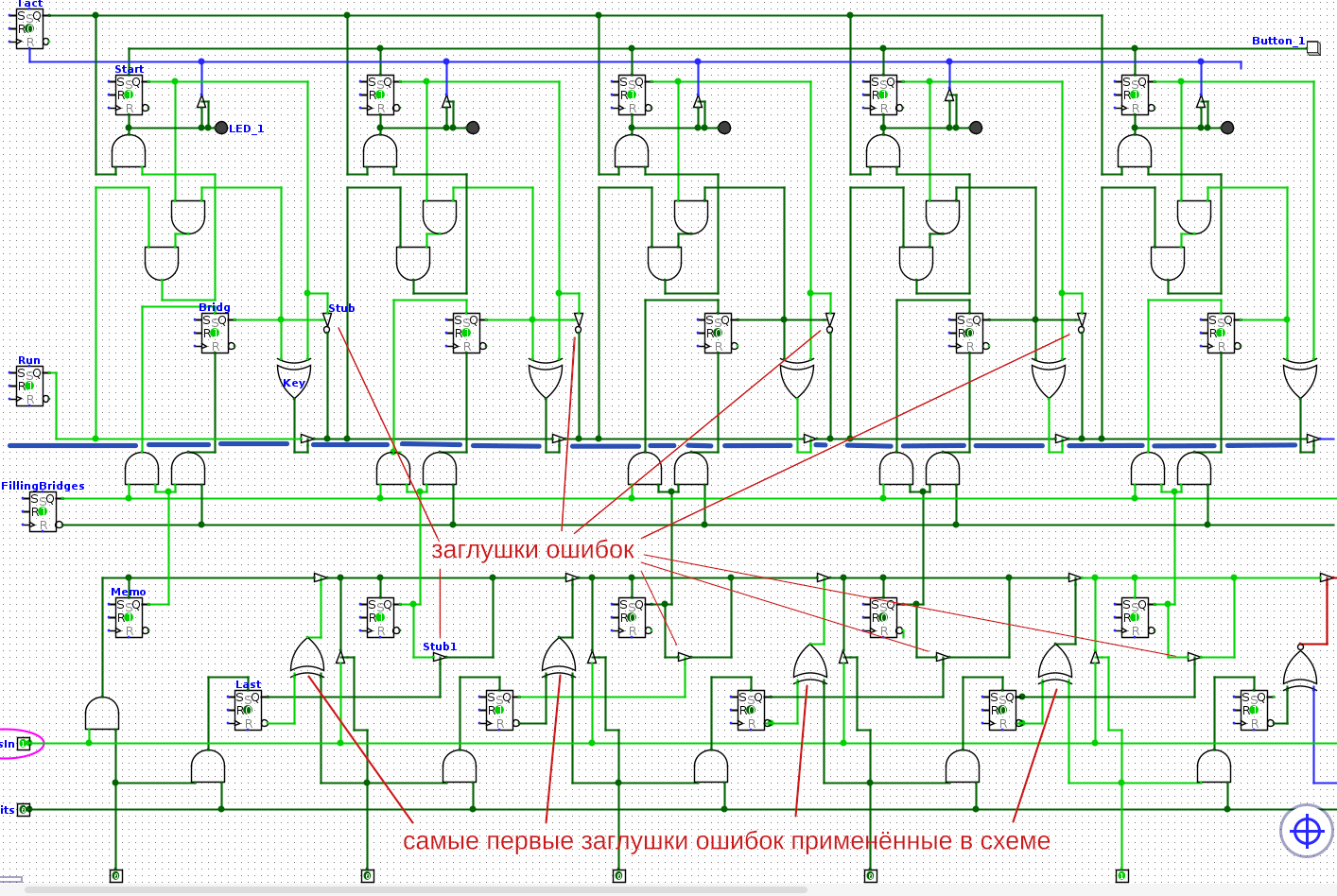

Далее исправленный кэш мостов.

Там пока по прежнему всего два триггера на звено цепи кэша мостов (и не ресширяемый пока функционал). Звено цепи кэша мостов — некоторая ячейка схемы, которая активирует ячейку памяти кэша команд не прибегая к работе дешифратора адресов команд. На схеме ячейка памяти кэша команд обозначена просто активируемым светодиодом.

Ну во первых почему он исправлен — считаю что перспективнее использовать электронные ключи, чем логические элементы, потому что они будут быстрее срабатывать. Конечно это зависит от типа ключей — на элементах какой логики они реализованы, да и вообще логические элементы, как я понял устроены немного сложнее и время их срабатывания — больше. И даже если это не так, и если базовые логические элементы устроены не намного сложнее ключа, триодного или транзисторного, то нет никаких гарантий, что компилятор Verilog подключит ножки на шинах именно так как нужно и быстродействие не утратится, кроме того в электронных ключах бывает на выходе плавающий сигнали он может по мере повторения накапливаться в ошибку, поэтому наверняка что базовые логические элементы устроены намного сложнее электронных ключей.

И вот мне писали что нет, это типа не так. Да это так, ви пржде чем писать такое — попробовали-бы в симуляторе сами хоть одну схему с собственной шиной и сразу-же убедились бы в том, что электронный ключ намного устроен проще базового логического элемента. А повторение чужих отлаженных схем и их созерцание в симуляторах — полной картины и представления не даст никогда. И тем, кто пишет, что не нужно рисовать схем и даже делать свой процессор, так как на FPGA реализовать абсолютно всё, скажу — ну раз всё так просто, напишите на Verilog для FPGA …любой САПР, ОС, или хотя-бы полноценный Blender 3D. Как сделаете — обязательно напишите об этом другим.

Во вторых — без электронных ключей к шине цепи сложно подключить звенья и заставить их работать без ошибки. Это было выявлено после отладки механизма заполнения кэша мостов, и на схеме «заглушки» ошибок, получаемых в результате повторений плавающего сигнала отмечены отдельно, как самые первые, и потом уже вторые. Вторые были сделаны просто из желания сделать всё как надо и доработать схему, хоть она и работала и так, но хотелось чтобы сигнала ошибок не возникало во время работы схемы.

и всёВ нижней части схемы, отделённой от верхней синими отрезками расположенными горизонтально, отображён механизм заполнения кэша мостов. В верхней — сам кэш мостов. Заглушки ошибок — дело кропотливое, так как метод ни систематизирован и не формализован до уровня технологии, и к каждому типу звена цепи на местах её возникновения нужен свой подход и решение, да алгоритмизации поиска места вставки и типа заглушки я не дошёл.

Как это работает (как работают заглушки ошибок — каждый может проверить сам).

Сначала в триггер линии Last (от триггера с меткой Last вправо на схеме), являющимся ограничением заполнения триггеров линии Memo, записывается единица, это делается подачей сигнала в самый нижний ряд контакта, и сигнала единицы на контакт самого нижнего горизонтального провода (не стал заполнять схему метками, так как это вероятно сильно усложнит её прочтение). После чего эти на сигналы единицы снова меняются на ноль. Затем, если нужно, производится установка в триггер с меткой FillingBridges значения, которое нам нужно залить в триггеры Bridg кэша мостов в верхней частисхемы. Если триггер или триггеры заполнятся единицею, то в процессе работы кэша мостов соответствующий светодиод загорится, что эквивалентно вызову соотвествующей ячейки кэша команд. Если ноль — то звено и соответствующая ему ячейка кэша команд будут пропущенны. Процесс заливки можно повторить, если нужно. Далее с контактов механизма заливки сигнал единицы убирается. Дальше в триггер Run записывается единица, чтобы дать по проводу сигнал подать сигнал для перебора звеньев цепи. Затем нажатием на Button_1 в триггеры Start записывается единица, если звено пропускается — то в ходе работы кэша мостов она останется, если вызовет ячейку кэша команд — то сменится нулём. Чтобы посмотреть симуляцию пошагово нужно в Logisim Evolution снять галочку с «Моделирование включено» и указателем выбора элементов (курсор в виде руки) в триггер Tact установить единицу. Далее нажимать CTRL+I, в результате чего мигнёт первый в очереди светодиод в звене, а в триггер Tact установится значение ноль. Так пока не пройдёт вся цепь. Пропуск звеньев с нулём в триггере осуществляется автономно. После окончания цепи процедуру можно снова нажав кнопку и записав в триггеры Start единицы.

Теперь, после того как мной были устранены все недоработки в схеме, мне остаётся только работа с FPGA, разумеется это в отрезки свободного времени от основной и других дел. Буду рад, если мой опыт окажется полезным кому-то в других решениях. Теперь точно нечего писать кроме результатов работы с FPGA. Всем спасибо за внимание… и понимание, если случайно отнял у них время. Быстрых ответов от меня не ждите — у меня длинный рабочий день и т.п. Да и надеюсь что в комментариях нет нужды, так как очередь Verilog и очередных результатов только подошла.