Ректоры и президенты неожиданно согласились рассказать студентам, что их ждет в микроэлектронике

Мы на Школе Синтеза двадцать суббот учили школьников и студентов проектировать процессоры на FPGA. Для выпуска мы решили пригласить крутых топов, и на наше удивление, откликнулись сразу семеро:

Александр Редькин, гендир и основатель компании Syntacore, которая разрабатывает будущий флагман российcких процессоров для линуксных ноутбуков — суперскаляр с внеочередным исполнением иструкций, совместимый по системе команд с архитектурой RISC-V.

Сергей Сергеевич Шумилин — заместитель директора по науке компании Миландр, российского лидера по разработке микроконтроллеров, пионера лицензирования ядер ARM и надежды российcких пользователей ПЛИС.

Николай Суетин — главный микроэлектронщик фонда Сколково, бывший руководитель R&D Интела в России.

Сергей Михайлович Абрамов — член-корреспондент РАН, руководитель разработки суперкомпьютера СКИФ и других HPC проектов.

Игорь Рубенович Агамирзян — бывший менеджер Микрософта, Российской Венчурной Компании, вице-президент Высшей Школы Экономики и программист.

Александр Тормасов — ректор Иннополиса, Chief Scientist компании Parallels, гуру виртуализации, лектор по компьютерной архитектуре.

Тимур Палташев — известный специалист по архитектуре компьютерной графики, c 25-летним опытом в Silicon Valley и работой с питерским ИТМО.

Вообще мы планировали бОльшую часть времени в субботу разбирать микроархитектурные задачки на верилоге, но раз так, то будем устраивать сессию на тему «лидеры индустрии и академии расскажут, какие следущие шаги предпринять после решения микроархитектурных задачек, чтобы стать лидерами индустрии и академии». И ответят на вопросы.

Это состоится в субботу 23 апреля в Капсуле №2 Технопарка Сколково в 12:00.

Как записаться и что была на двух последних занятиях

Записаться можно у Александра Биленко info@chipexpo.ru. Также неплохо зарегистрироваться на сайте для получения дополнительных материалов в рассылке.

Как вообще появилась Сколковская Школа Синтеза Цифровых Схем? Когда-то лет 10 назад я поехал в МФТИ, который любят сравнивать с MIT, и обнаружил, что в нем нет аналога MIT-шного курса 6.111. Это курс в котором студенты делают всякие цифровые схемы на FPGA, с курсовыми работами по обработке видео, звука, графике итд.

Потом была долгая история, в которой энтузиасты из России, Украины, Калифорнии и Великобритании создавали учебные материалы, и все это в конечном итоге вылилось в школу с ChipEXPO и Сколково. Которая помимо материалов а-ля MIT 6.111, впитала упражнения с дизайном простейшего CPU, трейнинг на тулах для массовых ASIC-ов, курсы Клифа Каммингса и индустриальное ноу-хау.

В течение 20 занятий по субботам ученики изучили:

Язык описания аппаратуры Verilog, методологии проектирования на уровне регистровых передач и основы статического анализа тайминга.

Элементы архитектуры и микроархитектуры процессоров общего назначения, на примере двух реализаций архитектуры RISC-V: простейшая schoolRISCV и промышленная RVfpga.

Маршрут синтеза для FPGA и для ASIC, используя САПР от Intel FPGA, Synopsys, Cadence и Mentor / Siemens EDA.

Приемы проектирования, слабо представленные в учебниках, но широко используемые в индустрии: кредитные счетчики с аппаратными очередями, арбитры, банки памяти, пересечение тактового домена.

Практические занятия по реализации на FPGA цифровых схем, работающих с сенсорами, графикой и музыкой.

Теперь что было на предыдущих занятиях.

Занятие 20. Первый шаг к графическому процессору (GPU)

Вначале речь, которая связывает студенческие упражнения с промышленным GPU:

Зачем нужны графические чипы:

Чем конвейер GPU отличается от конвейера CPU.

Превращение сложной операции в последовательность простых.

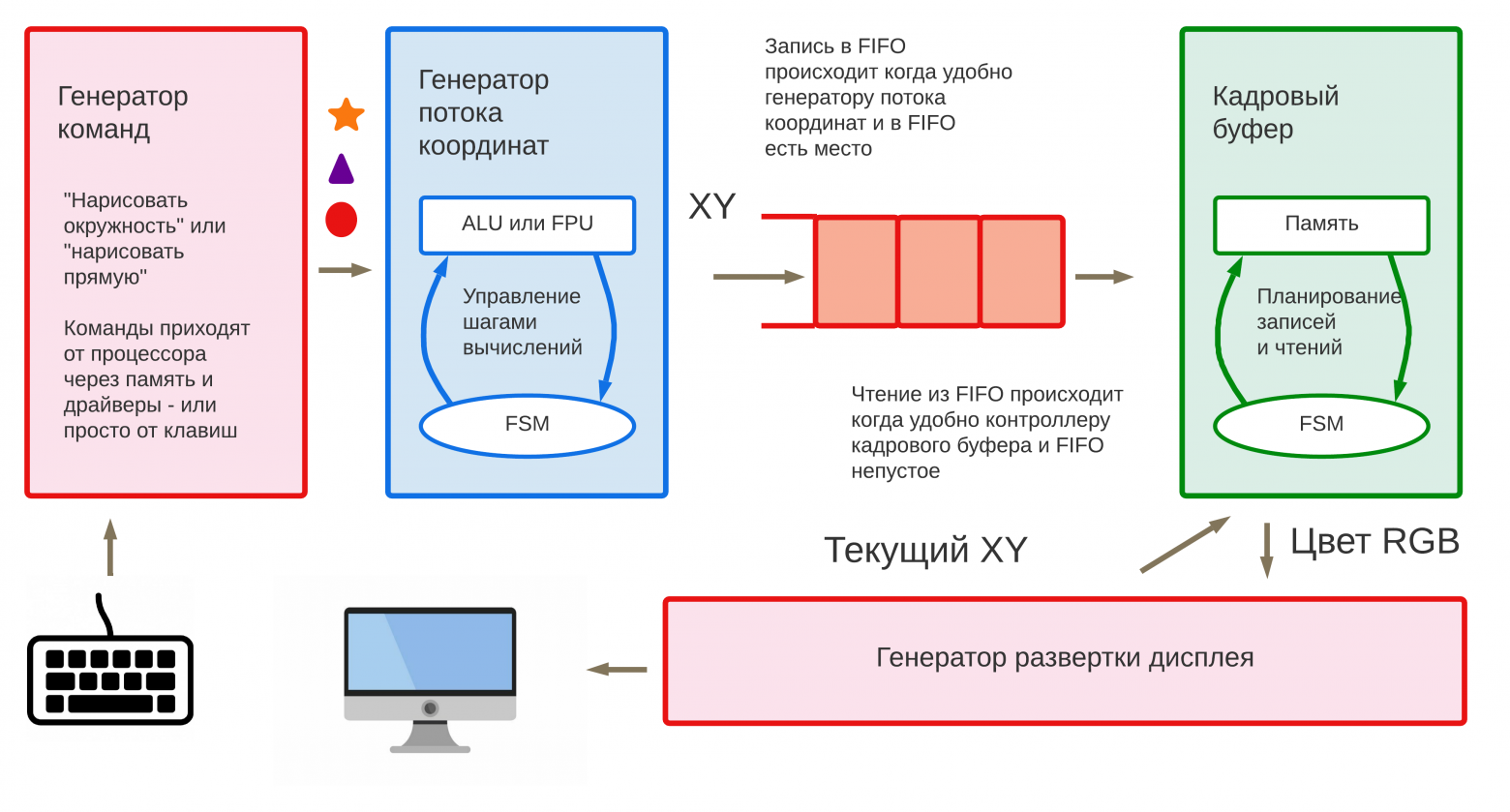

Пример: соединение «генератор команд → вычислитель координат → очередь FIFO → кадровый буфер → логика вывода на экран».

Пример: алгоритмы вычисления координат точек окружности.

Далее разбор примеров от Егора Варламова (МИРЭА) и Дмитрия Смехова.

Где-то на 15-й минуте объясняется идея трехмерной компьютерной графики на пальцах:

Еще приводится ссылка на древнюю статью с описанием 15 алгоритмов рисования окружностей — вы можете сами посмотреть какие из них подходят для реализации на FPGA (статья настолько древна, что код в ней на Фортране — ага!).

До этого было занятие 19, со спичем про реалии работы инженером в электронных компаниях, на позициях RTL дизайнер (Register Transfer Level), DV верификатор (Design Verification) и EDA программист (Electronic Design Automation) в Silicon Valley (впрочем такое же вы найдете в европейских и российких компаниях):

Организация.

1.1. Работа в большой, средней или малой компании, контракторство,

университет или стартап.

1.1. Структура типичной команды разработки: организация по отделам

компании и по блокам чипа.

1.3. Жизненный цикл проекта: от анализа требований рынка до продукта в магазине.Специализация.

2.1. Микроархитектор блока / инженер по проектированию на уровне

регистровых передач.

2.2. Инженер-верификатор / специалист по моделированию.

2.3. Разработчик программ для автоматизации проектирования /

Electronic Design Automation, EDA.

После этого выступил Александр Силантьев из МИЭТ, который разобрал часто встречающиеся задачки с интервью для скрининга и junior позиций (задачки посложнее мы будем разбирать на другой сессии).

После занятия мне поступил запрос выложить рекомендованную литературу, которая на видео не очень хорошо видна. Выкладываю:

Если вы только начинаете, приобретите Харрис & Харрис и Цифровой Синтез. После него стоит приняться за Дональда Томаса, где хорошо разбирается алгоритм симуляции верилога.

К сожалению, в Харрис & Харрис нет многих важных вещей, например арбитров и очередей FIFO. Кое-то есть в учебнике, который используют в Стенфорде (зеленый справа). Например в нем есть skid buffer / double buffer — важный прием для конструирования микроархитектуры. Там же объясняется что skid buffer решает (проблемы тайминга для логики затыков в конвейере).

Также в Х&Х мало описаны арифметические блоки. Эту тематику покрывает учебник справа (он не единственный — по реализации арифметики есть штук пять хороших нишевых учебников).

Также рекомендую полезный сайт под названием RTLery.

Для введения в микроархитектуру CPU лучший современный учебник — это Шен-Липасти слева. Там есть про предсказатели перехода, переименование регистров итд — все хорошо описано и с примерами.

Если же хочется поиграться с полноценной реализацией на верилоге архитектуры RISC-V, я рекомендую книжку справа. Процессор в нем простой — микроконтроллерного класса, с простым статическим конвейером, не как суперскаляры в Шен-Липасти. Но зато этот процессор написан индустриальным дизайнером от сохи (который например проектировал космические версии Z80 и сотню других чипов), а не еще одним студентом. Который еще и дотошно все описал.

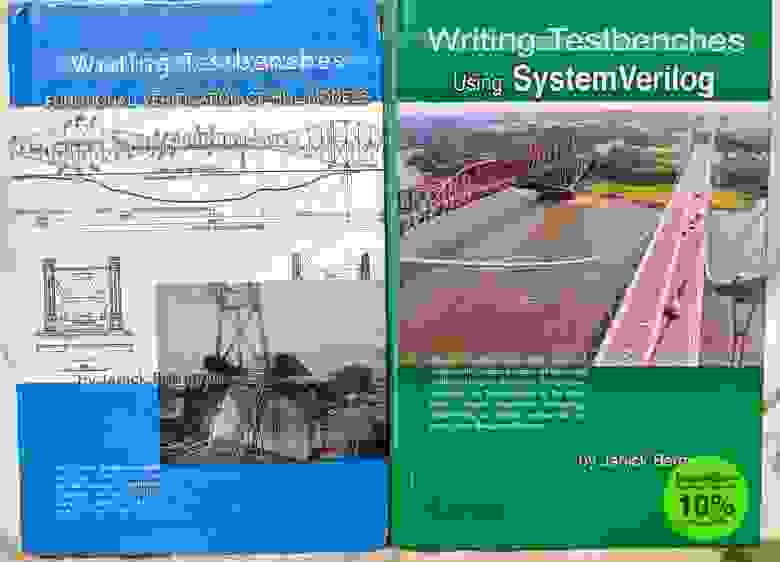

Основы верификации стоит знать не только верификатору, но и RTL-щику, чтобы не зависеть от верификаторов на юнит-тестах. В частности, стоит прочитать вот эту книжку, причем и старое (до coverage driven constrained-random verification), и новое издание (после этих изменений подхода). В первой главе хорошо описана идеология верификации, во второй писание тестового плана, потом разные трюки и индустриальные практики. Для чтения в электричке — самое то.

SystemVerilog верификатору стоит учить по книжке слева.

Отдельно стоит получить представление о UVM по другой книжке, Getting Started with UVM: A Beginner’s Guide by Vanessa R. Cooper. Правда написанный в ней пример драйвера для превращения транзакций в сигналы порочен, так как из этого примера не следует как писать драйверы для конвейерных транзакций, которые занимают несколько тактов (например AXI Write с фазами адреса и данных), но в остальном книжка хороша — абсолютный минимум и вcе понятно.

Книжку справа про assertions читают в основном социопаты. Например, у меня есть знакомый, который провел с этой книжкой (а не с девушкой) рождественские каникулы. Но знать язык concurrent assertions полезно и для верификатора, и для RTL дизайнера — это одна из так сказать стаместок, которые стоит иметь в наборе инструментов (кроме Бена Коэна есть и более легкие тексты). (После того рождества моего знакомого пригласили на интервью в Локхид-Мартин верифицировать чипы для американских ракет)

Вот две книжки, откуда можно черпать идеи. Одна (слева) как писать на верилоге игры. К сожалению, ее автор хоббист, а не писатель верилога на зарплате, поэтому к его коду не стоит относится как к идеалу стиля.

Другая — сборник древних статей уже упоминавшегося выше Джима Блинна. Я уверен, что по графике есть куча более солидных текстов, но объяснение преобразования перспективы от Джима Блинна понравилось мне больше всего.

На этом я свой пост заканчиваю и мы ждем вас всех в субботу 23 апреля в Капсуле №2 Технопарка Сколково в 12:00, насколько вместится в помещение.

Эту девочку зовут Наташа

Эту девочку зовут Наташа