Производители микросхем представили новый стандарт UCIe

Intel, AMD, Arm, TSMC и Samsung представили новый консорциум Universal Chiplet Interconnect Express (UCIe) с целью стандартизации межкомпонентных соединений между чипами с открытым интерфейсом. Участники консорциума стремятся сделать UCIe таким же универсальным, как и другие стандарты (USB, PCIe и NVMe).

UCIe

UCIe

Примечательно, что все производители примут эту технологию вместе с экосистемами x86 и Arm.

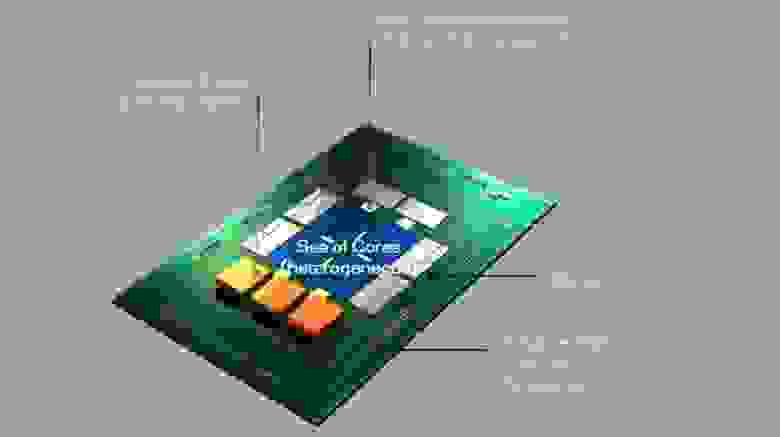

Преимущества чиплетов, такие как снижение затрат и использование различных типов технологических узлов в одном корпусе, хорошо известны и важны, поскольку производители сталкиваются со все более сложными проблемами масштабирования в свете угасающего закона Мура.

Долгосрочное видение чиплетов всегда заключалось в том, чтобы производители микросхем могли разрабатывать свои собственные типы специализированных микросхем, а затем соединять их с готовыми конструкциями других компаний, чтобы сократить время выхода на рынок при одновременном снижении затрат.

Тем не менее, отсутствие стандартизированного соединения между чиплетами привело к широкому спектру настраиваемых проприетарных межсоединений, поэтому современные чипы, безусловно, не всегда совместимы с другими конструкциями. Кроме того, отрасль долгое время страдала от явной нехватки стандартизированного контроля и проверки конструкций микросхем и межсоединений, что делало невозможным создание готовой экосистемы.

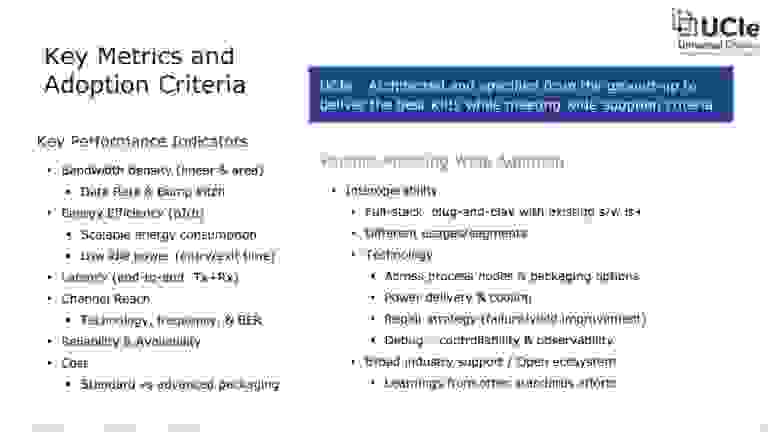

UCIe обеспечит стандартизированное соединение между чиплетами, такими как ядра, память и ввод-вывод, которое выглядит и работает аналогично соединениям на кристалле, а также обеспечивает соединения вне кристалла с другими компонентами. Оно опирается на существующие протоколы, такие как PCIe и CXL.

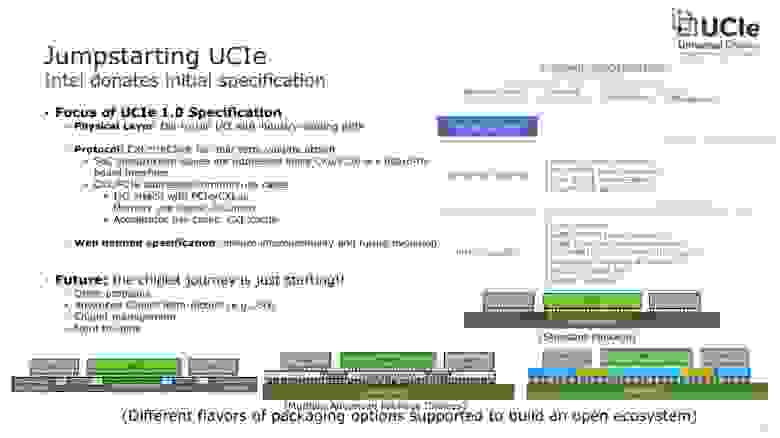

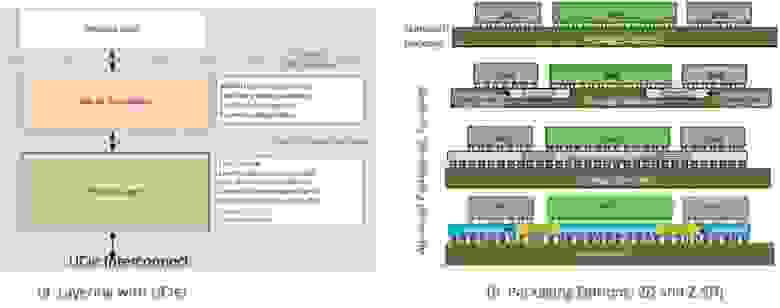

UCIe — это многоуровневый протокол с физическим уровнем и сквозным адаптером. Физический уровень может состоять из всех типов текущих вариантов упаковки от нескольких компаний: стандартной 2D-упаковки и более продвинутой 2,5D-упаковки (Intel EMIB), CoWoS на основе промежуточного устройства от TSMC и подходов промежуточного разветвления (FOCoS-B). В будущем стандарт UCIe также будет расширен до межсоединений 3D-упаковки.

Уровень протокола работает поверх физического уровня, и первоначальная спецификация основана на протоколе PCIe или открытом Compute eXpress Link (CXL, первоначально предоставленном Intel). Протокол PCIe обеспечивает широкую совместимость и гибкость, в то время как CXL можно использовать для более продвинутых соединений с малой задержкой и высокой пропускной способностью, таких как память (cxl.mem), ввод-вывод (cxl.io) и ускорители, такие как GPU и ASIC (cxl .кэш). Хотя спецификация начинается с PCIe и CXL в качестве текущих протоколов, в будущем она будет расширена за счет включения других протоколов.

Intel ранее использовала два IP-блока интерфейса для EMIB, усовершенствованную шину межсоединений (AIB) и UIB. Intel предложила AIB в качестве бесплатного стандарта с открытым исходным кодом в предыдущей попытке создать стандартизированную экосистему чиплетов, но это не получило большого признания в отрасли. Однако UCIe и AIB по своей сути не совместимы, поэтому, хотя Intel продолжит полностью поддерживать текущие реализации AIB, она прекратит все дальнейшие разработки и перейдет на UCIe.

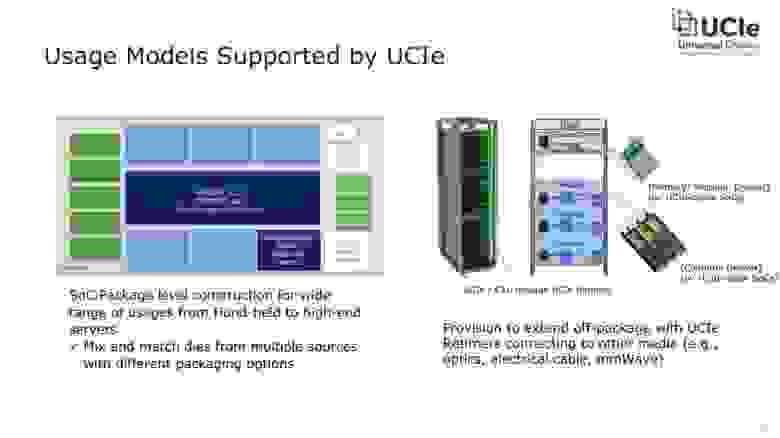

Спецификация UCIe также включает в себя конструкцию ретаймера, которая может расширять соединение за пределами пакета микросхем, обеспечивая оптические и электрические соединения с другими компонентами, такими как объединенная память, вычислительные ресурсы и ресурсы ускорителя. Учитывая высокие показатели производительности, консорциум предполагает, что взаимосвязь в конечном итоге позволит создать такие типы дезагрегированных систем в масштабе стойки, которые индустрия пыталась построить в значительных количествах на протяжении десятилетий.

Соединения кристалл-стойка могут использовать собственный CXL для PCIe для связи (трансляции не требуются), что, возможно, наконец обеспечит задержку и пропускную способность, необходимые для таких конструкций.

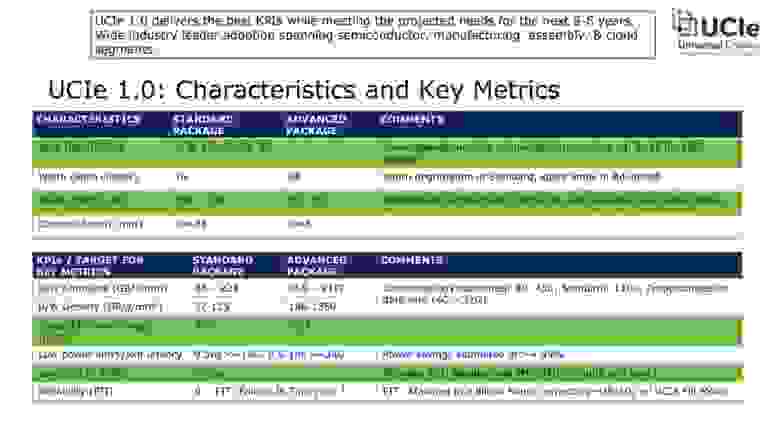

Консорциум разделил работу на два направления: со стандартными методами упаковки 2D и более продвинутыми методами 2.5D (EMIB, CoWoS и т. д.). Естественно, расширенные варианты упаковки обеспечат более высокую пропускную способность и плотность.

Настраиваемые факторы включают скорость передачи данных (диапазон от 4 до 32 ГТ/с), ширину (количество дорожек), шаг выступа (плотность соединений) и охват канала (длина физического соединения).

Для устройств с самой высокой производительностью существует частая проблема в том, чтобы втиснуть как можно большую полосу пропускания с низкой задержкой в наименьшую возможную область. Тем не менее, большинство проектов не требуют такого уровня производительности, поэтому в них используется несколько рычагов.

Например, прогнозы BW Shoreline (ГБ/с на мм) и плотности BW (ГБ/мм^2) основаны на шаге выступа 45 микрон. Тем не менее, спецификация поддерживает шаг выступов до 25 микрон, что увеличивает эти значения в три или более раз. Таким образом, в перспективе можно будет наблюдать до 3,8 ТБ/с пропускной способности на мм^2.

Кроме того, консорциум разработал спецификацию с учетом энергоэффективности, включив в нее расширенные функции, такие как быстрый вход/выход (субнаносекундная шкала) из состояний включения и выключения питания.

В целом, спецификация UCIe направлена на то, чтобы межсоединения на корпусе выглядели как можно более похожими на межсоединения на кристалле, предоставляя при этом множество опций, способные обеспечить практически любой требуемый тип производительности или технологии упаковки. Однако у спецификации UCIe есть конкурент в виде спецификации Open Compute Project Bunch of Wires (BoW). Спецификация BoW предназначена также для демократизации дизайна микросхем и может похвастаться впечатляющими характеристиками производительности, но она не настолько гибкая. Например, BoW предлагает энергоэффективность от 0,7 до 0,5 пДж/бит, в то время как различные рычаги, доступные с UCIe, обеспечивают от 0,5 до 0,25 пДж/бит.

Спецификация BoW поддерживает фиксированную скорость 16 ГТ/с, в то время как UCIe настраивается и может увеличивать ее до 32 ГТ/с. UCIe также лидирует по другим показателям, таким как плотность полосы пропускания (1280 Гбит/с против до 3,8 Тбит/с). BoW ограничивается пакетированием MCP, в то время как UCIe может поддерживать большинство вариантов упаковки 2D и 2,5D.

Стандартизация межсоединений — один из первых шагов к улучшению функциональной совместимости любого устройства. Проект UCIe поддержали AMD, Intel, Samsung, Arm, ASE, TSMC, Google, Meta, Microsoft и Qualcomm. Nvidia в проекте в настоящее время не участвует.

Спецификация UCIe 1.0 уже доступна, и у консорциума также есть веб-сайт с официальным документом и другими ресурсами.