Новый лабник «Цифровой синтез» продолжает книгу Харрисов и помогает сделать видеоигру на FPGA

Новый лабник «Цифровой синтез» продолжает традиции учебника Дэвида Харриса и Сары Харрис «Цифровая схемотехника и архитектура компьютера», скачивания которого завалили британский сайт. Лабник позволяет потрогать руками всю теорию из Харрис & Харрис на плате FPGA, от мигания лампочек до процессора. В лабнике также разобрана концепция конвейерной обработки, без которой вы не пройдете интервью на работу проектировщиком ни в одну микроэлектронную компанию. В конце показан путь от FPGA до ASIC, массовых микросхем, которые стоят в айфонах, теслах и ИИ-акселераторах.

В книжке есть интервью команды из Питера, которую Intel привез в свою штаб-квартиру в Silicon Valley за их победу на конкурсе Innovate FPGA. Книжку «Цифровой синтез» поддержала ведущая компания в автоматизации пректирования микросхем Cadence Design Systems (на фото выше сибирячка Наташа стоит с FPGA платой перед штаб-квартирой Cadence в Silicon Valley — в посте будет ее видео).

Лабник делался под эгидой Высшей Школы Экономики / МИЭМ, при этом разные главы в нем писали преподаватели Московского, Киевского и Самарского университетов, Питерского ИТМО, Черниговского политеха и Университета Калифорнии Санта-Круз (вечернее отделение в Silicon Valley). В создании учебника приняли участие инженеры российских компании IVA Technologies (аппаратный ускоритель ИИ) и ФГУП НПЦАП (отделение Роскосмоса), американских компаний MIPS, Juniper Networks и AMD. Издало учебник ДМК-Пресс.

Учебник годится не только для студентов — его можно использовать для летних лагерей по цифровому проектированию для продвинутых школьников. Разобраться с нуля по тьюториалам в интернете, как работать со средой Intel Quartus II — это нетривиально. А в учебнике это все расписано по шагам. Кроме этого, в нем есть вся теоретическая база, чтобы сделать что-то интересное для школьников, помимо мигания лампочками, которые им быстро надоедают. Интересное — это например видеоигру:

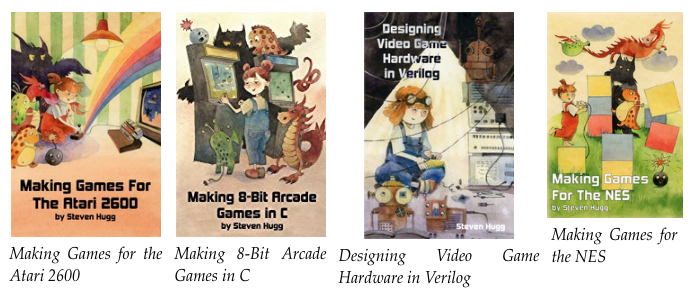

Идея учить верилогу с помощью игр на VGA не нова — такая лаба есть во многих вузах, например в курсе 6.111 Introductory Digital Systems Laboratory Массачусетского Технологического Института (MIT). Также, два года назад вышла книжка Designing Video Game Hardware in Verilog Paperback by Steven Hugg, с довольно развитыми играми с танчиками, гоночными машинками, генератором псевдослучайного звездного неба с помощью LFSR, фрейм-буфером и даже аппаратно-программным интерфейсом. Кроме этого, игры на VGA есть в демонстрациях от производителей ПЛИС Xilinx и Intel/Altera, точнее от их компаний-партнеров — Digilent и Terasic.

В частности в лабе из MIT очень наглядно показано, что все, что нужно сделать для рисования на дисплее — это реализовать в виде схемы функцию, которая в качестве аргумента принимает координаты X и Y точки на экране и возвращает цвет этой точки (RGB). В простейшем случае эта функция — комбинационная, например вот такая функция нарисует шедевр Малевича: «цвет черный (RGB=0,0,0), если x >= 200 и x <= 400 и y >= 200 и y < 400, иначе цвет белый (RGB=1,1,1)». Мы будем далее называть такую схему «миксер», посколько она будет «смешивать» вводы от генераторов разных изображений.

Для генерации самих аргументов миксера X и Y используется простая, построенная на двух счетчиках схема, которая использует тактовый сигнал высокой частоты CLK. Помимо координат X и Y эта схема генерирует сигналы HSYNC и VSYNC для дисплея VGA. Cигналы HSYNC и VSYNC остались со времен электронно-лучевой трубки. Они говорят виртуальному лучу, когда переходить на следующую точку/пиксел на экране по горизонтали, а потом на следующий ряд по вертикали.

В сложном случае миксер использует не только значения своих входов X и Y, но и значения из элементов состояния (D-триггеров и памяти), в которые происходит запись по тактовому сигналу CLK. В этом случае тактовый сигнал тоже входит в миксер. Схемы с тактовыми сигналами и элементами состояния называются последовательностными (эти схемы проходят последовательность состояний, которые четко отделяет друг от друга пульсирующий тактовый сигнал). На последовательностных миксерах можно реализовать движущиеся изображения любой степени сложности.

Вот картинки из MIT-шной лабы (такое же есть в куче других вузов), иллюстрирующие функцию генератора HSYNC/VSYNC, миксера (того самого блока, которые вычисляет RGB как функцию от X/HCOUNT и Y/VCOUNT), а также вывод HSYNC, VSYNC и RGB на экран. На картинке используется переключатель/мультиплексор между тремя миксерами — один рисует полоски, другой прямоугольник, третий — изображение на экране во время игры в пинг-понг:

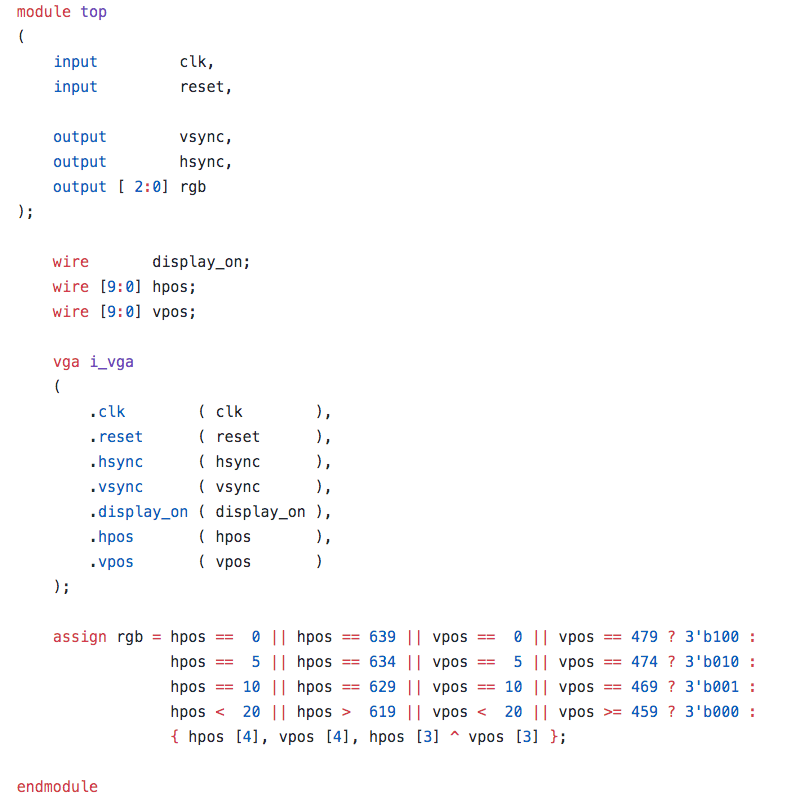

В коде простейший миксер выглядит так. Он рисует разноцветные квадраты из смесей красного, синего и зеленого, а также линии чистых цветов:

Таким способом можно рисовать разнообразные красочные статические изображения. Вот изображения, которые нарисовали школьники на летней школе в Зеленограде сразу после короткой лекции с объяснением, как это делать:

Ну хорошо, школьники могут закодировать функцию RGB (X, Y) и рисовать статические картинки. Но что делать дальше, какой следущий шаг? Мы рассмотрели возможность использовать материалы от MIT, Digilent+Xilinx, Altera+Terasic и Steven Hugg, после чего пришли к выводу, что в чистом виде использовать их нельзя. Вузовские лабы вписаны в вузовскую программу, а материалы от вендоров ПЛИС недостаточно хорошо написаны, а также не содержат подсказок, как менять код в формате летней школы, чтобы школьники изобретали свои игры. У книжки же Стивена Хагга есть два недостатка, которые являются обратной стороной ее достоинств (живости и красочности):

Во-первых, Стивен Хагг по-видимому не работал как Verilog дизайнер в электронной компании, поэтому в его коде есть разные вещи которые бы профессионал верилога так не делал.

Во-вторых, Стивен Хагг реализовал очень визуально привлекательную и легкую в использовании среду разработки и моделирования 8bitworkshop, которая, увы, уходит в сторону от средств, которые используют разработчики в промышленности.

Вообще верилог у Стивена Хагга стоит в одном ряду с программированием процессоров старых 8-битных консолей от Атари и Нинтендо. Таким образом Хагг ориентирован не на тренировку будущих супердизайнеров, а на ностальгантов, ретро-компьютерщиков и других реконструкторов. Разница между его средой и профессиональными средствами проектирования еще больше, чем между средой программирования Ардуино и тулкитами для STM32.

Я конечно не предлагаю сваливать на школьников Cadence SimVision и Synopsys Design Compiler за стотысяч долларов, но школьники вполне могут потянуть бесплатные версии профессиональных тулов Xilinx Vivado, Intel/Altera Quartus II, Mentor ModelSim, а также Icarus Verilog, GTKWave и онлайн-площадку edaplayground.com.

Я перечитал предыдущий абзац и подумал:, а вот Cadence SimVision для летней школы в Зеленограде можно было бы и использовать. Он имхо сделан лучше и удобнее и своего прямого конкурента Synopsys Design Vision Environment (DVE)*, и средств от Mentor Graphics (бесплатного ModelSim и платного Questa), и всех дешевых и бесплатных тулов (IcarusVerilog и т.д.) Если московское отделение Cadence Design System предоставит нам право и поддержку использования их софтвера на летних школах в Зеленограде, лично я буду за интеграции этого в программу школы.

* У DVE например текст в окне исходников глючит/прыгает, когда я запускаю его под Ubuntu. Приходится делать window resize пока он перестает глючить. У SimVision такого нет.

Вот начало тьюториала по SimVision (всего в него входит 22 видео):

Но вернемся назад к играм. Если не Стивен Хагг, то что? Я написал пример простейшей игры, которую использовал на летней школе в Зеленограде. Исходники игры лежат на гитхабе. Выглядит она так:

За две недели школьники разобрались с основными принципами проектирования на уровне регистровых передач и стали делать свои собственные, причем нетривиальные игры:

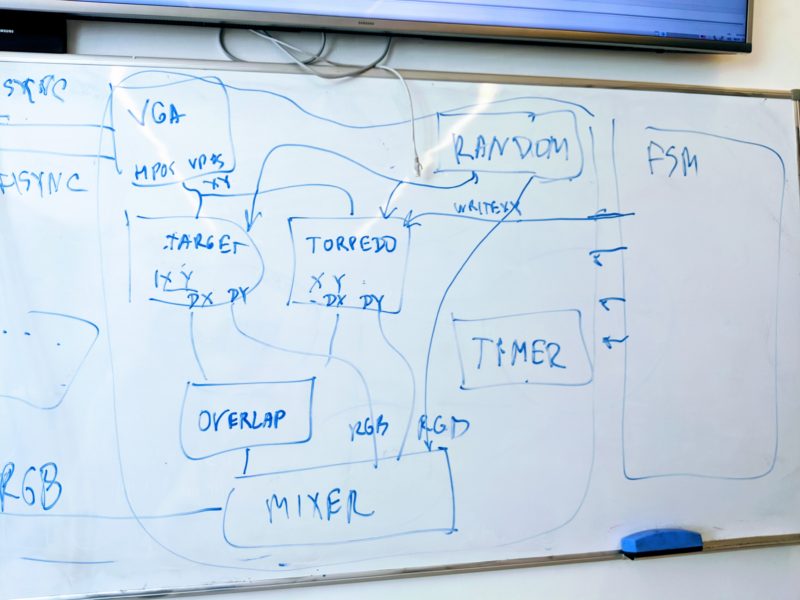

Поговорим о технических деталях игры-примера. Платформенно-независимый модуль игры может быть помещен (instantiated) в обвязке (wrapper) любой FPGA платы, на которой есть VGA порт и две кнопки. Если плата совсем голая, то к ней можно подсоединить переходник для VGA и кнопки через провода GPIO (general purpose input/output). Модуль игры состоит из:

- Генератора развертки VGA.

- Двух параллельно работающих модулей для спрайта торпеды и спрайта цели.

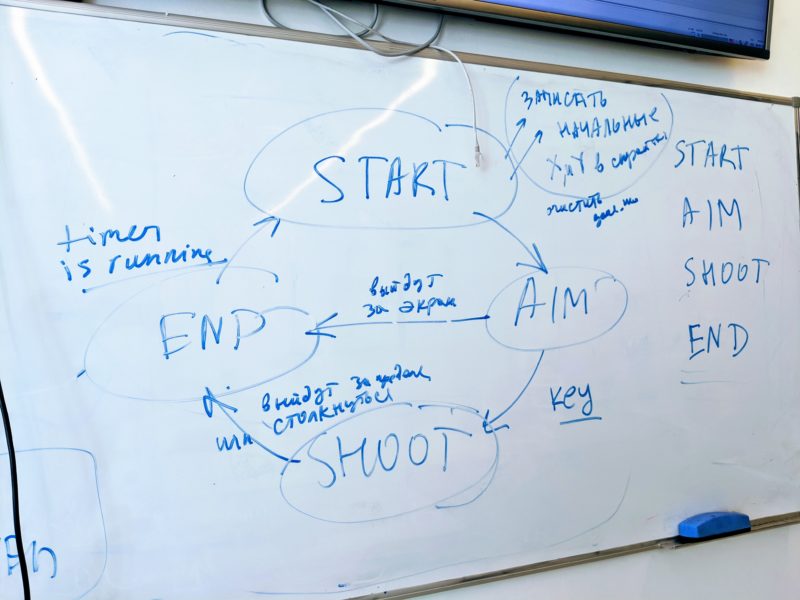

- Конечного автомата для сценария игры, с состояниями «начало», «наведение», «летит», «победа/поражение».

- Модуля, который определяет, столкнулись ли спрайты.

- Таймера для задания длительности визуального эффекта после выигрыша (моргающий малиновый экран) или поражения (желтый экран).

Все эти картинки нужно для следующей школы перерисовать с помощью draw.io или Lucidchart в нормальные микроархитектурные диаграммы:

Еще нужно добавить в материалы школы временные диаграммы, нарисованные с помощью WaveDrom, чтобы показать как работает генератор развертки VGA, а также как вычисляет координаты мини-конвейер тракта данных внутри спрайтов:

И разумеется нужно нарисовать диаграммы конечного автомата. Я сделал дюжину вариантов конечного автомата этой игры, вот на доске — вариант с четырьмя состояниями:

Зачем я сделал много вариантов? Даже с таким простым автоматом можно сравнить разные стили их кодирования на верилоге, а также проиллюстрировать оптимизацию состояний и тайминга. Все это спрашивают на интервью на позицию проектировщика микросхем в Apple, NVidia, Intel, AMD и другие компании. Поэтому эту область нужно знать так, чтобы от зубов отскакивало. Есть несколько хороших статей Клиффорда Каммингса на эту тему:

- Самая новая статья 2019 года: FiniteStateMachine (FSM) Design & Synthesis using SystemVerilog — Part I by Clifford E. Cummings & Heath Chambers.

- Более старая статья, в которой упоминается эффективный стиль кодирования one-hot state machine, который можно встретить в коде процессоров SPARC и MIPS: Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements by Clifford E. Cummings. См. на странице 10: «case (1'b1) // synopsys parallel_case next[READ]: rd <= 1'b1».

- Еще одна старая статья, в которой на странице 9 описывается полезный трюк, при котором выводные сигналы идут прямо из специально закодированного состояния: Coding And Scripting Techniques For FSM Designs With Synthesis-Optimized, Glitch-Free Outputs by Clifford E. Cummings.

Я засинтезировал разные варианты конечного автомата игры с помощью наиболее распостраненного в индустрии тула Synopsys Design Compiler и сделал вот такую табличку. Как мы видим, современная версия DC очень эффективно оптимизирует все стили, так что вытягивать пикосекунды на конечных автоматах можно, но необязательно. Хотя возможно для более сложный конечных автоматов трюки из статей Каммингса будут более критичны:

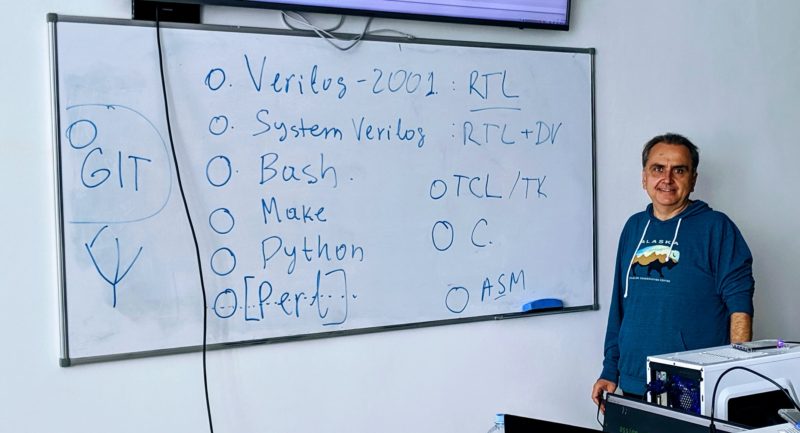

Во время школы в Зеленограде мы также обсуждали, что при проектировании чипов, помимо языков описания аппаратуры Verilog и VHDL, используются и много вспомогательных языков:

Для автоматизации сборки, менеджмента регрессии, извлечения информации из отчетов синтеза и кодогенарации используют Питон, а также bash, make и прочую юниксную/линуксную кухню.

Древний Tcl/Tk является стандартным внутренним языком программ синтеза, симуляции и физического дизайна. На нем пишутся скрипты, которые определяют период цикла тактового сигнала, привязывают имена в коде на Verilog к реальным выводам на FPGA, синтезируют и анализируют группы файлов, добавляют сигналы во временную диаграмму при анализе результатов симуляции или при отладке.

Многие компании еще с 1990-х скрестили немодный сейчас Perl с верилогом. Они используют Perl для препроцессирования и генерации кода на верилоге. Хотя после внедрения Verilog-2001 и SystemVerilog такой гибрид в 90% случаев можно заменить на Verilog-2001 generate и многомерные порты из SystemVerilog, все же остались случаи, когда гибрид перла с верилогом полезен. В частности, если вы используете бесплатные программы, которые не поддерживают SystemVerilog.

C/C++ и библиотеки типа SystemC используют для написания моделей аппаратных блоков на уровне транзакций. Инженеры-верификаторы проверяют блоки, проектируемые на верилоге, против этих моделей.

Если вы работаете в процессорной компании, вам полезно знать ассемблер. Даже если вы не низкоуровневый программист и не верификатор, а проектировщик процессора на уровне регистровых передач (Register Transfer Level — RTL).

Вот ссылки для тех, кого заинтересовало использование перла в качестве препроцессора для верилога:

- G. Spivey. EP3: An extensible Perl preprocessor

- vpp.pl man page

- A Verilog Preprocessor

Пример, как использовать встроенный в верилог перл для соединения 64 портов:

//@ for my $i (0..7) {

//@ for my $j (0..7) {

.D$i$j(P${i}data[$j]),

//@ }

//@ }

Было бы хорошо, если бы кто-нибудь написал универсальные скрипты для моделирования и синтеза примера (необязательно моей игры) на всех основных платформах для синтеза, симуляции, отладки, анализа динамического энергопотребления, физического проектирования, обвязки для всех плат итд. Это можно было бы использовать на школах и семинарах:

Тут у вас может возникнуть вопрос:, а почему я использую на семинарах Linux? Хотя и под Windows есть среды для моделирования и синтеза для FPGA, но в индустрии проектирования массовых чипов Windows не прижился. В начале 1990-х рынок рабочих станций для разработчиков ASIC-ов был поделен между SunOS и HP/UX. Потом электронные компании года три поиграли с Windows NT, но оно не пошло. После этого Synopsys и другие компании проектировочного софта плюнули и перешли на Linux — сначала на Red Hat, потом на SuSE и Ubuntu. Подозреваю, в основном из-за кучи скриптов на перле, C-shell итд, а также из-за удаленной работы разработчиков через telnet и X Window.

Поэтому я для своих семинаров хожу с кучей bootable SSD с Lubuntu, на которых установлен весь нужный софт. При этом я использую legacy boot, но последнее время выяснилось, что все больше компьютеров требуют UEFI boot. По-видимому надо будет сделать bootable SSD с UEFI boot.

Прижимистые компании вместо Red Hat используют CentOS. Возможно многие тулы для проектирования идут и под Debian, но я не проверял.

Для семинаров я используют китайские FPGA платы, одну из которых держит в руках новосибирская девушка Наташа, которая проводит у нас в Silicon Valley тусовки формата Что-Где-Когда.

В марте месяце я гулял по дикой природе Калифорнии вместе с российским бизнесменом Сергеем Зориным, который отвез в Москву десяток плат ZEOWAA, похожих по характеристикам на ту, которую держит в руках Наташа.

Так как из-за коронавируса эти летом семинаров в Зеленограде наверное не будет, я думаю раздать этот десяток плат московским школьникам бесплатно. C двумя условиями:

Перед получением платы вам нужно пройти все три части онлайн-курса «Как работают создатели умных наночипов» («От транзистора до микросхемы», «Логическая сторона цифровой схемотехники», «Физическая сторона цифровой схемотехники»), и получить сертификат. Этот курс мы создали вместе с РОСНАНО, точнее его образовательной дочкой eNano, проектом STEMford.

Помимо привязки упражнений в школе к реальной индустрии, этот курс объясняет многие моменты, которые нужно твердо знать перед тем, как перейти к практическим упражнениям. В частности концепции последовательностной логики, конечных автоматов, логического синтеза, тайминга внутри цикла (без него непонятно как вычислять тактовую частоту схемы) и других. Эти концепции не всегда укладываются в голову сразу, и если их не изучить перед практикой теоретически, то пользы от практики будет не очень много.

После получения платы я ожидаю, что вы сделаете на ней проект, выложите код на гитхаб и напишете про ваш проект пост на Хабре.

Если вы хотите купить в качестве подспорья для такого проекта новую книгу «Логический синтез», то для читателей Хабра у нее есть промокод — Sintez_2020.

В перспективе хорошо было бы слезть с использования китайских плат и сделать дешевую российскую плату для таких упражнений с FPGA, с открытым дизайном. Я приветствую, если вы поделитесь мыслями в комментах о программах для проектирования плат и идеями, как лучше спроектировать и маркетировать такую плату. Для массового использования со школьникам желательно чтобы она стоила не больше $30 или 2000 рублей.

Если вы школьник и заинтересовались проектированием микросхем, вы можете поступать в МИЭТ, ВШЭ МИЭМ, МИФИ, МГУ, МФТИ (в нем подобными упражнениями занимается Никита Поляков, МЭИ, МИСиС, ИТМО, ЛЭТИ, Самарский Университет, некоторые украинские университеты (КНУ, Черниговский НТУ, харьковский ХНУРЭ) и другие вузы. Вот я застал как при мне ремонтировали подход к приемной комиссии МИЭТ в Зеленограде:

А вот как МИЭТ выглядит внутри:

Трудоустроиться там можно кстати прямо напротив МИЭТ в НПО ЭЛВИС, которое занимается умными камерами и чипами для спутников:

Или вы можете приехать в Silicon Valley. Хотите пройти интервью в компании Долины? Упражняйтесь на платах ПЛИС!