Новостной дайджест событий из мира FPGA/ПЛИС — №0010 (2021_03) + конференция FPGA разработчиков

ПЛИСкульт привет, FPGA хаб!

Вебинары

-

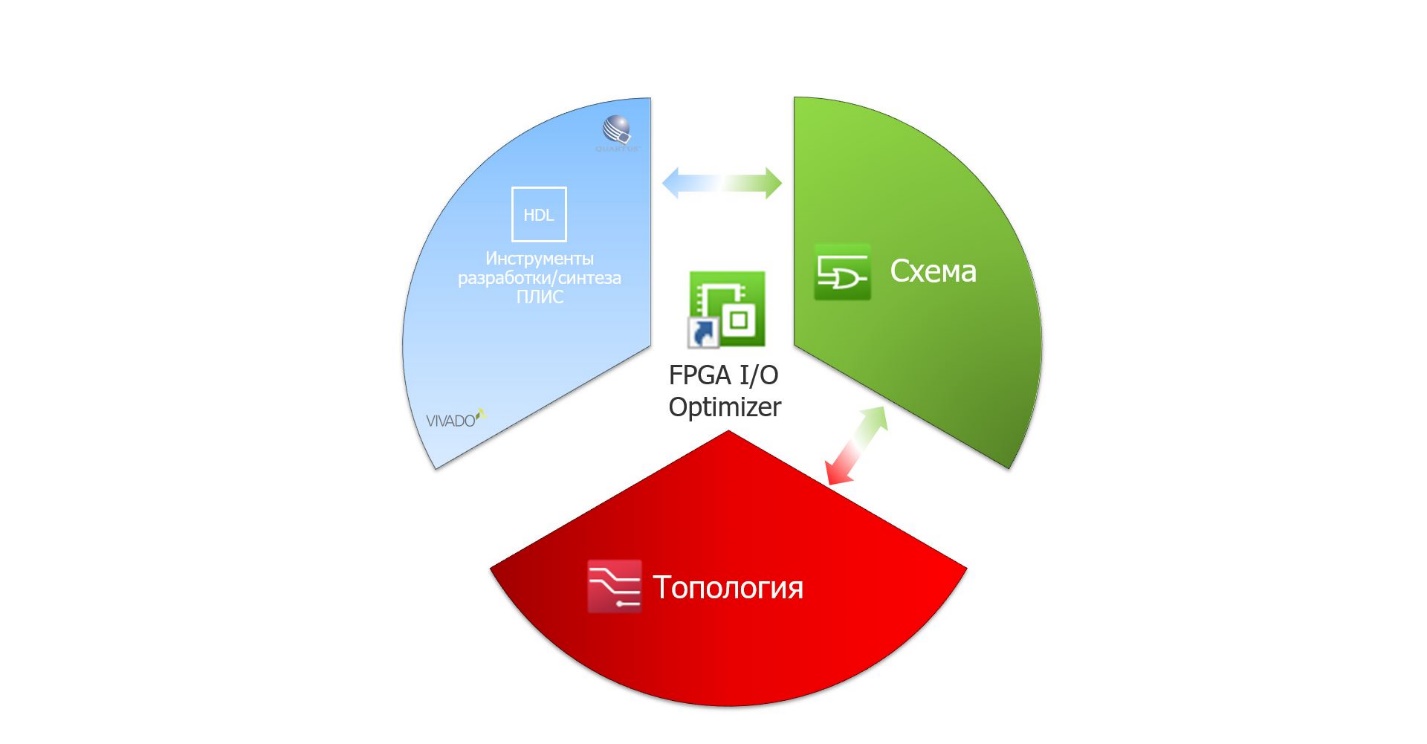

Ускорение процесса проектирования печатных плат с использованием ПЛИС ::

Ускорение процесса проектирования печатных плат с использованием ПЛИС :: Мощность, гибкость и непосредственная доступность ПЛИС привела к тому, что они получили широкое распространение при разработке проектов печатных плат. Очевидно, что благодаря более быстрому выходу на рынок за счет достоинств и высокой производительности, ПЛИС стали перспективной альтернативой по сравнению с более ресурсоемкими IC/ASIC решениями.

-

Xilinx Versal ACAP на русском ::

Xilinx Versal ACAP на русском :: Хочу напомнить, что 25-марта-2021 стартует 2-дневный онлайн семинар на русском по Xilinx Versal ACAP. Часть лекций читают участники нашего чата: Дмитрий Cмехов (@dsmv2011) и Михаил Коробков (KeisN13)

-

Увеличение продуктивности верификации RTL кода в Matlab и Simulink:

Увеличение продуктивности верификации RTL кода в Matlab и Simulink: Проверка RTL кода остается серьезной проблемой в FPGA и ASIC проектах. На этом вебинаре мы увидим, как инженеры с различными навыками могут использовать инструменты MATLAB / Simulink для повышения эффективности и сокращения времени верификации.

-

Plug & Play FPGA программирование для всех ::

Plug & Play FPGA программирование для всех :: IDE, учебные пособия и примеры кода широко доступны для микроконтроллеров. К сожалению, начать изучать технологию FPGA зачастую оказывается намного сложнее.

Миссия VHDPlus — изменить представление о проектирование на FPGA. Это инновационная среда разработки, обеспечивающая более высокий уровень абстракции, ч

-

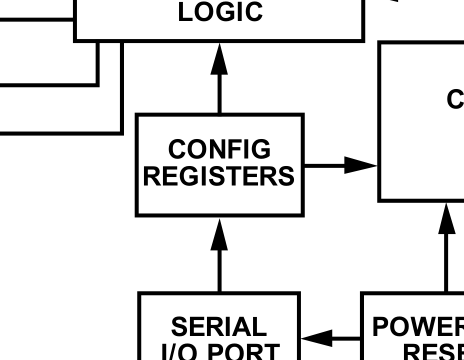

Вебинар по формальной верификации регистров ввода/вывода ::

Вебинар по формальной верификации регистров ввода/вывода :: Даже небольшой компонент, описанный при помощи RTL, может содержать в себе сотни регистров управления и статуса. Как убедиться, что все они работают правильно? Об этом — в предстоящем вебинаре от Siemens.

-

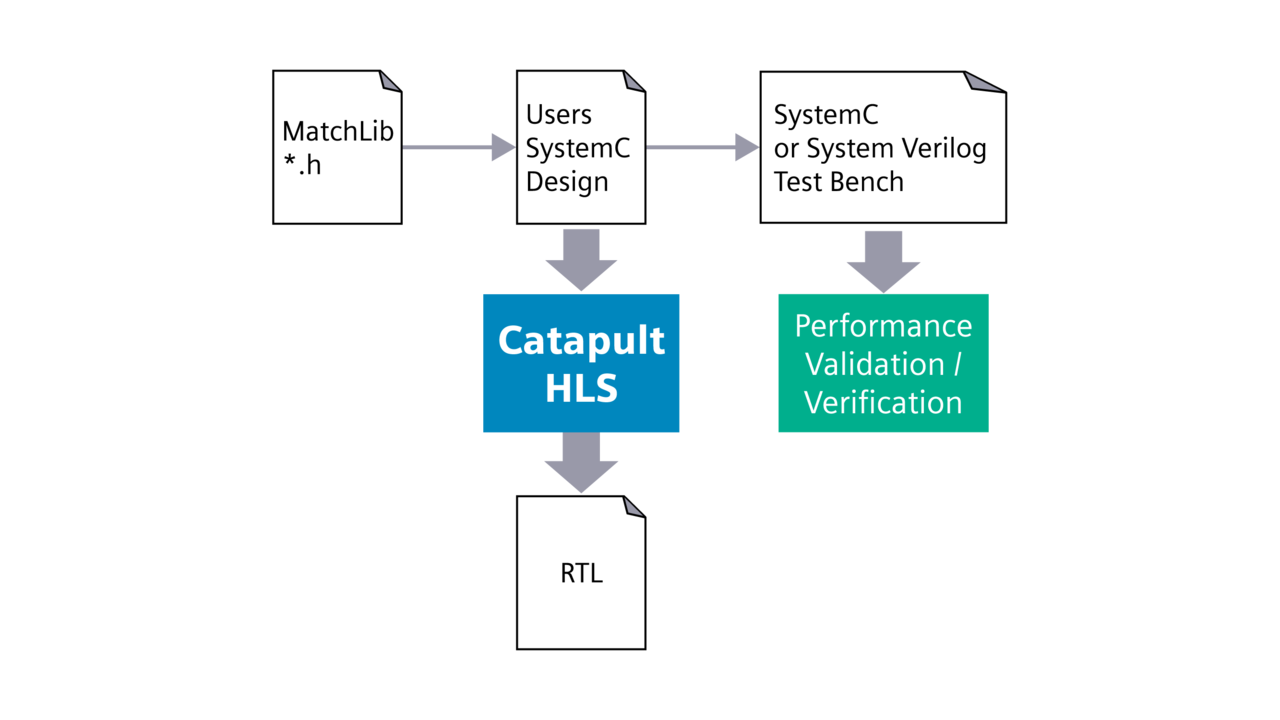

Вебинар по работе с SystemC и MatchLib:

Вебинар по работе с SystemC и MatchLib: Вебинар будет посвящен использованию библиотеки MatchLib SystemC с открытым исходным кодом, первоначально разработанной NVIDIA, для быстрого моделирования и синтеза ускорителя машинного обучения

-

Вебинар по использованию Intel OneAPI от компании Bittware:

Вебинар по использованию Intel OneAPI от компании Bittware: Компании Intel и Bittware проведут вебинар по использованию инструментария Intel oneAPI для FPGA.

В качестве примера будет рассмотрена реализация алгоритма 2D FFT, которая будет запущена на FPGA ускорителе 520N-MX от Bittware.

-

Врываемся в FPGA с Basys3 — воркшоп в двух частях ::

Врываемся в FPGA с Basys3 — воркшоп в двух частях :: Адам Тейлор приглашает на двух дневный воркшоп по основам проектирования на FPGA с использованием инструментов компании Xilinx. Узнайте, как создать встроенную систему на основе FPGA, разрабатывая забавную игру, похожую на Pong / Breakout. На этом воркшопе нам расскажут обо всем, что нужно знать об экосистеме Xilinx, а также рассмотрят все возможности потрясающей платы Digilent Basys3.

-

Начало работы с платформой Xilinx Versal ACAP:

Начало работы с платформой Xilinx Versal ACAP: Компания Xilinx приглашает вас присоединиться к бесплатному двухдневному онлайн-тренингу, организованному совместно Xilinx Customer Training и авторизованными поставщиками обучения Xilinx.

Новинки

-

Разработчикам FPGA для бортовых систем: Aldec добавляет 60+ новых правил проверки RTL-кода ::

Разработчикам FPGA для бортовых систем: Aldec добавляет 60+ новых правил проверки RTL-кода :: Компания Aldec, Inc., один из лидеров в разработке ПО для моделировании VHDL/Verilog и аппаратной верификации проектов FPGA и ASIC, добавила более 60 новых правил HDL в модуль DO-254 программы ALINT-PRO (предназначенной для углубленной проверки качества исходного кода RTL) и внесла несколько улучшений в возможности

-

AXI interconnect IP от компании TrueStream:

AXI interconnect IP от компании TrueStream: Компания Truestream анонсировала IP ядро, выполняющее функцию AXI Intercinnect. Как следует из документации на IP — это интерконнект позволяет решать задачи подключения/арбитража N-to-1. при различных частотных доменах ведущих и ведомого устройства.

-

Xilinx возвращается в борьбу за Cost-optimized рынок:

Xilinx возвращается в борьбу за Cost-optimized рынок: Кевин Моррис опубликовал на портале eejournal.com аналитическую заметку, приуроченную к анонсу компанией Xilinx выхода новых кристаллов семейства UltraScale+ — Artix UltraScale+ и Zynq ZU1.

-

Анонс Artix UltraScale+ и ZU1::

Анонс Artix UltraScale+ и ZU1:: Компания Xilinx анонсировала пополнение своей линейки UltraScale+ в направлении cost-optimized сегмента. Основные технические документы уже обновлены и можно ознакомиться с техническими деталями новинок.

Статьи

-

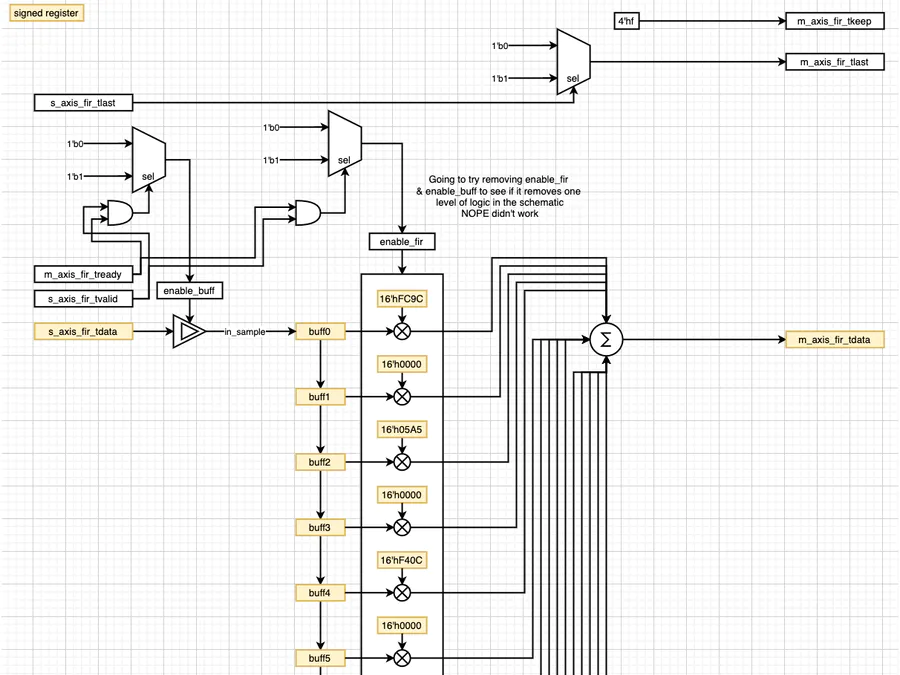

ЦОС на FPGA: простой КИХ фильтр на Veriog:

ЦОС на FPGA: простой КИХ фильтр на Veriog: В нашем телеграм чате в последнее время актуальной стала тема цифровой обработки сигналов на ПЛИС. Whitney Knitter c портала hackster.io как будто бы читая наш чат решила написать руководство по разработке простого КИХ фильтра на FPGA с использованием языка Verilog.

-

10 Ошибок при проектировании на FPGA:

10 Ошибок при проектировании на FPGA: На портале https://hardwarebee.com/ появилась небольшая заметка, сосредоточенная на 10 ошибках, которые допускают FPGA разработчики при проектировании.

-

QuickLogic переоткрывает проектирование на FPGA:

QuickLogic переоткрывает проектирование на FPGA: Еще одна крайне интересная заметка от Кевина Морриса на портале eejournal.com Здесь Кевин обсуждает одну из опенсорс инициативных компаний QuickLogic — одного из немногих производителей, который идет по пути проектирования с открытым исходным и производящего FPGA со встроенным аппаратным контроллером Arm Cortex-M4 и со сверхнизким потреблением QuickLogic EOS S3.

-

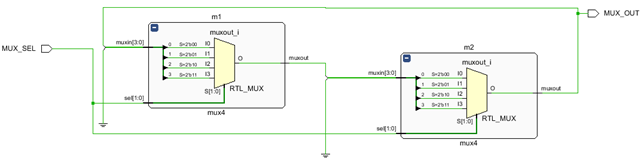

Тренинг по Chisel:

Тренинг по Chisel: Вы когда-нибудь слышали про chisel? Если вы читаете наш телеграм чат — то наверное да. А вот планировали ли вы развиваться в этом направлении и пытаться его изучать?

-

Так что же такое FPGA? ::

Так что же такое FPGA? :: На портале HardwareBee.com появилась небольшая заметка на тему прояснения того, что же такое FPGA? В статье обсуждается отличие FPGA от ASIC, преимущества FPGA, различия между FPGA и CPLD, приложения и архитектура ПЛИС.

-

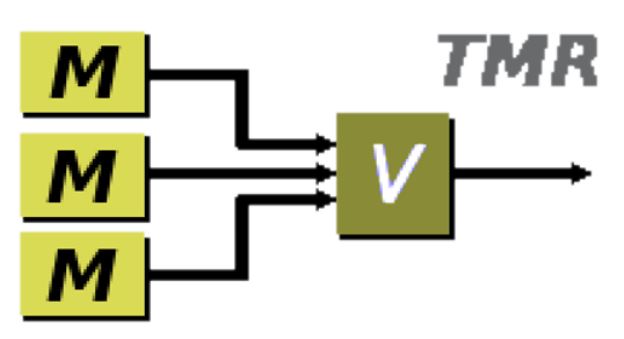

Реализация тройного модульного резервирования (TMR) на MicroBlaze:

Реализация тройного модульного резервирования (TMR) на MicroBlaze: Небольшое руководство о том, как разместить 3 софт-процессора MicroBlaze на отладочной плате Nexys 4 DDR FPGA (Xilinx Artix 7 FPGA) и затем реализовать тройное модульное резервирование для управления GPIO, используя IP-блок Triple Modular Redundancy (TMR)

-

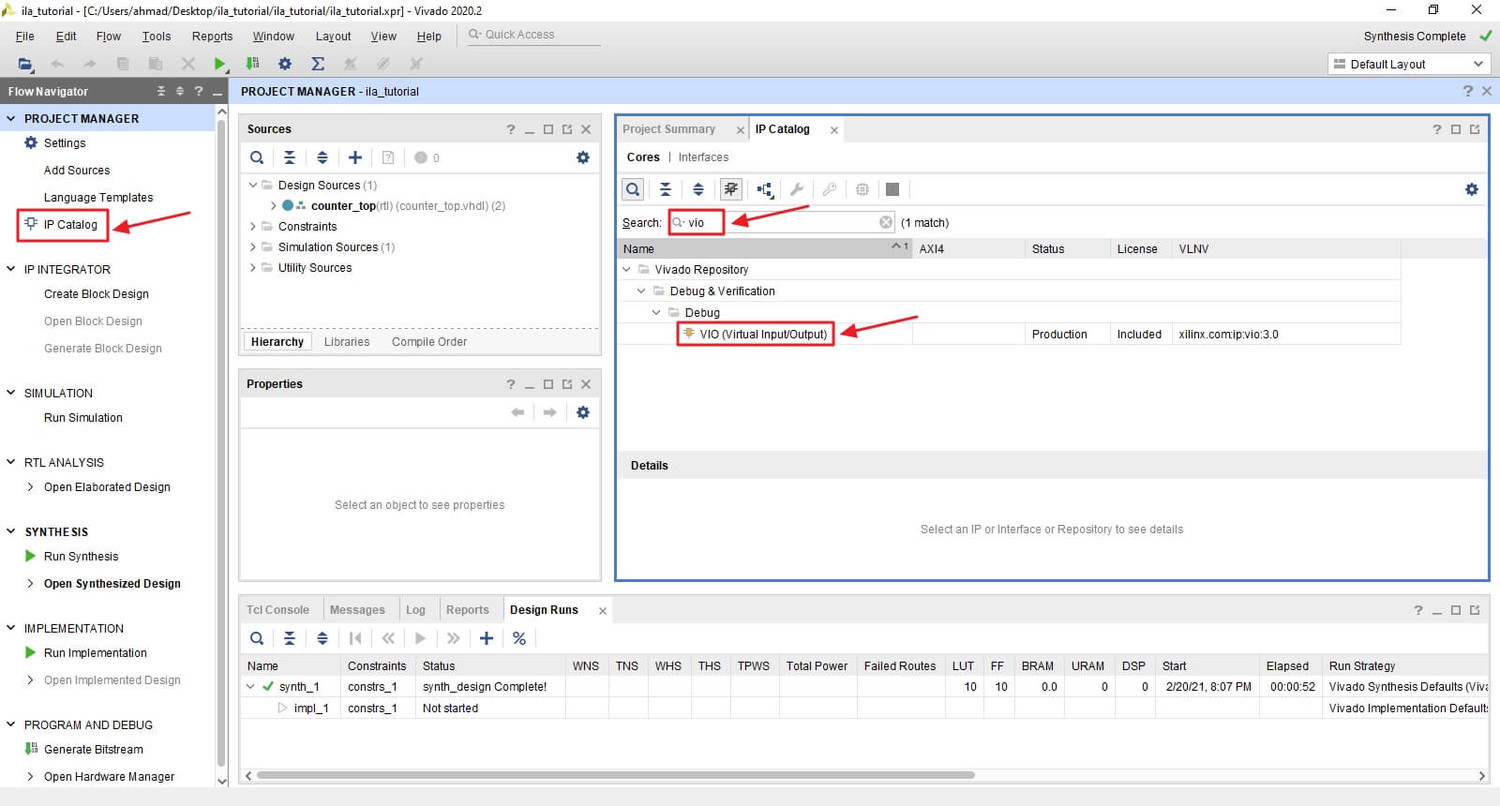

Использование интегрированного логического анализатора (ila) и виртуального ввода-вывода (vio) ::

Использование интегрированного логического анализатора (ila) и виртуального ввода-вывода (vio) :: На портале vhdlwhiz.com появилось новое большое руководство по работе с инструментами отладки Vivado: интегрированными логическими анализаторами (ILA) и блоком виртуальных портов ввода/вывода (VIO).

-

Курсы по RISC-V от The Linux Foundation:

Курсы по RISC-V от The Linux Foundation: Вышло два новых БЕСПЛАТНЫХ курса от RISC-V International && The Linux Foundation

На русском:

-

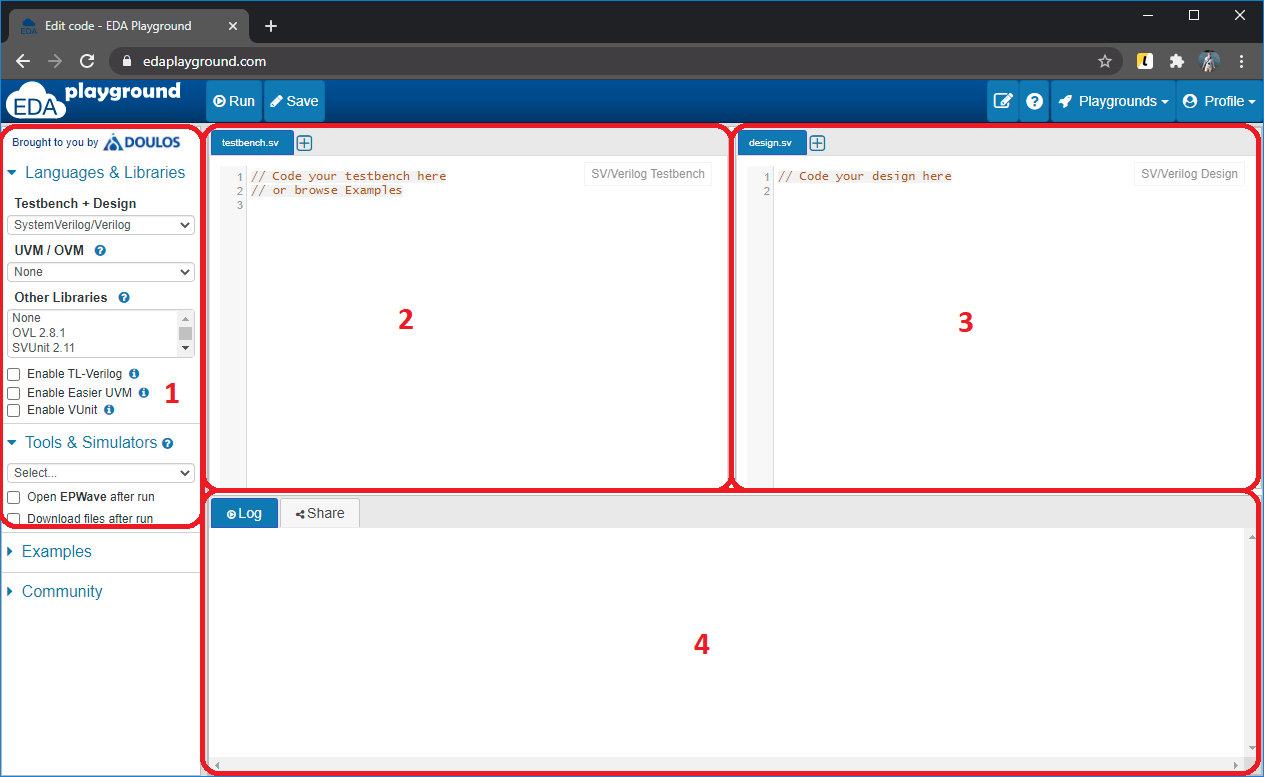

Введение в EDA Playground:

Введение в EDA Playground: Данная записка создана в помощь новичкам в изучении сайта www.edaplayground.com, с помощью которого можно проводить моделирование модулей, запускать различные симуляторы и многое другое.

-

Что нового в VHDL 2019? ::

Что нового в VHDL 2019? :: Эта статья, взята из доклада VHDL 2018: New and Noteworthy. С этим докладом выступил наш коллега Ливен Лемиенгре на DVCON 2018. Поскольку новый стандарт VHDL был утвержден и опубликован в 2019 году, все ссылки на 2018 год в этой статье были заменены на 2019 год

-

Асинхронная работа с libusb 1.0::

Асинхронная работа с libusb 1.0:: Несколько статей назад мы рассмотрели методику работы с USB-устройством при помощи библиотеки libusb. Данные в устройстве у нас формировались по таймеру, поэтому мы были не просто уверены, что рано или поздно они придут к нам, но даже могли предсказать, через какой срок это произойдёт. Однако в анализаторе (который является конечной целью разработки) данные идут непредсказуемо. Будут данные или нет — зависит от поведения объекта контроля.

-

Прикоснемся к магии или как я вступил в ряды MISTического общества ::

Прикоснемся к магии или как я вступил в ряды MISTического общества :: Ниже предложен рецепт приготовления деликатеса, позволяющего Вам попробовать различные 8 и 16-битные приставки и компьютеры. Основное же блюдо для меня miniMIG — Amiga core с графикой OCS/AGA/RTG и CPU до 68020 в 20 раз быстрее стандартной A600.

Стримы

Обучающие видео

Вакансии

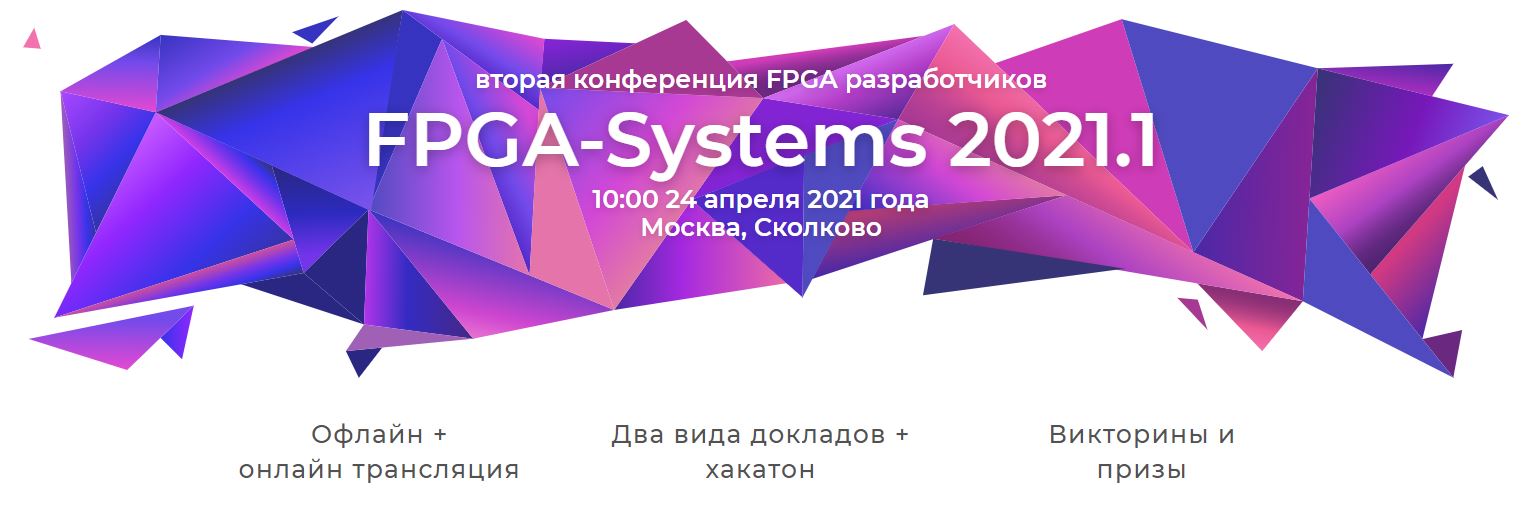

Конференция FPGA разработчиков

Осталось совсем чуть-чуть до нашей второй встречи FPGA разработчиков, которая пройдет 24 апреля 2021 в формате конференции. Еще можно успеть зарегистрироваться:

- Онлайн и офлайн участие

- 5 полноформатных докладов

- 3 доклада «карапули» — узнайте больше о формате здесь

- хакатон + викторины с призами

Предыдущие выпуски новостного дайджеста

Вы можете помочь в наполении контентом следующего номера новостного дайджеста по FPGA/ПЛИС. Присылайте ссылки на актуальные материалы в личку или оставляйте их в комментариях.