ИИ проектирует микросхемы быстрее и лучше людей

Инженеры Google Brain обучили алгоритмы создавать дизайн микросхемы. Нейросети справляются с проектированием всего за шесть часов и делают это лучше, чем белковые специалисты.

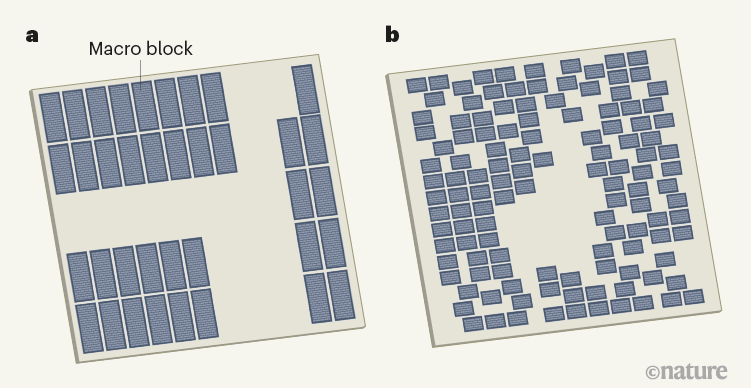

а) Процессор Ariane RISC-V. Микросхема составлена специалистами-людьми. Расположение её элементов считается хорошим: инженеры плотно упаковали 37 макроблоков в выровненные строки и столбцы, оставив место для размещения других компонентов. b) Другая вариация Ariane, созданная ИИ. Решения RL значительно отличаются от решений специалистов, но полученная схема не менее жизнеспособна.

а) Процессор Ariane RISC-V. Микросхема составлена специалистами-людьми. Расположение её элементов считается хорошим: инженеры плотно упаковали 37 макроблоков в выровненные строки и столбцы, оставив место для размещения других компонентов. b) Другая вариация Ariane, созданная ИИ. Решения RL значительно отличаются от решений специалистов, но полученная схема не менее жизнеспособна. Современная разработка дизайна микросхем основана на сочетании автоматизированных методов и ручной обработки. Система автоматизированного программирования радиоэлектронной аппаратуры значительно экономит время, но инженерам всё ещё приходится планировать расположение блоков на кристалле. В итоге разработка дизайна микросхемы в зависимости от размера занимает до нескольких недель.

В новом исследовании инженеры Google Brain научили ИИ самостоятельно проектировать микросхемы и сравнили итоговый результат с работами специалистов.

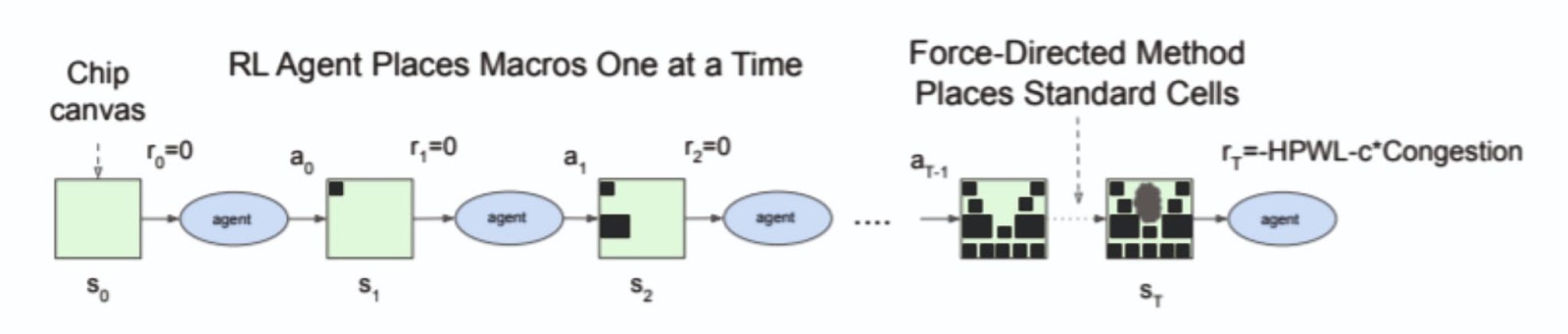

Исследователи применили подход глубинного обучения с подкреплением к проблеме размещения , в котором алгоритмы обучения с подкреплением последовательно размещают макросы на схеме. Когда макросы размещены, на данные воздействуют силовые алгоритмы визуализации графов.

Инженеры сформулировали задачи RL через марковские процессы принятия решений:

«состояние»: каждое возможное размещение элементов на холсте чипа;

«действие»: набор всех местоположений в дискретном пространстве холста, на которые макрос может быть помещён без нарушения жёстких ограничений на плотность или блокировки;

«переход состояния»: распределение вероятностей по следующим состояниям;

«вознаграждение»: вознаграждение равняется нулю для всех действий, за исключением последнего, где вознаграждение представляет собой отрицательную взвешенную сумму длины прокси-провода и перегрузки, с учетом ограничений плотности.

В исходном состоянии s0 у алгоритма есть пустой холст микросхемы и неразмещённый список объектов. sT обозначает микросхему с размещёнными объектами. Таким образом, T — это общее количество объектов, t — промежуточное. На каждом этапе t начинается с st, выполняет действие at, прибывает в новое состояние st+1, получает вознаграждение rt от среды (0 для t < T и отрицательное для t = T). Алгоритм размещает блоки в порядке уменьшения размера.

Через повторяющуюся последовательность состояний, действий и вознаграждений нейросеть постоянно учится и улучшает показатели скорости с каждой новой схемой. Всего в ходе исследования ИИ учился на 10 тысячах дизайнов. Для обновления параметров программы обучения с учётом совокупного вознаграждения за каждое размещение инженеры использовали алгоритм обучения с подкреплением Proximal Policy Optimization.

Исследователи отмечают, что существует множество возможностей для доработки алгоритма, например, оптимизация выбора строк и столбцов при размещении размещении макросов. Инженеры Google Brain планируют заняться его доработкой и в ближайшее время выложить исходный код в открытый доступ.

Несмотря на большое поле для доработок, алгоритм уже генерирует дизайн микросхемы менее чем за шесть часов по сравнению с несколькими неделями у специалистов. Сформированные алгоритмом дизайны либо схожи по качеству с ручной сборкой, либо превосходят её. Кроме того, тайминги у сформированных ИИ дизайнов лучше, чем у дизайнов, созданныхспециалистами-людьми.

В апреле прошлого года исследователи разместили препринт статьи на arXiv. Итоговые материалы исследования опубликованы 9 июня этого года в статье «A graph placement methodology for fast chip design»в журнале Nature DOI: 10.1038/s41586–021–03544-w.