Микроархитектура Zen 2: вот почему мы ждём Ryzen 3000

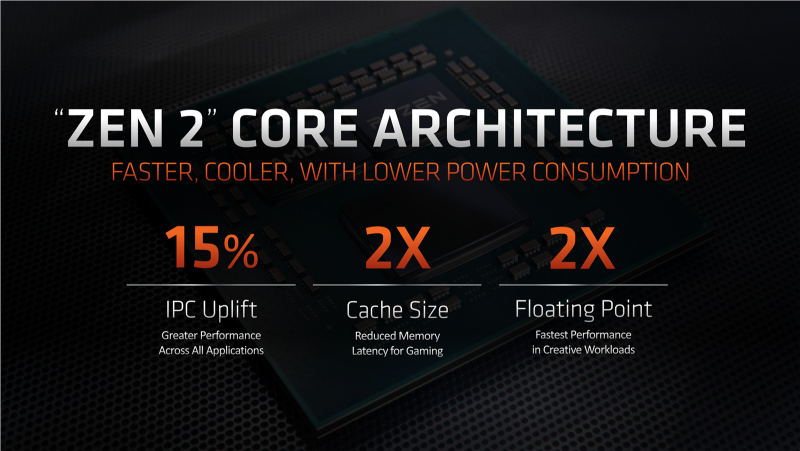

Через две недели с небольшим нас, по всей видимости, ожидает чудо. Такой вывод можно сделать, если обобщить все те предположения, которые высказывают пользователи в ожидании предстоящего анонса процессоров Ryzen третьего поколения. Но даже самые смелые высказывания о том, будто бы во второй половине года на рынке процессоров для ПК нас ждёт смена лидера (по производительности), нельзя назвать полностью беспочвенными. Ещё в начале года, на выставке CES 2019, компания AMD пообещала, что её процессоры нового поколения увеличат удельное быстродействие (при неизменной тактовой частоте) как минимум на 15%. А теперь мы узнали, что к этому приложится заметный рост тактовых частот, кардинальное увеличение числа вычислительных ядер и снижение тепловыделения.

Каждое из этих обещаний в отдельности уже кажется как минимум очень смелым. Но чтобы всё сразу?! Тем не менее всё это возможно. На прошедшем в рамках выставки E3 2019 специальном мероприятии Next Horizon компания AMD подробно объяснила, как так вышло, что микроархитектура Zen 2, которая изначально должна была стать банальным переводом Zen на рельсы 7-нм техпроцесса, смогла оказаться настоящим прорывом, имеющим шансы перевернуть весь процессорный рынок.

С момента выхода первых процессоров с микроархитектурой Zen прошло чуть более двух лет. За это время AMD уже успела выпустить промежуточное поколение микроархитектуры, Zen+. Однако в нём мы не увидели практически никаких улучшений. Суть прошлого обновления фактически свелась к переходу с 14-нм на 12-нм производственную технологию, да и только. Новая микроархитектура Zen 2, встреча с которой нас ожидает в июле, вновь предполагает смену техпроцесса — с 12 нм на 7 нм — с одновременной сменой производственного подрядчика: теперь CPU компании будет изготавливать не GlobalFoundries, а TSMC. Но это далеко не всё: вместе с техпроцессом кардинально меняется и масса других вещей.

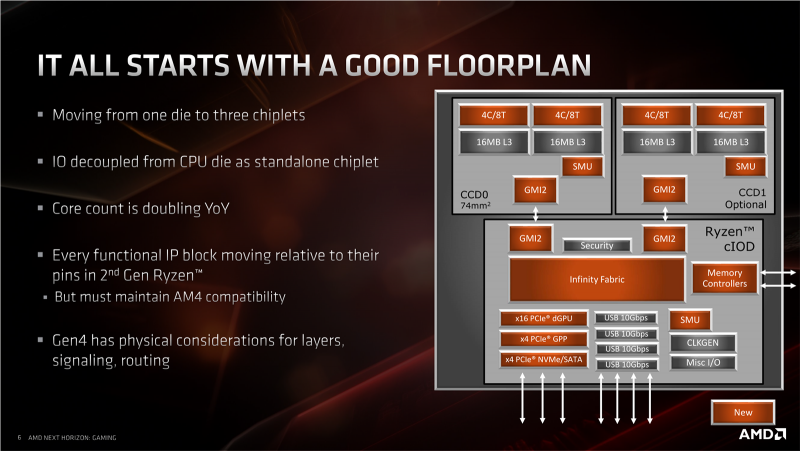

Чтобы понять, насколько Ryzen 3000 будут непохожими на своих предшественников, достаточно посмотреть на любую фотографию этих процессоров со снятой теплорассеивающей крышкой. Одного взгляда будет достаточно, чтобы понять: процессоры AMD уходят от использования монолитного полупроводникового кристалла. Ядра в них распределены по нескольким полупроводниковым кристаллам — чиплетам, также в отдельный чиплет будут вынесены и все контроллеры ввода-вывода. К этому стоит добавить, что одновременно с внедрением коренных изменений в конструктив процессоров AMD переработала внутреннее устройство вычислительных ядер и позаботилась о том, чтобы устранить основные узкие места прошлых CPU с микроархитектурами Zen и Zen+.

Кроме того, с приходом Ryzen 3000 изменения затронут и всю экосистему, в которой будут работать такие процессоры. Совместимость новинок с традиционным разъёмом Socket AM4 при этом сохранится, но полностью все их преимущества можно будет почувствовать лишь в новых материнских платах, которые смогут обеспечить поддержку интерфейса PCI Express 4.0.

Все многочисленные улучшения и оптимизации, сделанные в процессорах поколения Zen 2, заслуживают явно большего, чем простого перечисления. Поэтому по итогам мероприятия AMD Next Horizon, на котором смог побывать представитель нашего сайта, мы решили подготовить отдельный обстоятельный материал и подробно проанализировать, почему Zen 2 — это действительно круто.

⇡#Технология 7 нм — ключ ко всему

Цели, которые ставила перед собой компания AMD во время работы над новой микроархитектурой Zen 2, были вполне очевидными. Основная задача состояла в улучшении производительности процессоров как для десктопов, так и в серверном сегменте, при обязательном сохранении преемственности и совместимости с имеющимися платформами. Иными словами, речь шла о дальнейшей масштабируемости имеющихся процессорных семейств Ryzen и EPYC и комплексном улучшении их потребительских качеств.

Прочный фундамент под дизайн Zen 2 должен был подвести новый технологический процесс. При переходе от 14- к 12-нм нормам, который произошел в апреле прошлого года, процессоры Ryzen лишь немного выиграли в тактовых частотах и смогли довольно незначительно нарастить свою удельную производительность. Но свежий техпроцесс с разрешением 7-нм должен был катализировать куда более существенный прогресс в улучшении всего набора потребительских характеристик. В силу того, что давний производственный партнёр AMD, компания GlobalFoundries, отказался от освоения 7-нм технологии, чипмейкеру пришлось переориентироваться на сотрудничество с TSMC. И в конечном итоге AMD явно не прогадала. В пользу этого говорят числа: базовый процессорный строительный блок — четырёхъядерный комплекс CCX (Core Complex) с L3-кешем объёмом 8 Мбайт — при производстве по 12-нм техпроцессу GlobalFoundries имел площадь 60 мм2. Подобный комплекс Zen 2 с четырьмя усовершенствованными ядрами и вдвое более вместительным, 16-мегабайтным L3-кешем, произведённый на TSMC по 7-нм техпроцессу, занимает почти вдвое меньшую площадь — 31,3 мм2.

Полный процессорный кристалл (чиплет) в Zen 2, как и раньше, формируется из двух CCX. То есть он содержит восемь ядер и кеш-память третьего уровня объёмом 32 Мбайт. При этом суммарная площадь такого кристалла составляет всего 74 мм2, что существенно меньше 213 мм2, которые занимает кристалл процессора с дизайном Zen/Zen+, например, того же Ryzen 7 2700X. Столь заметный выигрыш в плотности размещения транзисторов открыл перед разработчиками AMD широкие возможности по усовершенствованию микроархитектуры, которое могло бы быть проведено без какого-либо существенного ущерба для себестоимости новых процессоров.

Ещё в начале этого года компания AMD объявила о том, что микроархитектура Zen 2 обеспечит 15-процентное преимущество в производительности по сравнению с Zen+ за счёт одних только микроархитектурных улучшений, то есть на одинаковой тактовой частоте. Однако массу преимуществ дал и новый прогрессивный полупроводниковый процесс. Например, при одинаковом энергопотреблении для Zen 2 обещана как минимум в 1,25 раза более высокая производительность, чем у предшественников, а при одинаковом быстродействии новые процессоры должны быть чуть ли не вдвое экономичнее. Более того, AMD не стесняется даже говорить о том, что в отдельных ситуациях преимущество новых процессоров Zen 2 будет составлять более 75% по сравнению с прошлыми Zen+ того же класса и более 45% по сравнению с равноценными решениями конкурента.

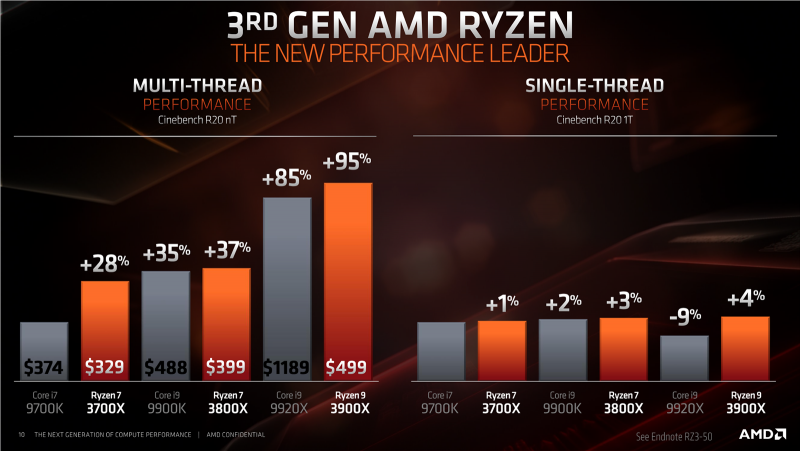

Безусловно, все эти выкладки ещё должны будут пройти проверку на прочность независимыми тестами и обзорами, которые выйдут 7 июля. В рамках же своего мероприятия AMD активно оперировала показателями Cinebench R20, которые говорят о том, что если сравнивать Zen 2 и процессоры Intel с аналогичным количеством ядер, то предложения AMD выигрывают как по однопоточной, так и по многопоточной производительности, а также по энергопотреблению и по цене.

Один лишь пример: согласно данным AMD, старший восьмиядерный Ryzen 7 3800X с ценой $400 очень близок к 500-долларовому восьмиядерному Core i9–9900K в однопоточном и многопоточном рендеринге, но при этом его энергопотребление сравнимо с потреблением Core i7–9700K.

⇡#Ядра Zen 2: «тик» и «так» одновременно

Согласно первоначальному плану, микроархитектура Zen 2 должна была представлять собой простой перенос старого дизайна Zen на новый техпроцесс. Однако позднее, анализируя слабые места своих первых поколений процессоров Zen и Zen+, инженеры AMD приняли решение по возможности подрихтовать и базовую микроархитектуру. И надо сказать, этот план, судя по всему, отлично сработал. Несмотря на то, что в Zen 2 нет никаких кардинальных переделок, рост IPC (среднего числа выполняемых за такт инструкций) на 15% — прекрасная иллюстрация того, что всё было сделано правильно.

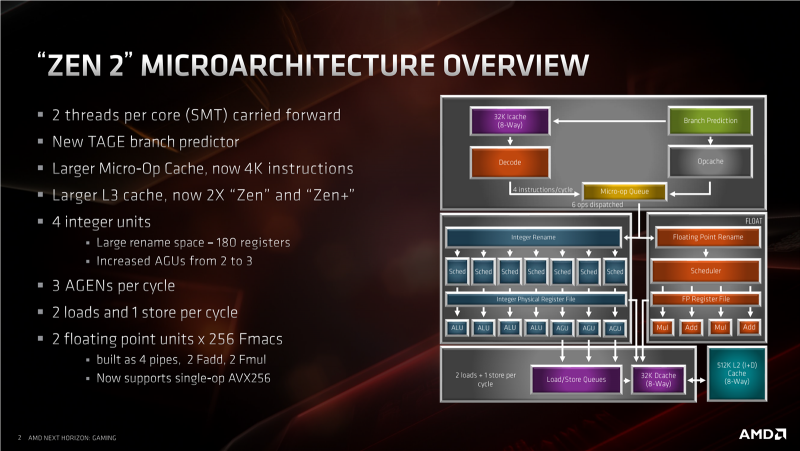

В то же время нужно понимать, что Zen 2 — микроархитектура, очень похожая на оригинальную Zen/Zen+. Все базовые элементы процессорного ядра остались неизменными, а переделки касаются лишь повышения эффективности имеющихся функциональных блоков. Соответственно, внутренняя конфигурация ядра не изменилась: оно способно декодировать до четырёх инструкций и исполнять до шести инструкций за такт. Кроме того, осталась неизменной и поддержка технологии SMT: каждое ядро Zen 2 может исполнять по два потока одновременно.

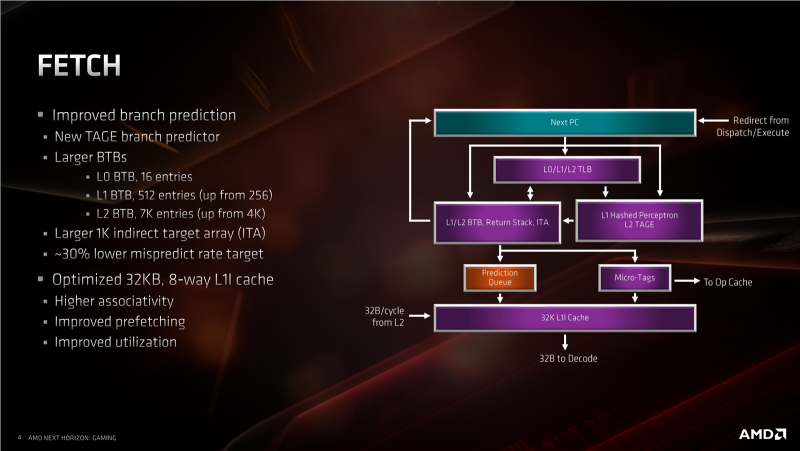

Что же поменялось? Как обычно и бывает при работе над совершенствованием имеющихся микроархитектур, первым местом приложения сил инженеров стал блок выборки инструкций и предсказания переходов. Впрочем, здесь изменения не очень явные, поскольку в основе этого блока продолжает лежать «нейронный» алгоритм, основанный на использовании перцептрона. Хотя в целом такая схема даёт не очень впечатляющие результаты, при работе с буфером целей ветвления первого уровня она обеспечивает хорошую энергоэффективность, поэтому AMD не стала от неё отказываться и просто добавила к ней дополнительный многоступенчатый статистический механизм TAGE (Tagged geometric), работающий с буфером целей ветвления второго уровня.

Одновременно были увеличены и размеры буферов целей ветвления. Таблица первого уровня в Zen 2 включает 512 записей вместо 256, а второго уровня — 7К записей вместо 4К. Что касается нулевого уровня, то соответствующий буфер, как и раньше, включает 16 записей, но зато массив адресов косвенных переходов расширился до 1K записей. Иными словами, в новой микроархитектуре переходы прогнозируются явно лучше, чем в первоначальных Zen/Zen+. А это значит, что ситуации, когда процессор должен полностью сбрасывать исполнительный конвейер из-за неправильно предсказанного перехода, будут случаться гораздо реже.

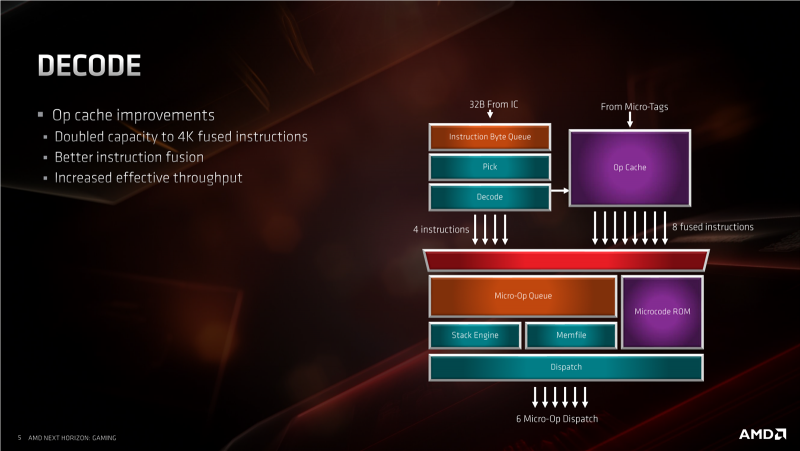

Другим усовершенствованием Zen 2 стало то, что AMD решила существенно перераспределить ресурсы, занятые кешированием инструкций. Кеш микроопераций, в котором хранятся уже декодированные x86-инструкции, был увеличен вдвое — до 4096 записей. При этом классический кеш инструкций первого уровня, в котором сохраняются команды до их декодирования, напротив, сократился. В то время как раньше его объём составлял 64 Кбайт при 4-канальной ассоциативности, в Zen 2 он был урезан до 32 Кбайт с одновременным увеличением степени ассоциативности до 8.

Моделирование, проведённое AMD, показало, что такие изменения положительно сказываются на производительности. И если судить по произошедшему росту IPC, это действительно так. Любопытно, что в результате изменений в размерах кеш-памяти, Zen 2 стали процессорами с самым вместительным кешем микроопераций. Например, в микроархитектуре Skylake этот кеш рассчитан на 1,5К операций, в то время как в Sunny Cove инженеры Intel расширили его всего до 2,25К операций.

Изменения во входной части исполнительного конвейера не повлекли за собой никаких существенных перемен в организации работы планировщиков. Как и раньше, декодер Zen 2 способен поставлять по четыре инструкции за такт и вместе с кешем микроопераций, из которого может поступать до восьми связанных инструкций, они заполняют очередь микроопераций, из которой инструкции выбирают два планировщика: один для целочисленных операций, другой — для операций с числами с плавающей точкой. При этом целочисленный планировщик может отправлять на исполнение по шесть микроопераций за такт, а вещественночисленный — по четыре.

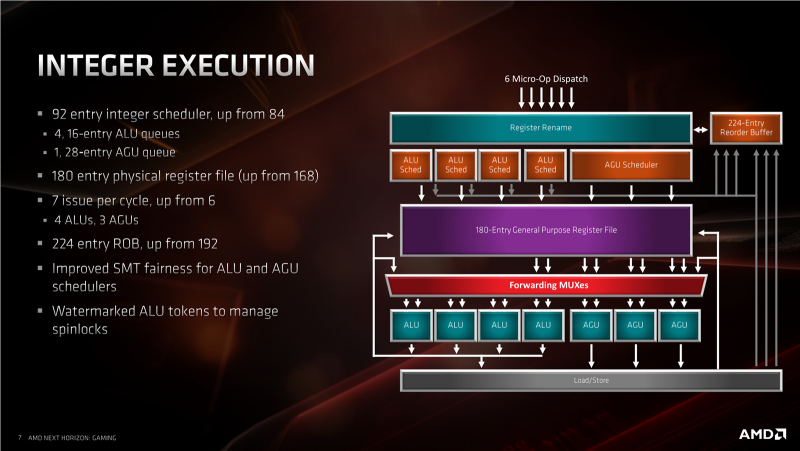

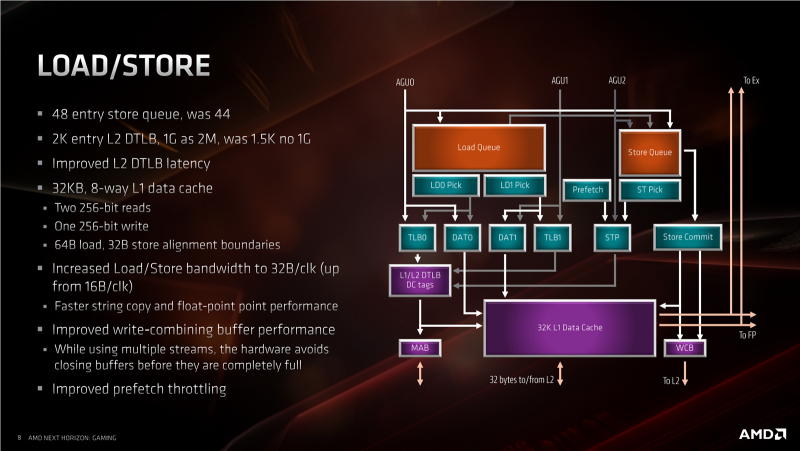

Зато заметные изменения в микроархитектуре произошли на стадии исполнения инструкций. Если говорить об исполнении целочисленных инструкций, то тут — впридачу к увеличению размера буферов (как самого планировщика, так регистрового файла и буфера переупорядочивания) примерно на 10–15% — появился дополнительный блок генерации адресов (AGU). В сумме это означает, что число исполнительных портов в Zen 2 выросло с шести до семи: четыре порта для арифметико-логических операций (ALU) и три порта — для операций генерации адресов (AGU). В результате микроархитектура Zen 2 может инициировать по две 256-битных операции чтения и по одной 256-битной операции записи каждый такт. Прошлая версия микроархитектуры была по понятным причинам ограничена только двумя подобными операциями за такт, причём лишь шириной 128 бит.

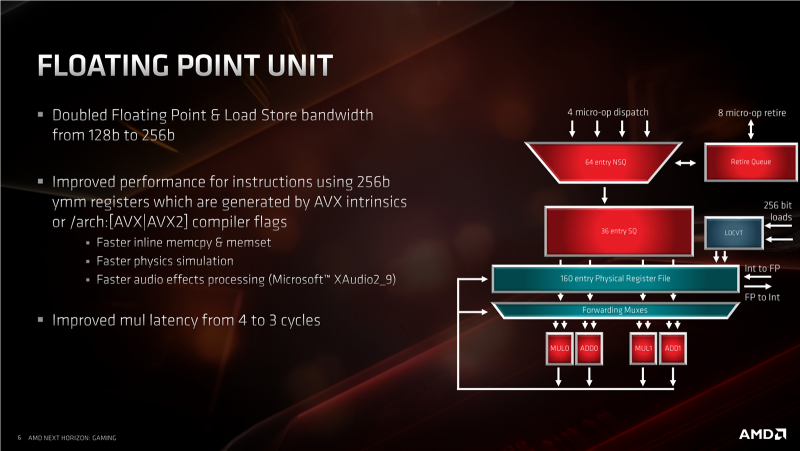

Но что ещё важнее, в Zen 2 компания AMD удвоила пропускную способность блока операций с плавающей точкой. Теперь он стал полностью 256-битным, что означает возможность прямого исполнения им AVX2-инструкций. В первоначальной архитектуре Zen/Zen+ такие команды, работающие с 256-битными регистрами, перед выполнением разбивались на пару 128-битных инструкций и обрабатывались в два приёма, следовательно, от Zen 2 можно ожидать двукратного увеличения темпа работы с AVX2-кодом. Состав же исполнительных устройств в FPU при этом остался старым. Предусмотрено два устройства для операций сложения и два — для операций умножения, что даёт Zen 2 возможность одновременно выполнять по две 256-битные FMA-команды. Здесь же очень пригождается способность новой микроархитектуры инициировать 256-битные операции пересылки данных: в результате исполнение AVX2-кода может происходить без каких-либо задержек. К тому же в Zen 2 AMD смогла добиться того, что обработка AVX2-инструкций может проводиться без какого-либо снижения тактовой частоты, как это происходит в процессорах Intel.

Попутно AMD сообщила и о том, что ей удалось увеличить скорость умножений чисел с плавающей точкой с четырёх до трёх тактов. В конечном итоге это также вносит свой вклад в увеличение удельной производительности процессоров с новой микроархитектурой.

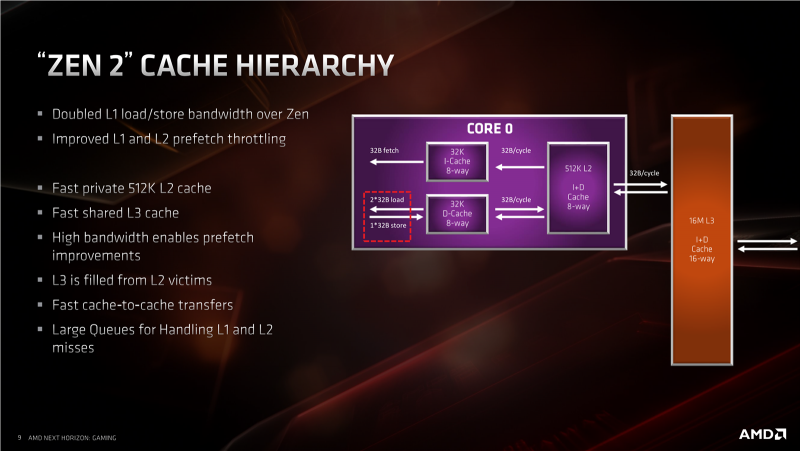

Как следует из сказанного, микроархитектура Zen 2 стала немного «шире» Zen в смысле способностей параллельного исполнения инструкций. Но в то же время она стала «шире» и в смысле работы с данными. Хотя подсистема кеш-памяти, работающей с данными, структурно не изменилась, она получила шины с большей пропускной способностью, которые позволяют получать необходимые данные, не задерживая выполнение AVX2-команд. Если конкретнее, то это означает, что L1-кеш данных сохранил размер 32 Кбайт на ядро с 8-канальной ассоциативностью, а L2-кеш, как и раньше, имеет объём 512 Кбайт на ядро с 8-канальной ассоциативностью, но теперь кеш-память может обслуживать по две 256-битных операции чтения и по одной 256-битной операции записи за такт на уровне L1, а также по одной 256-битной операции чтения и записи за такт на уровне L2. Латентность кеш-памяти не изменилась и составляет 4 такта для L1 и 12 тактов для L2.

Несмотря на неизменность структуры кеш-памяти, в Zen 2 была улучшена работа L2 TLB (буфера трансляции адресов). В первом поколении процессоров Zen размер этой таблицы составлял 1,5К, теперь же она увеличилась до 2К, причём её латентность при этом даже стала ниже. Но самое главное, теперь L2 TLB поддерживает страницы объёмом 1 Гбайт, чего в прошлых версиях микроархитектуры реализовано не было.

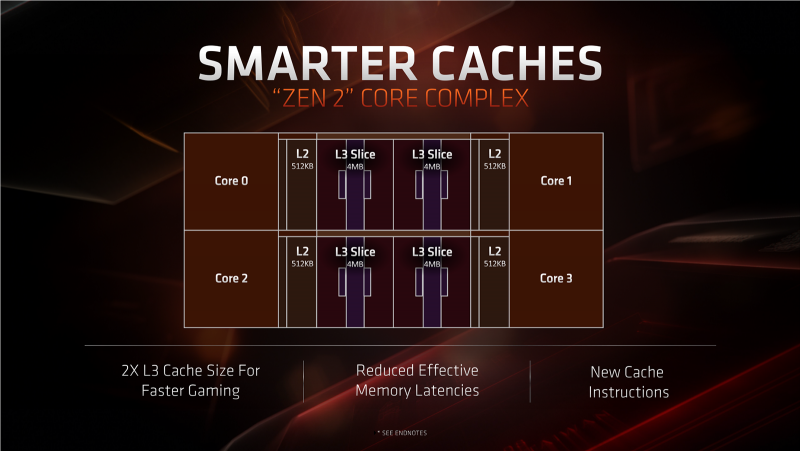

Ещё одним заметным изменением в Zen 2 стало удвоение объёма кеш-памяти третьего уровня. В новых процессорах её объём составляет не 8, как раньше, а 16 Мбайт на каждый четырёхъядерный CCX. Так AMD попыталась компенсировать расчленение процессора на несколько независимых кристаллов. Разработчики Zen 2 полагают, что рост объёма L3-кеша позволит снизить количество пересылок данных между чипсетами с ядрами и чиплетом с контроллером памяти. Может, это и так, но не стоит забывать о том, что увеличение объёма кеш-памяти практически всегда сопряжено с ростом латентности. И она у L3-кеша в Zen 2 действительно выросла до 40 тактов, в то время как в процессорах Zen L3-кеш имел латентность примерно на 5 тактов ниже.

⇡#От ядра — к CCX и CCD, и далее — к CPU

Выше уже говорилось о том, что конструкция процессоров Ryzen 3000 заметно отличается от того, как были устроены все прошлые Ryzen. Тем не менее CCX-комплексы собираются из ядер Zen 2 ровно так же, как и раньше. В один блок CCX объединяется 4 ядра и 16 Мбайт общей кеш-памяти третьего уровня.

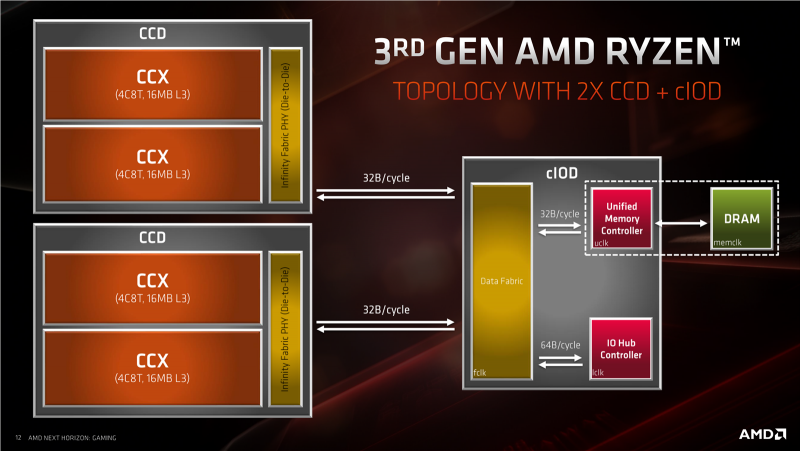

Пара CCX располагается на одном 7-нм полупроводниковом кристалле и формирует процессорный чиплет, получивший аббревиатуру CCD (Core Complex Die). Помимо ядер и кеша, в CCD-чиплет входит также контроллер шины Infinity Fabric, посредством которого должно обеспечиваться соединение CCD с обязательным для любого Ryzen 3000 чиплетом ввода-вывода.

В чиплете ввода-вывода (I/O) процессоров поколения Zen 2 располагаются так называемые внеядерные компоненты, а также элементы северного моста и SoC. В нём, помимо всего прочего, находятся контроллер памяти и контроллер шины PCI Express 4.0. Также в I/O-чиплете реализованы и две шины Infinity Fabric, необходимые для соединения с CCD-чиплетами.

В зависимости от того, о каком процессоре семейства Ryzen 3000 идёт речь, он может состоять либо из двух, либо из трёх чиплетов. В процессорах с числом ядер восемь и менее применяется один CCD-чиплет и один I/O-чиплет. В процессорах с числом ядер более восьми CCD-чиплетов становится уже два. Однако нужно понимать, что процессор при этом всё равно остаётся единым целым. За счёт того, что в любых Ryzen 3000 контроллер памяти находится в I/O-чиплете и он всего один, любое из ядер может гладко обращаться к любым её областям: никаких NUMA-конфигураций, которые портили жизнь владельцам процессоров Threadripper, в случае Zen 2 не будет.

Стоит напомнить, что Zen 2 — далеко не первая попытка перейти на многокристальную компоновку процессоров. Раньше производители уже прибегали к такому подходу. Например, опирались на два полупроводниковых кристалла четырёхъядерные Core 2 Quad, а ещё раньше такой же приём был использован при создании двухъядерных Pentium D. Но впоследствии производители всё же перешли на монолитную конструкцию процессоров, так как она оказалась более эффективной при росте числа ядер и переносе в процессор компонентов северного моста. Однако новые Ryzen 3000, в состав которых входит два или три чиплета, — отнюдь не шаг назад. Напротив, это переход на следующий уровень, поскольку AMD в новом поколении процессоров идёт не простым экстенсивным методом, наращивая количество вычислительных ядер за счёт добавления дополнительных кристаллов, а применяет куда более интеллектуальный подход, вводя в обиход чиплеты с различной функциональностью и объединяя их в единое целое специализированной высокоскоростной шиной Infinity Fabric.

Выигрыш, который даёт использование многокристальной компоновки, вполне очевиден. В первую очередь она позволяет снизить себестоимость. Производство чиплетов, имеющих сравнительно небольшую площадь кристалла, заметно проще, чем изготовление крупного монолитного процессора. Меньшие кристаллы не только позволяют получить более высокий выход годных чипов, но и эффективнее размещаются на круглой полупроводниковой подложке, что дополнительно снижает количество отходов. В конце концов, именно чиплетная компоновка позволила AMD создать весьма сложные процессоры Ryzen 3000 сравнительно недорогими, даже несмотря на то, что их выпуск организован на мощностях TSMC по самому передовому и новому для индустрии техпроцессу с нормами 7 нм.

Распределение функций процессора по различным чиплетам позволило AMD сэкономить и ещё в одном аспекте. Новый техпроцесс оказалось совсем необязательно применять при производстве всех частей процессоров. «Тонкие» передовые нормы важны для процессорных ядер, поскольку они прямо влияют на частотный потенциал и энергопотребление, но нет никакой нужды использовать их для изготовления более простого чиплета, отвечающего за функции ввода-вывода. Именно поэтому I/O-чиплет в Ryzen 3000 производится по-старинке — на фабриках GlobalFoundries по 12-нм техпроцессу, который использовался при изготовлении процессоров Ryzen второго поколения.

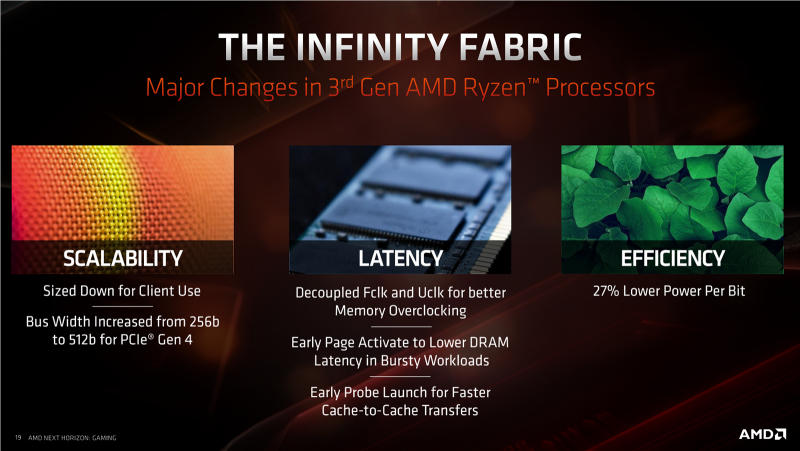

Впрочем, нужно иметь в виду, что чиплетная конструкция порождает и определённые трудности. Например, в современных процессорах очень высокие требования предъявляются к тому, как соединяются и взаимодействуют друг с другом различные части CPU. Реализовать такую шину при многочиповой компоновке оказывается несколько сложнее. Впрочем, эта задача была успешно решена инженерами AMD. Процессоры Ryzen первого и второго поколений, хотя они и были основаны на монолитном ядре, использовали для соединения CCX и контроллера памяти, северного моста и элементов SoC специализированную шину Infinity Fabric. В новых процессорах Ryzen 3000 применяется вторая версия этой шины: именно она отвечает за передачу данных между всеми чиплетами.

Откровенно говоря, к тому, как работает Infinity Fabric, ранее высказывались вполне обоснованные претензии: она не всегда могла обеспечить должный уровень быстродействия при взаимодействии процессорных ядер с L3-кешем и с контроллером памяти. В процессорах Ryzen 3000 компания AMD постаралась исправить основные недостатки Infinity Fabric.

Во-первых, эта шина была расширена вдвое: теперь её ширина составляет 512 бит, что означает двукратное увеличение пропускной способности и возможность пересылки по 32 байта за такт в каждом направлении. Разработчики уверяют, что на этот шаг они пошли в первую очередь из-за появления в Ryzen 3000 поддержки PCI Express 4.0, но очевидно, что более производительная шина, которая связывает все ключевые компоненты процессора, сыграет положительную роль и во многих других случаях.

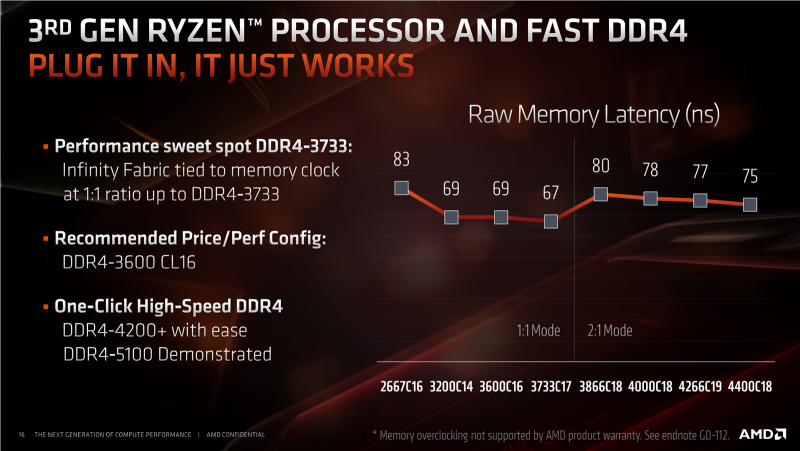

Во-вторых, Infinity Fabric теперь «развязана» с контроллером памяти по частоте. Раньше частота работы этой шины была синхронизирована с частотой памяти, что, с одной стороны, приводило к сильной зависимости производительности процессоров Ryzen от скорости установленных в системе модулей DDR4 SDRAM, а с другой — препятствовало разгону памяти выше 3466–3600 МГц. Теперь же шина Infinity Fabric сможет работать с контроллером памяти не только синхронно, но и на вдвое меньшей относительно него частоте — с применением делителя 2:1. Это — по крайней мере теоретически — означает гораздо большую свободу в выборе скорости памяти, хотя AMD продолжает настаивать на том, что синхронный режим для Infinity Fabric всё равно будет обеспечивать лучшую производительность, и оптимальнее с Ryzen 3000 использовать модули памяти DDR4–3600 с низкими таймингами.

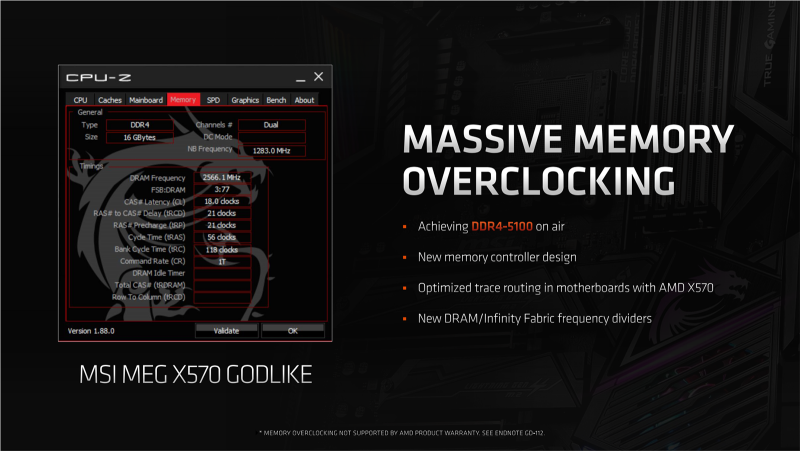

Тем не менее уже сейчас известно о том, что память в Socket AM4-системах, оснащённых процессорами Ryzen 3000, действительно можно будет сильно разгонять.

Например, AMD показала работу модулей памяти в режиме DDR4–5100 в системе, построенной на Socket AM4-материнской плате MSI MEG X570 Godlike.

Следующая страница →

Полный текст статьи читайте на 3DNews