Эксперимент: 12-ядерный процессор в десктопе

В недалёком прошлом основной характеристикой центральных процессоров для настольных компьютеров, адекватно отражающей их уровень производительности, была тактовая частота. Некоторые наши читатели наверняка даже помнят те времена, когда именно эта величина, а не абстрактный процессорный номер занимала центральное место в маркировке CPU. Однако с тех пор всё сильно изменилось. Оказалось, что увеличение частоты процессоров выше 3–4 ГГц вызывает серьёзные проблемы с тепловыделением, и потому прогресс в частоте прекратился, вместо этого производители начали увеличивать количество ядер. Высокая производительность в таких чипах обеспечивается не столько способностью выполнять инструкции с высоким темпом, сколько наличием в процессоре нескольких равноправных вычислительных ядер, предлагающих возможности параллельной обработки.

Однако и развитие концепции многоядерности требует серьёзных технологических усилий — увеличение количества ядер приводит к кратному росту транзисторного бюджета и потому оказывается возможным лишь во время серьёзных прорывов в миниатюризации норм производственного процесса. Так что сегодня мы пришли к ситуации, когда разница в скорости работы флагманских процессоров разных поколений стала определяться по большей части лишь изменениями в их микроархитектуре. Действительно, никакого ощутимого прогресса в частоте мы не видим примерно с 2003 года, а количество ядер у старших моделей десктопных процессоров не растёт где-то с 2009-го. Если же к этому прибавить тот факт, что новые микроархитектуры в последнее время делают лишь робкие шаги в сторону улучшения удельной производительности, то вырисовывается достаточно унылая картина: состояние рынка процессоров для настольных систем можно охарактеризовать как явно застойное.

К счастью, понимают это не только потребители, но и сами разработчики. Поэтому, например, последний высокопроизводительный CPU компании Intel, Core i7–5960X, получил не стандартные по меркам продуктов такого класса шесть вычислительных ядер, а уже целых восемь. В ряде случаев это действительно позволило поднять быстродействие десктопных систем верхней ценовой категории на принципиально новый уровень. Однако расширение набора вычислительных ресурсов на одну треть некоторым энтузиастам может показаться недостаточной мерой, тем более что на самом деле Intel умеет делать чипы и со значительно большим числом ядер. В десктопы они не попадают, но для серверного рынка у компании есть предложения с 10, 12, 14, 15, а с первого квартала этого года — с 16 и даже с 18 ядрами. Поэтому совершенно неудивительно, что существует небольшая прослойка пользователей, которая не обращает внимания на формальное позиционирование и строит свои настольные компьютеры на базе таких монструозных многоядерных процессоров. Более того, конфигурации с подобными чипами существуют среди серийно выпускаемых компьютеров: например, 12-ядерным CPU класса Xeon может быть укомплектован один из вариантов рабочей станции Mac Pro.

Но какой бы соблазнительной ни выглядела затея создания настольной системы с многоядерным процессором, следует понимать, что уровень её реального быстродействия может оказаться существенно ниже ожидаемого. Дело в том, что выигрыш от возможности глубокого распараллеливания вычислений по ядрам могут получать далеко не все алгоритмы, и существует целый пласт реальных задач, для которых разница между CPU с восемью и, например, с двенадцатью вычислительными ядрами окажется несущественной. Не стоит забывать и о том, что сосредоточение в процессорном кристалле большего числа ядер увеличивает тепловыделение, заставляя дополнительно ограничивать частоты многоядерных CPU. В результате использование таких чипов в ряде ситуаций может оказаться не только не полезным, но и даже вредным.

Учитывая сказанное, мы решили провести эксперимент и посмотреть, доросли ли общеупотребительные десктопные нагрузки до возможностей, которые им могут предоставить современные процессоры с числом ядер больше восьми. По случаю в нашей редакции оказался 12-ядерный процессор Xeon E5 v3 нового поколения, основанный на дизайне Haswell-EP. Мы решили попробовать собрать с его участием настольную систему, похожую на флагманские платформы со старшими Haswell-E, и посмотреть на практике, будет ли от этого какой-нибудь прок.

⇡#Процессорные ядра и масштабируемость производительности

⇡#Процессорные ядра и масштабируемость производительности

Прежде чем заняться тестами, необходимо несколько слов сказать и о том, что эффект от увеличения числа ядер в процессоре можно оценить и без проведения практических испытаний. Совершенно очевидно, что чипы с высоким числом вычислительных ядер эффективны лишь в тех случаях, когда решаемые на компьютере задачи могут быть распараллелены. Поэтому, прежде чем воплощать в жизнь формулу «мне нужно больше ядер», нужно убедиться, что все ресурсы такого процессора действительно могут быть загружены полезной работой — только в этом случае можно будет говорить о положительном масштабировании производительности. Например, если используемые вами приложения не могут создавать более четырёх параллельных потоков, то процессор с числом ядер более четырёх будет полезен лишь в том случае, если вы будете запускать две или большее число копий таких программ одновременно.

Впрочем, даже в случае приложений с неограниченной многопоточностью прирост производительности может оказаться не впечатляющим. Дело в том, что любые, даже самые хорошо распараллеливаемые алгоритмы содержат части, которые нуждаются в последовательном выполнении. Этот фактор встаёт на пути кратной масштабируемости быстродействия и описывается в так называемом законе Амдала. Сформулированный американским математиком Джином Амдалом ещё в 1969 году принцип гласит: «В случае, когда задача разделяется на несколько частей, суммарное время её выполнения на параллельной системе не может быть меньше времени выполнения самого длинного фрагмента». И это значит, что ускорение выполнения программы за счёт распараллеливания на множестве процессорных ядер ограничено временем, необходимым для выполнения её последовательных связанных частей.

Идею закона Амдала проще всего пояснить практическим примером: если в программе идеальному распараллеливанию поддаётся 90 процентов кода, а оставшиеся 10 процентов могут выполняться лишь в однопоточном режиме, то максимально достижимо только десятикратное увеличение скорости работы программы — вне зависимости от того, насколько большим количеством ядер располагает процессор. Именно поэтому многоядерные архитектуры эффективнее всего использовать в тех ситуациях, когда доля последовательного кода минимальна. При этом увеличение тактовой частоты остаётся более действенным и универсальным способом улучшения быстродействия.

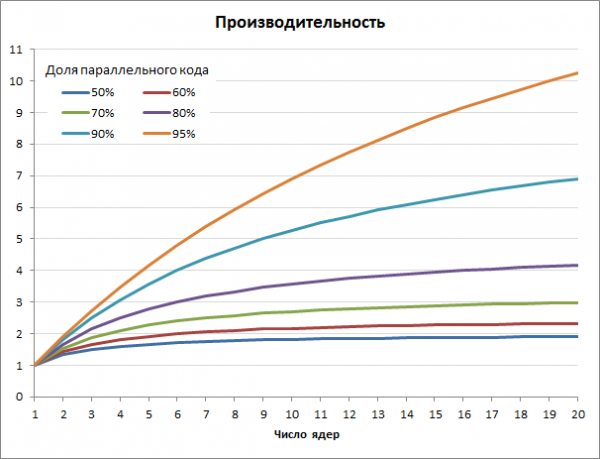

На следующей иллюстрации мы приводим графики теоретически рассчитанного по закону Амдала ускорения выполнения программ с долями параллельного кода от 50 до 95 процентов для равночастотных процессоров с числом ядер от 1 до 20.

Глядя на график, нетрудно уловить важную закономерность. С ростом количества вычислительных ядер в процессоре получаемый за счёт этого прирост производительности постепенно снижается. То есть если, например, шестиядерный процессор позволяет получить четырёхкратное улучшение быстродействия по сравнению с одноядерным, то это совершенно не означает, что применение для решения той же задачи 12-ядерного CPU позволит довести прирост в быстродействии до восьмикратного уровня. Более того, увеличение числа ядер выше восьми имеет смысл лишь в таких задачах, где доля распараллеливаемого кода больше 80 процентов. В противном случае кратное усложнение (и, соответственно, удорожание) CPU обернётся лишь незначительным выигрышем в производительности, который не будет превышать и 20 процентов.

Глядя на график, нетрудно уловить важную закономерность. С ростом количества вычислительных ядер в процессоре получаемый за счёт этого прирост производительности постепенно снижается. То есть если, например, шестиядерный процессор позволяет получить четырёхкратное улучшение быстродействия по сравнению с одноядерным, то это совершенно не означает, что применение для решения той же задачи 12-ядерного CPU позволит довести прирост в быстродействии до восьмикратного уровня. Более того, увеличение числа ядер выше восьми имеет смысл лишь в таких задачах, где доля распараллеливаемого кода больше 80 процентов. В противном случае кратное усложнение (и, соответственно, удорожание) CPU обернётся лишь незначительным выигрышем в производительности, который не будет превышать и 20 процентов.

Именно основываясь на подобных расчётах, Intel и приняла решение ограничить количество ядер в десктопных процессорах восемью штуками. Большинство общеупотребительных задач, решаемых настольными компьютерами, имеют долю распараллеливаемого кода, не превышающую 80-процентного уровня, поэтому использование в них CPU с серверным арсеналом ядер попросту нецелесообразно. А для основной массы игровых приложений, пусть даже и оптимизированных под многопоточность, где доля параллельного кода редко выходит за 60-процентную границу, вполне хватит и процессоров с четырьмя ядрами. Дальнейшее же углубление многоядерности может добавить к производительности лишь 15–20 процентов, что вряд ли можно назвать достойным откликом на рост количества вычислительных ядер в несколько раз.

Все приведённые выше теоретические расчёты сделаны для идеального случая и не учитывают, что ядра разделяют между собой общие ресурсы, такие как кеш и оперативная память, а также имеют ограниченный канал для взаимодействия. Поэтому в реальной жизни производительность может масштабироваться ещё хуже, чем показано на графиках. Более того, при увеличении числа ядер выше некой границы их быстродействие может даже снижаться. Здесь же нужно упомянуть и о том, что увеличение сложности процессора в большинстве случаев влечёт за собой некоторое снижение его предельной тактовой частоты. Поэтому с многоядерными CPU явно не стоит связывать большие надежды. Формула «больше ядер — выше быстродействие» работает далеко не всегда, причём десктопные нагрузки представляют собой как раз не очень благоприятную среду для подобной масштабируемости. Иными словами, увеличение числа ядер — достаточно специфический способ для улучшения быстродействия процессора, и подходит он далеко не для всех ситуаций.

⇡#Xeon E5 v3 и Core i7–5хх0: в чём разница

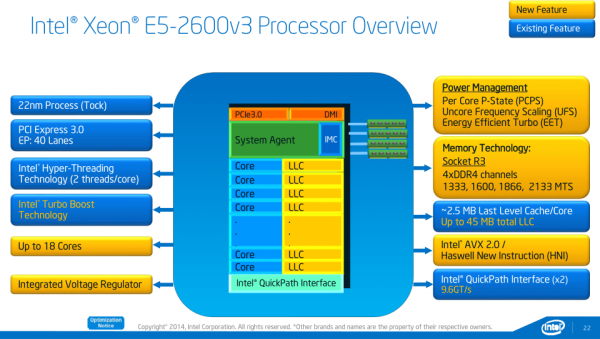

Первые процессоры серии Haswell-EP, появившиеся в результате перевода серверных многоядерных CPU на микроархитектуру Haswell, появились одновременно с Haswell-E осенью прошлого года. Эти чипы, получившие официальное наименование Xeon E5 v3, основываются на полупроводниковых кристаллах, производимых по 22-нм технологии, и предназначаются для установки в платы с одним или несколькими разъёмами LGA2011–3, не совместимыми по выводам с привычным LGA2011, использовавшимся в серверных платформах прошлых поколений. Основными преимуществами Haswell-EP по сравнению с их предшественниками Sandy Bridge-EP и Ivy Bridge-EP стало увеличение максимального количества ядер вместе с ростом объёма кеш-памяти, а также снижение тепловыделения. Кроме того, процессоры Xeon E5 v3 получили встроенный преобразователь питания и поддержку AVX2-инструкций, а также унаследовали ряд других улучшений, повышающих удельную производительность за счёт оптимизаций на уровне микроархитектуры.

Когда мы знакомились с высокопроизводительной десктопной платформой LGA2011–3 и с процессорами семейства Haswell-E, мы говорили о том, что она получена в результате адаптации серверных процессоров Haswell-EP для настольных систем. Именно это и обуславливает наличие между ними родственных связей, которые позволяют устанавливать процессоры класса Xeon E5 v3 в материнские платы на базе набора логики Intel X99. В существовании такой совместимости нет ничего странного: подобные полусерверные-полудесктопные конфигурации можно было создавать и на базе процессоров и платформ прошлого поколения — ничего не изменилось и с внедрением новой микроархитектуры. Haswell-E и Haswell-EP используют одинаковый процессорный разъём, а для работоспособности Xeon E5 v3 в материнках для настольных ПК необходима лишь их поддержка со стороны BIOS, которую производители плат обычно добавляют как минимум в своих продуктах верхней ценовой категории.

Когда мы знакомились с высокопроизводительной десктопной платформой LGA2011–3 и с процессорами семейства Haswell-E, мы говорили о том, что она получена в результате адаптации серверных процессоров Haswell-EP для настольных систем. Именно это и обуславливает наличие между ними родственных связей, которые позволяют устанавливать процессоры класса Xeon E5 v3 в материнские платы на базе набора логики Intel X99. В существовании такой совместимости нет ничего странного: подобные полусерверные-полудесктопные конфигурации можно было создавать и на базе процессоров и платформ прошлого поколения — ничего не изменилось и с внедрением новой микроархитектуры. Haswell-E и Haswell-EP используют одинаковый процессорный разъём, а для работоспособности Xeon E5 v3 в материнках для настольных ПК необходима лишь их поддержка со стороны BIOS, которую производители плат обычно добавляют как минимум в своих продуктах верхней ценовой категории.

Однако между Xeon E5 v3 и Core i7–5xx0 для LGA2011–3 знак тождественного равенства поставить всё же нельзя. Эти процессоры имеют важные различия: на фоне Haswell-EP десктопный дизайн имеет заметные упрощения, а старшие модификации Xeon E5 v3, обладающие числом ядер более восьми, могут похвастать более продвинутой внутренней конструкцией. В частности, для серверных процессоров Haswell-EP у Intel подготовлено три принципиально различных процессорных кристалла, но в Haswell-E используется лишь самый простой из них.

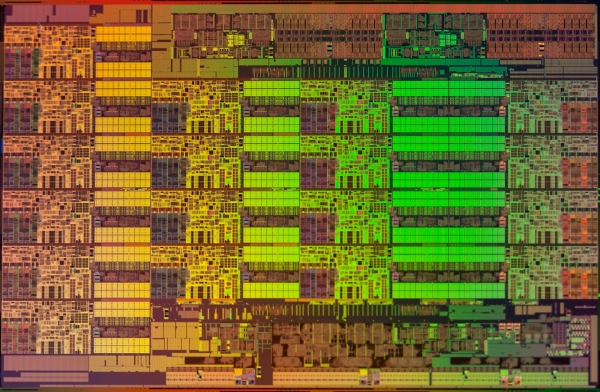

Ядро 18-ядерного процессора семейства Xeon E5 v3

Ядро 18-ядерного процессора семейства Xeon E5 v3

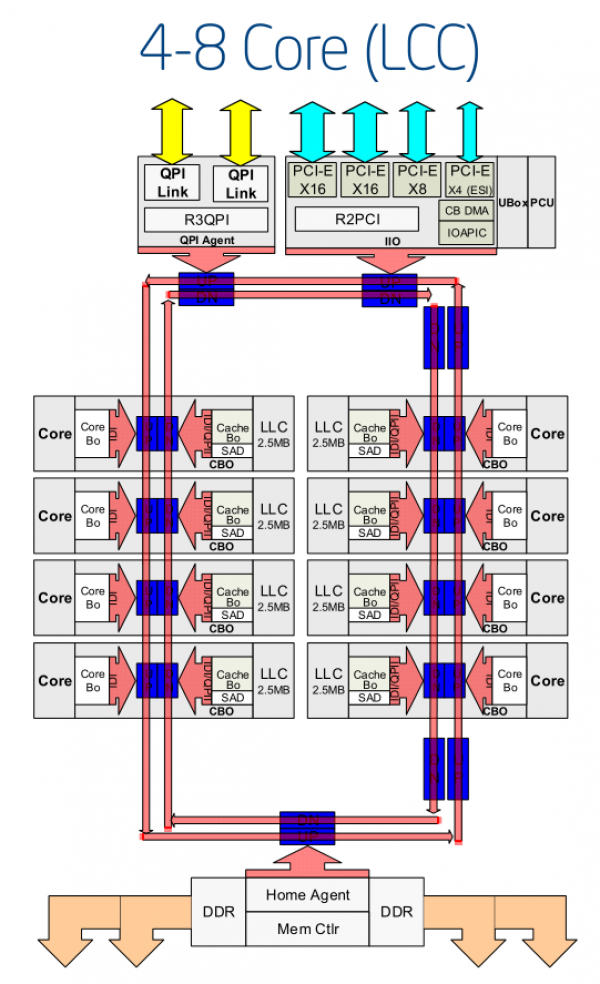

Младшие Xeon E5 v3 с числом ядер до восьми включительно, так же как и десктопные Haswell-E, основываются на кристалле площадью 354 мм2, состоящем из 2,6 млрд транзисторов. Структурно этот кристалл состоит из двух рядов процессорных ядер, между которыми расположен разделяемый кеш третьего уровня. Ядра и блоки кеша объединяются между собой одной двунаправленной кольцевой шиной, к которой подключён четырёхканальный контроллер памяти с поддержкой DDR4 SDRAM, контроллер шины PCI Express 3.0 и QPI-интерфейс, необходимый при создании многопроцессорных конфигураций.

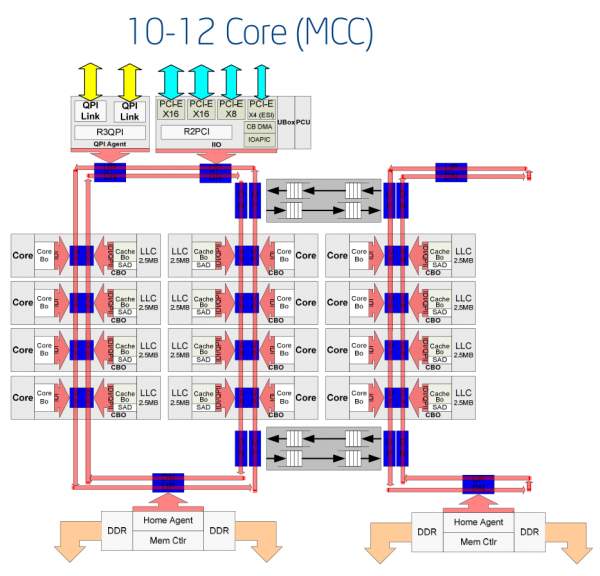

Процессоры Xeon E5 v3, обладающие числом ядер от 10 до 12, используют более массивный полупроводниковый кристалл, включающий 3,84 млрд транзисторов и оккупирующий площадь 492 мм2. В нём вычислительные ядра расположены тремя рядами, а кеш распределён в двух областях — между первыми двумя рядами ядер и с наружного края третьего ряда. Для коммутации и обмена данными в этом случае используется уже две равноправные кольцевые шины. Одна связывает первые ряды ядер и кеша, а вторая работает с третьим рядом и крайней областью кеш-памяти. Для обмена данными между кольцевыми шинами в процессоре появился дополнительный элемент — буферизирующий коммутатор. Такая схема, получившая название «кластер-на-ядре», снижает нагрузку на кольцевые шины и обеспечивает более высокую скорость взаимодействия между ядрами и лучшую пропускную способность кеш-памяти при многопоточных нагрузках. Более того, в таком варианте процессорного дизайна контроллер памяти разделён на две части, которые разведены по различным кольцевым шинам. Фактически процессоры Xeon E5 v3 с числом вычислительных ядер более 10 обладают не одним четырёхканальным, а двумя двухканальными контроллерами памяти с поддержкой DDR4 SDRAM.

Процессоры Xeon E5 v3, обладающие числом ядер от 10 до 12, используют более массивный полупроводниковый кристалл, включающий 3,84 млрд транзисторов и оккупирующий площадь 492 мм2. В нём вычислительные ядра расположены тремя рядами, а кеш распределён в двух областях — между первыми двумя рядами ядер и с наружного края третьего ряда. Для коммутации и обмена данными в этом случае используется уже две равноправные кольцевые шины. Одна связывает первые ряды ядер и кеша, а вторая работает с третьим рядом и крайней областью кеш-памяти. Для обмена данными между кольцевыми шинами в процессоре появился дополнительный элемент — буферизирующий коммутатор. Такая схема, получившая название «кластер-на-ядре», снижает нагрузку на кольцевые шины и обеспечивает более высокую скорость взаимодействия между ядрами и лучшую пропускную способность кеш-памяти при многопоточных нагрузках. Более того, в таком варианте процессорного дизайна контроллер памяти разделён на две части, которые разведены по различным кольцевым шинам. Фактически процессоры Xeon E5 v3 с числом вычислительных ядер более 10 обладают не одним четырёхканальным, а двумя двухканальными контроллерами памяти с поддержкой DDR4 SDRAM.

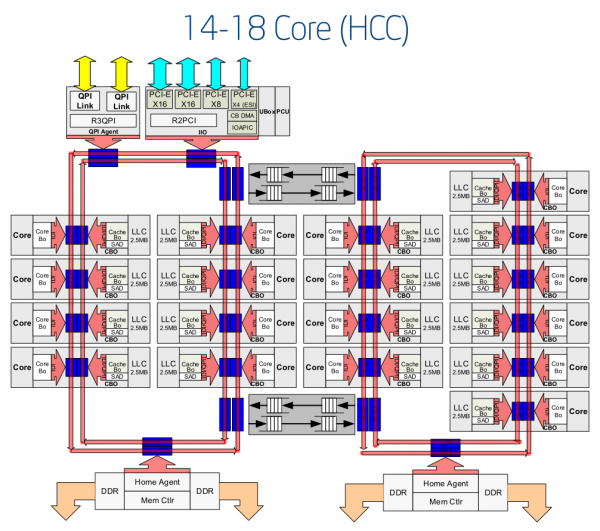

Самый же сложный вариант полупроводникового кристалла Haswell-EP, который предназначается для процессоров с 14–18 вычислительными ядрами, имеет ещё более замысловатое строение. Площадь такого кристалла составляет 662 мм2, он содержит 5,69 млрд транзисторов. В нём ядра расположены четырьмя рядами, между которыми проложены две области кеш-памяти третьего уровня. Как и в предыдущем случае, эти элементы объединены двумя кольцевыми шинами, сопряжёнными в единое целое буферизирующим коммутатором. Контроллер памяти DDR4 вновь разделён на две двухканальные части, а контроллеры PCIe и QPI отнесены к той из кольцевых шин, которая обслуживает меньшее количество ядер.

Самый же сложный вариант полупроводникового кристалла Haswell-EP, который предназначается для процессоров с 14–18 вычислительными ядрами, имеет ещё более замысловатое строение. Площадь такого кристалла составляет 662 мм2, он содержит 5,69 млрд транзисторов. В нём ядра расположены четырьмя рядами, между которыми проложены две области кеш-памяти третьего уровня. Как и в предыдущем случае, эти элементы объединены двумя кольцевыми шинами, сопряжёнными в единое целое буферизирующим коммутатором. Контроллер памяти DDR4 вновь разделён на две двухканальные части, а контроллеры PCIe и QPI отнесены к той из кольцевых шин, которая обслуживает меньшее количество ядер.

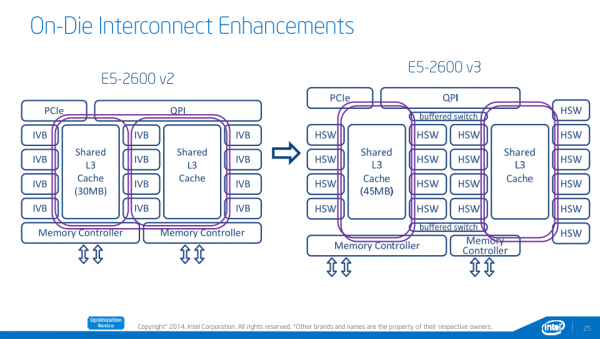

Вариант с двумя независимыми двунаправленными кольцевыми шинами и буферизирующим коммутатором в Haswell-EP нашёл применение впервые. Ранее в многоядерных процессорах Sandy Bridge-EP и Ivy Bridge-EP ядра объединялись тремя однонаправленными кольцевыми шинами, проходящими через разные группы ядер. Такая схема была проще и обходилась без какой-либо коммутации, но она показала свою неэффективность в сложных многопоточных задачах, в которых трафик по кольцевым шинам сильно возрастал и мог привести к нежелательным простоям ядер.

Вариант с двумя независимыми двунаправленными кольцевыми шинами и буферизирующим коммутатором в Haswell-EP нашёл применение впервые. Ранее в многоядерных процессорах Sandy Bridge-EP и Ivy Bridge-EP ядра объединялись тремя однонаправленными кольцевыми шинами, проходящими через разные группы ядер. Такая схема была проще и обходилась без какой-либо коммутации, но она показала свою неэффективность в сложных многопоточных задачах, в которых трафик по кольцевым шинам сильно возрастал и мог привести к нежелательным простоям ядер.

Одной из ключевых возможностей, появившихся в LGA2011–3-процессорах, стала поддержка нового типа памяти DDR4 SDRAM с большими рабочими частотами и меньшим напряжением питания. Совместимость с такой памятью есть как в серверных, так и в десктопных модификациях CPU, однако контроллеры DDR4, которыми располагают серверные Xeon E5 v3, имеют несколько иные возможности, чем есть в процессорах класса Core i7–5хх0. Для серверных CPU критичным является объём поддерживаемой памяти, поэтому в них введена поддержка регистровых модулей (RDIMM) и модулей с пониженной нагрузкой (LRDIMM). В результате если десктопный Haswell-E позволяет установить до 64 Гбайт памяти восемью небуферизованными планками, серверные процессоры Haswell-EP могут комплектоваться массивом из двенадцати модулей LRDIMM общей ёмкостью до 768 Гбайт или аналогичным количеством RDIMM-модулей общим объёмом 384 Гбайт. При этом скорость таких модулей, так же как и в случае десктопных платформ, может достигать режима DDR4–2133. Таким образом, если принять во внимание четырёхканальную архитектуру контроллера DDR4 SDRAM в Haswell-EP, максимальная производительность подсистемы памяти составляет 68 Гбайт/с на процессор.

Одной из ключевых возможностей, появившихся в LGA2011–3-процессорах, стала поддержка нового типа памяти DDR4 SDRAM с большими рабочими частотами и меньшим напряжением питания. Совместимость с такой памятью есть как в серверных, так и в десктопных модификациях CPU, однако контроллеры DDR4, которыми располагают серверные Xeon E5 v3, имеют несколько иные возможности, чем есть в процессорах класса Core i7–5хх0. Для серверных CPU критичным является объём поддерживаемой памяти, поэтому в них введена поддержка регистровых модулей (RDIMM) и модулей с пониженной нагрузкой (LRDIMM). В результате если десктопный Haswell-E позволяет установить до 64 Гбайт памяти восемью небуферизованными планками, серверные процессоры Haswell-EP могут комплектоваться массивом из двенадцати модулей LRDIMM общей ёмкостью до 768 Гбайт или аналогичным количеством RDIMM-модулей общим объёмом 384 Гбайт. При этом скорость таких модулей, так же как и в случае десктопных платформ, может достигать режима DDR4–2133. Таким образом, если принять во внимание четырёхканальную архитектуру контроллера DDR4 SDRAM в Haswell-EP, максимальная производительность подсистемы памяти составляет 68 Гбайт/с на процессор.

Ещё одно различие между Haswell-E и Haswell-EP заключается в поддержке шины QPI. В серверных платформах эта шина используется для создания межпроцессорных соединений, поэтому в десктопных моделях CPU она отсутствует. Серверные же Xeon E5 v3 имеют активный контроллер QPI 1.1, который, кстати говоря, реализует две шины с пропускной способностью 9,6 ГТрансфер/с, что на 20 процентов выше полосы пропускания межпроцессорной шины в Sandy Bridge-EP и Ivy Bridge-EP.

⇡#Тестовый процессор: Xeon E5–4650 v3

На самом деле, если уж говорить об использовании мощных серверных процессоров в составе настольных конфигураций, то для этой цели лучше бы подошли процессоры серии Xeon E5–2600 v3, имеющие до 18 ядер и формально ориентированные на двухпроцессорные конфигурации. Однако нам выбирать не приходится — компания Intel предоставила нам для экспериментов Xeon E5–4650 v3, ориентированный на четырёхпроцессорные системы. Впрочем, для десктопной платформы с единственным процессорным разъёмом почти никакой разницы нет. Да, Xeon E5–4650 v3, в отличие от Xeon E5–26xx v3, обойдётся несколько дороже, однако в этой статье о стоимости мы говорить не будем.

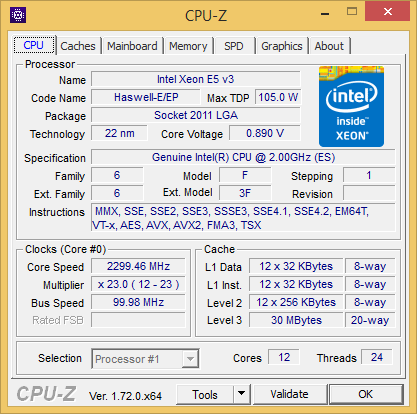

Xeon E5–4650 v3 — это серверный Haswell-EP средней мощности. Он несёт в себе 12 вычислительных ядер с поддержкой технологии Hyper-Threading, обладает L3-кешем объёмом 30 Мбайт и имеет паспортную тактовую частоту 2,0 ГГц. Обратите внимание, частота этого CPU заметно ниже, чем у десктопного восьмиядерника Core i7–5960X, и это — расплата за возросшее количество ядер. К тому же роль играет и тот факт, что тепловой пакет Xeon E5–4650 v3, ориентированного на использование в составе упакованных в стоечные корпуса многопроцессорных конфигураций, ограничен достаточно консервативной величиной 105 Вт. Впрочем, невысокая паспортная частота отчасти компенсируется режимом Turbo, благодаря которому процессор может разгоняться до 2,6 ГГц при небольших нагрузках и до 2,3 ГГц при нагрузке на все 12 ядер.

Как это ни странно, но такой типично серверный процессор без каких-либо проблем может работать в десктопной материнской плате. Несмотря на то, что для систем на базе Haswell-EP у Intel имеются специализированные наборы логики, например Intel C612, серверные LGA2011–3-процессоры прекрасно себя чувствуют в типично десктопных платах на базе чипсета Intel X99. Мы проверили наш тестовый Xeon E5–4650 v3 в ASUS X99-Deluxe и в ASUS Rampage V Extreme — в обоих случаях никаких препятствий не возникло, да и в списке совместимости на сайте ASUS поддержка Xeon E5 v3 материнскими платами на базе Intel X99 обещана явно. Более того, как показала практика, Haswell-EP легко находит общий язык и с обычной небуферизованной DDR4 SDRAM, так что десктопная платформа с процессором серии Xeon E5 v3 на самом деле не требует никаких специальных комплектующих серверного класса. Иными словами, если вы решитесь собирать настольную систему с многоядерным серверным CPU, дополнительных трат не потребуется — раскошелиться придётся только на сам процессор. Например, цены 12-ядерных Haswell-EP начинаются с отметки в $1 500.

Как это ни странно, но такой типично серверный процессор без каких-либо проблем может работать в десктопной материнской плате. Несмотря на то, что для систем на базе Haswell-EP у Intel имеются специализированные наборы логики, например Intel C612, серверные LGA2011–3-процессоры прекрасно себя чувствуют в типично десктопных платах на базе чипсета Intel X99. Мы проверили наш тестовый Xeon E5–4650 v3 в ASUS X99-Deluxe и в ASUS Rampage V Extreme — в обоих случаях никаких препятствий не возникло, да и в списке совместимости на сайте ASUS поддержка Xeon E5 v3 материнскими платами на базе Intel X99 обещана явно. Более того, как показала практика, Haswell-EP легко находит общий язык и с обычной небуферизованной DDR4 SDRAM, так что десктопная платформа с процессором серии Xeon E5 v3 на самом деле не требует никаких специальных комплектующих серверного класса. Иными словами, если вы решитесь собирать настольную систему с многоядерным серверным CPU, дополнительных трат не потребуется — раскошелиться придётся только на сам процессор. Например, цены 12-ядерных Haswell-EP начинаются с отметки в $1 500.

Выше мы подробно расписали преимущества Xeon E5 v3 перед Core i7–5хх0, главными из которых являются увеличенное число вычислительных ядер и более продуманная схема внутренних коммуникаций. Однако у серверных процессоров есть и явные минусы, которые наверняка огорчат энтузиастов. Дело в том, что десктопные Haswell-E благосклонны к разгону и имеют незаблокированные множители, позволяя произвольно варьировать частоту вычислительных ядер, кеша и памяти. Серверные же процессоры такие вольности пресекают на корню. Поднять частоту выше величин, предусмотренных технологией Turbo Boost, невозможно. Не допускается также и тактование памяти в режимах, превосходящих DDR3–2133. И это значит, что на любом разгоне Xeon E5 v3 можно поставить крест.

Выше мы подробно расписали преимущества Xeon E5 v3 перед Core i7–5хх0, главными из которых являются увеличенное число вычислительных ядер и более продуманная схема внутренних коммуникаций. Однако у серверных процессоров есть и явные минусы, которые наверняка огорчат энтузиастов. Дело в том, что десктопные Haswell-E благосклонны к разгону и имеют незаблокированные множители, позволяя произвольно варьировать частоту вычислительных ядер, кеша и памяти. Серверные же процессоры такие вольности пресекают на корню. Поднять частоту выше величин, предусмотренных технологией Turbo Boost, невозможно. Не допускается также и тактование памяти в режимах, превосходящих DDR3–2133. И это значит, что на любом разгоне Xeon E5 v3 можно поставить крест.

Таким образом, несмотря на то, что изначально идея использования процессора Xeon E5 v3 в десктопной платформе выглядела очень многообещающе, по мере более глубокого погружения в тему мы сталкиваемся с всё возрастающим числом аргументов против. И хотя никаких явных препятствий для создания серверно-десктопного гибрида пока не просматривается, похоже, что это попросту нецелесообразно. Впрочем, не будем забегать вперёд — перед тем как делать какие-то выводы, давайте ознакомимся с результатами тестов.

Следующая страница →

Виджет от SocialMart

Если вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

Полный текст статьи читайте на 3DNews