SK hynix придумала, как сделать жизнеспособную 5-битную PLC NAND

На конференции IEDM 2025 компания SK hynix представила новую архитектуру 5-битной памяти NAND-флеш. Такая ячейка принимает 32 состояния и требует сложнейших контроллеров для хранения данных, что всё ещё делает эту технологию нежизнеспособной. Представленная SK hynix архитектура PLC обходит это ограничение, предлагая физически разделить каждую ячейку на две идентичные и работающие в паре половинки, где каждая из них будет удерживать всего по 6 уровней.

Источник изображений: SK hynix

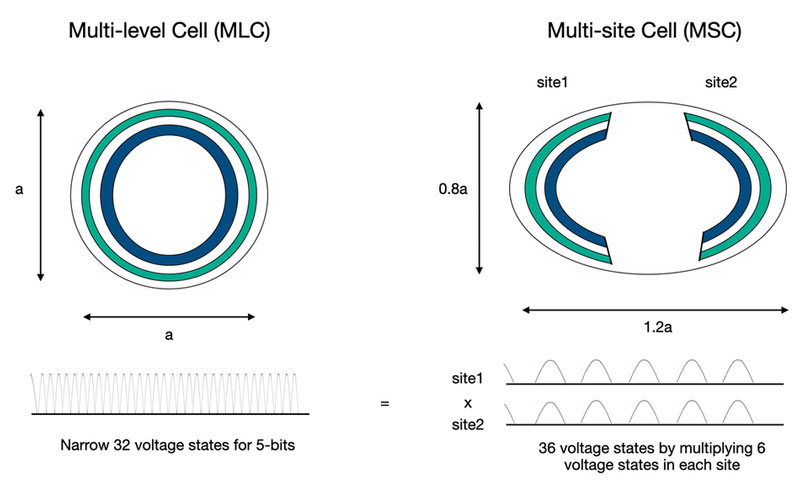

Производители NAND-флеш давно освоили выпуск памяти с запись четырёх бит в каждую ячейку (QLC). Такая память хранит информацию в 16 состояниях уровня заряда. Следующая ступенька — память PLC (penta-level cell) — предполагает работу с 32 состояниями. Наградой за решение проблемы со сложностью обработки каждой такой ячейки станет условно бесплатное увеличение ёмкости NAND-флеш на 25% в том же объёме кремния на пластине. Увы, этот барьер пока никому не дался. По крайней мере — в лоб, но можно зайти с другой стороны.

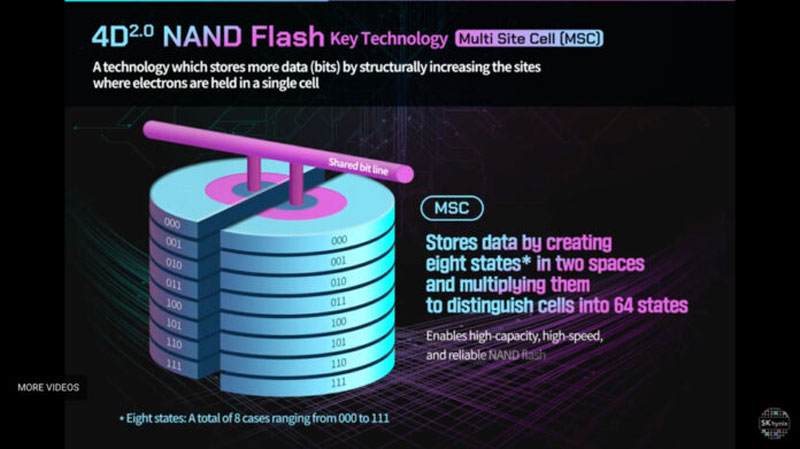

Предложение SK hynix как раз и является тем обходным манёвром, который позволяет без увеличения сложности контроллера и потери надёжности записать в каждую ячейку пять бит данных. Компания предлагает разделить ячейку на две равные половинки со своими адресными и управляющими линиями (что несколько усложнит производство, но не радикально). Процесс, названный Multi-Site Cell, позволит удерживать в каждой половинке ячейки 6 уровней заряда — это условно 2,5 ячейки. Параллельная обработка двух половинок даст 36 уровней, что можно свести к 32 уровням или записи 5 бит.

Утверждается, что представленная архитектура использует модификацию фирменной технологии 4D 2.0, над которой SK hynix работала как минимум с 2022 года. Распределение уровней между двумя половинками ячейки расширяет динамический диапазон, ускоряет операции чтения и записи и улучшает долговечность памяти по сравнению с традиционным PLC, где близкие уровни напряжения сильно ограничивают характеристики памяти.

По словам компании, она располагает рабочими образцами такой памяти и исследует возможность её массового производства. Компании Samsung, Micron, Kioxia и Sandisk также работают в этом направлении. По крайней мере, Kioxia (Toshiba) в своё время даже заплатила штраф тайваньской Macronix за якобы кражу технологии разделения ячеек NAND, которую назвала Twin BiCS Flash. Но даже Macronix не является изобретателем этой архитектуры. Она ей досталась по наследству от немецкой компании Qimonda (Infineon). Разработке не один десяток лет и, возможно, её звёздный час в лице PLC не за горами.

© 3DNews