Заказные блоки в микросхемах (Silicon IP): как это работает

В каждой статье на хабре, посвященной отечественным микропроцессорам, так или иначе поднимается вопрос лицензионных IP-блоков и того, насколько их наличие и отсутствие уменьшает ценность, отечественность или безопасность разработки. При этом очень многие комментаторы не слишком хорошо понимают предмет обсуждения, поэтому давайте попробуем разобраться, как же именно работает лицензирование в микроэлектронной индустрии, чем хороши и чем плохи лицензированные блоки, и в чем состоит процесс разработки микросхемы, если большая часть блоков в ней куплена.

Любая современная микросхема — это то, что некоторое время назад гордо называли «система на кристалле»: даже у трехногих линейных регуляторов и источников опорного напряжения есть скрытая от пользователя цифровая подстройка, что уж говорить о микропроцессорах и микроконтроллерах, содержащих десятки разнообразных блоков, разработка каждого из которых требует специфических навыков и большого опыта, чтобы обойти подводные камни, о которых не пишут в книгах и статьях. При этом любой проект, как правило, имеет свою killer feature, за счет которой разработчики рассчитывают получить преимущество над конкурентами, и именно эта killer feature должна быть сделана максимально хорошо, а все остальные блоки должны быть просто не хуже, чем у других.

Внимание, вопрос: нужно ли содержать дорогостоящую команду разработчиков, способную сделать самостоятельно вообще все нужные блоки?

Еще более интересный вопрос: если вы сами разработали систему команд микропроцессора, нужно ли содержать команду программистов, которая напишет для нее компилятор, портирует свежие ядра популярных операционных систем, сделает кучу другой тяжелой работы и, скорее всего, все равно не поставит ваше творение на один уровень с популярными архитектурами, над которыми трудится гораздо большее количество людей?

И самое главное: дадут ли положительные ответы на предыдущие два вопроса конкурентные преимущества вашему продукту?

Лирическое отступление

Пятого июня вышел на пенсию Моррис Чанг — человек, о которым вы никогда не слышали, но без которого не было бы современной электроники. Моррис Чанг родился в Китае, в разгар гражданской войны уехал в США, закончил MIT, а потом много лет проработал в Texas Instruments и General Instruments. В те годы неотъемлемой частью любой микроэлектронной компании было собственное производство, оборудование для которого стоило на несколько порядков дешевле, чем сейчас, но тем не менее, все равно было очень дорого. Вот как об этом писал сам Чанг:

When I was at TI and General Instrument I saw a lot of IC designers wanting to leave and set up their own business, but the only thing, or the biggest thing that stopped them from leaving those companies was that they couldn«t raise enough money to form their own company. Because at that time it was thought that every company needed manufacturing, needed wafer manufacturing, and that was the most capital intensive part of a semiconductor company, of an IC company. And I saw all those people wanting to leave, but being stopped by the lack of ability to raise a lot of money to build a wafer fab.

В 1985 году Моррис Чанг собирался выйти на пенсию, но вместо этого принял предложение правительства Тайваня поработать в Industrial Technology Research Institute, исследовательском институте, который должен был помочь совершить индустриальную революцию на Тайване и ликвидировать отставание тамошней экономики от развитых стран. В 1987 году, параллельно с работой в ITRI Чанг создал TSMC — компанию, выросшую в крупнейшего в мире производителя интегральных схем. Бизнес-модель TSMC изначально строилась на том, что компания ничего не разрабатывает, а только производит чужие разработки, и это был один из первых шагов в создании современной экосистемы разработки и производства микросхем, известной как Fabless-модель.

Конец лирического отступления

Что такое Fabless?

Fabless — это модель разработки и производства микросхем, в которой компания-разработчик не имеет собственного производства и пользуется услугами сторонней фабрики, также сотрудничающей с другими разработчиками (и иногда имеющей собственные продукты).

Наличие сторонних фабрик позволяет радикально уменьшить порог входа на рынок микроэлектроники (о чем и мечтал в свое время Моррис Чанг), с сотен до единиц миллионов долларов, за счет отсутствия необходимости покупать и обслуживать оборудование для производства. Оно же позволяет уменьшить этот порог еще дальше за счет формирования рынка поставщиков сложнофункциональных блоков (они же Silicon IP). Если вы производите чипы на собственной фабрике, то вы можете рассчитывать только на собственные силы и должны содержать команду, способную создать все нужные блоки. Если фабрикой пользуетесь не только вы, но и другие компании, то большинство типовых задач кто-то уже решил до вас, и вы можете воспользоваться результатами чужого труда — или перепродать собственное решение кому-то еще, предварительно договорившись о цене и условиях так, чтобы никто не остался в накладе. Разумеется, вы вряд ли будете продавать свое ноу-хау непосредственным конкурентам, но ситуаций, когда можно заработать, не ввязываясь в конфликт интересов, тоже предостаточно. Именно из возможности и желания переиспользовать результаты решения типовых задач возник рынок IP-блоков, размер которого по состоянию на 2017 год подобрался к четырем миллиардам долларов и продолжает бурно расти.

Чем это выгодно?

Покупателю IP — в первую очередь экономией. По разным оценкам, покупка IP-блоков обычно оказывается от двух до пяти раз дешевле самостоятельной разработки. Кроме того, покупка обычно позволяет существенно сократить время разработки, так как вам не нужно самостоятельно производить тестовые чипы и исправлять ошибки.

Разработчику IP — возможностью построить работающий бизнес на нишевом решении и существенно сократить расходы на ведение бизнеса. В стоимости микросхемы значительную часть составляют затраты на маркетинг, корпусирование, тестирование, техподдержку, прикладное ПО, наконец, на фотошаблоны для серийного производства, и т.д. и т.п. Если вы не производите готовые продукты, а только продаете блоки, то всех этих расходов у вас нет.

Фабрике — возможностью привлечь больше клиентов. Крупные фабрики стремятся создать вокруг себя экосистему поставщиков IP-блоков, потому что их использование позволяет существенно ускорить дизайн и, что не менее важно, максимально автоматизировать его. Богатое портфолио готовых компонентов — большое подспорье в дизайне конечного продукта, потому что оно позволяет самостоятельно делать только то, что является вашим know-how, и не тратить драгоценные ресурсы на разработку всего вообще — особенно в ситуации, когда уже есть готовое решение, разработанное людьми, вложившими в его разработку существенно больше времени и опыта, чем можете себе позволить вы. Соответственно, широкий выбор готовых IP может быть серьезным фактором в выборе той или иной фабрики для производства вашего проекта.

Как это работает?

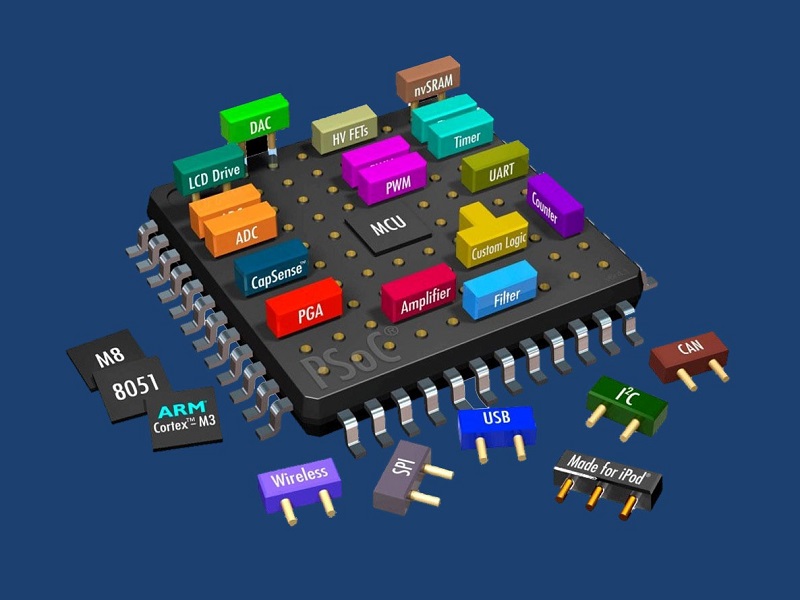

Давайте рассмотрим лицензирование ядер на примере сферической заказной системы на кристалле. Система будет содержать процессорное ядро, шины для объединения ядра и периферии, какое-то количество кэш-памяти, интерфейсы для общения с внешним миром (допустим CAN и I2C), PLL, ЦАП и АЦП. Для чистоты эксперимента допустим, что покупаться будет вообще всё, без самостоятельной разработки. «Глупое предположение», — скажете вы и будете не совсем правы. В реальности, конечно, такие ситуации крайне редки, но вс же вполне можно представить себе, что killer feature продукта будет не какой-то блок сам по себе, а специфическое сочетание уже существующих блоков. Например, вы первый покупатель блока (поэтому его еще нет у конкурентов) или придумали существующему блоку применение в нехарактерном для него сегменте (поэтому у конкурентов в этом сегменте нет ничего похожего).

Итак, начнем с…

нет, не с процессорного ядра, а с аналоговой обвязки. Для примера возьмем аналого-цифровой преобразователь (АЦП) — типовой блок большинства микроконтроллеров и любых других систем, имеющих дело с данными из внешнего мира.

АЦП — это аналоговый блок, а значит его параметры серьезно зависят не только от его схемотехники, но и от того, как именно эта схемотехника реализована на кристалле. Если мы возьмем готовый файл с топологией от одного техпроцесса и произведем его на другой фабрике с теми же проектными нормами, мы можем получить совершенно другие параметры (не говоря уже о переносе на другие проектные нормы). Впрочем, известная с середины века культура «вторых поставщиков» все же существует; например, фабрика Towerjazz предлагает копии некоторых техпроцессов TSMC.

АЦП — это отличный пример Hard IP — блока, привязанного к определенному технологическому процессу. Для того, чтобы купить такой блок, вы должны точно знать, на какой технологии будет производиться ваш конечный продукт, и, как уже упоминалось выше, наличие нужных Hard IP может быть для фабрики серьезным конкурентным преимуществом.

В каком виде поставляется Hard IP? Это интересный вопрос, и для ответа на него надо обсудить, в каком виде такой блок разрабатывается. В случае с большинством аналоговых блоков, разработка схемотехники ведется на уровне отдельных транзисторов, то есть выходными файлами будут файл электрической схемы и файл с топологией. При этом особенности и схемы, и топологии могут иметь серьезную коммерческую ценность, отдавать которую на сторону, конечно же, не хочется. А для того, чтобы клиент не смог реверс-инжинирить схему по топологии, топология обычно тоже не передается, поэтому в обычном случае поставляемые файлы выглядят следующим образом:

1) Вместо электрической схемы клиент получает высокоуровневую поведенческую модель, не раскрывающую особенности реализации. Такая модель может быть написана на языке Verilog-A. Альтернативный вариант — некоторые САПР (например Cadence Virtuoso) поддерживают шифрование электрических схем, то есть клиент сможет использовать вашу схему (или файл verilog-A), но не сможет открыть и посмотреть содержимое.

2) Габаритный макет топологии, с отмеченными внешними выводами и описанием того, сколько уровней металлизации занимает блок.

3) Тестовое окружение для верификации основных параметров.

4) Документацию.

При этом, разумеется, необходимо участие третьей стороны, которой вы сможете передать топологию, не опасаясь конкуренции и реверс-инжиниринга. Этой третьей стороной выступает фабрика, и ее роль посредника между заказчиками и исполнителями — важная часть экосистемы fabless разработки чипов. У фабрики, конечно же, должна быть кристально чистая репутация (это к вопросу о закладках) и, в идеале, она не должна самостоятельно производить ничего похожего, потому что работать на фабрике компании-конкурента — в любом случае сомнительное удовольствие. У Samsung получается производить процессоры одновременно себе и Apple, но другие крупные фабрики обычно или концентрируются на собственном производстве (как Intel), или совсем отказываются от самостоятельной разработки (как TSMC). Желание избавиться от этого конфликта интересов, кстати, было одним из драйверов выделения Globalfoundries (второго по размеру игрока на рынке фабрик) из состава AMD.

Лирическое отступление

В России, кстати, говоря, pure-play фабрик нет. Более того, для абсолютно всех игроков рынка выпуск собственной продукции является приоритетом, и все производимые fabless-разработчиками полностью отечественные микросхемы изготавливаются на производствах их потенциальных конкурентов — или на pure-play фабриках за рубежом.

Конец лирического отступления

Дальше есть еще одна важная деталь взаимодействия поставщика и фабрики: фабрика заносит ваш IP-блок в собственную базу и в дальнейшем проверяет все входящие проекты на наличие в них вашей топологии (которую кто-то мог получить как от вас, так и нелегально), и сверяется с вами относительно того, есть ли у запрашивающего производство лицензия (так как многие дешевые лицензии подразумевают использование блока только в одном проекте). Наличие проверки фабрикой позволяет разработчику Hard IP выбрать любой удобный вариант лицензирования — привязанный к количеству проектов, к количеству проданных чипов, к срокам запуска чипов в производство и т.д. и т.п. Но подробнее о типах лицензий — в следующей части.

Как Hard IP в типовой системе на кристалле нужны будут АЦП, PLL, физические уровни интерфейсов ввода-вывода.

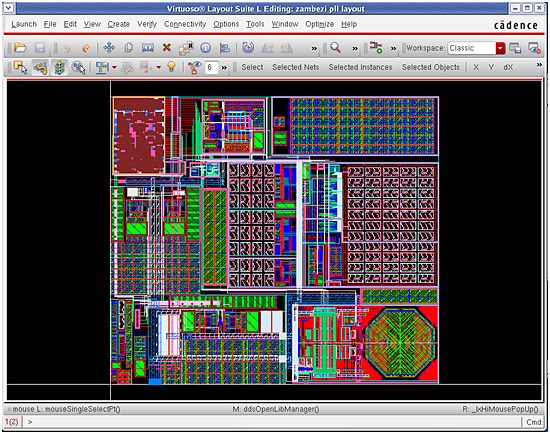

Окно САПР Cadence Virtuoso Layout Suite с топологией аналогового Hard IP блока (это PLL, если кому-то интересно). Хорошо видны границы между отдельными подблоками (которые обычно делают разные люди) и, например, очень редкий для интегральных микросхем элемент — катушка индуктивности в правом нижнем углу. А слева вверху виден цифровой блок (наверное, управление) и его многобитный интерфейс к остальной части.

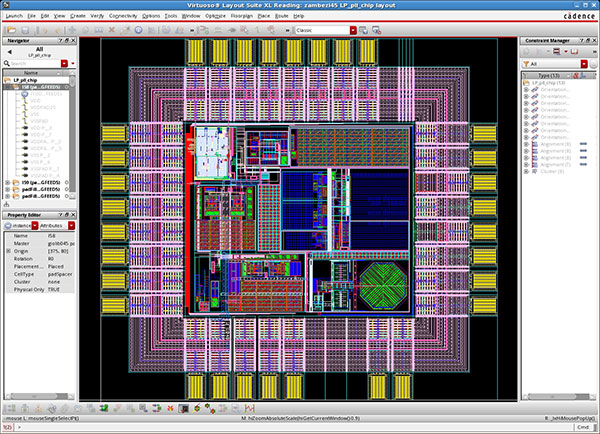

Оно же, но уже в виде готового чипа (например, для тестирования). Хорошо видны площадки ввода-вывода и соединяющие их кольца из земель и питаний.

Термин «Hard IP» также используется применительно к IP-блокам для FPGA. В этом случае подразумевается, что код блока был оптимизирован для использования в конкретной модели FPGA и синтезирован для размещения в ней.

Soft IP

Следующий блок, который мы рассмотрим — это процессорное ядро. Собственно, на его месте может быть практически любая цифровая схема, например, блок кодирования сигнала кодом Рида-Соломона, но процессорные ядра больше всего на слуху и они же составляют добрую половину всего рынка (в том числе в силу сложности и дороговизны).

Основное отличие разработки цифровых схем от разработки аналоговых состоит в том, что цифровые схемы обычно пишутся на специальных языках высокого уровня — Verilog или VHDL, а дальше специальный САПР синтезирует из этого кода электрическую схему и топологию. Так вот, до момента синтеза код не привязан к конкретной технологии, и один и тот же блок можно произвести на разных фабриках (или зашить в ПЛИС) или на разныз вариантах одной и той же технологии (например, оптимизированных под высокую скорость или низкое энергопотребление). Этим, собственно, и пользуются компании-разработчики, такие как, например, ARM. Такие цифровые блоки, не привязанные к определенной технологии, называются Soft IP.

Вот так выглядит схема одного бита сумматора:

А вот так на самом деле выглядит восьмибитный сумматор в дизайне микросхемы:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

Как видите, ни слова ни про размер транзисторов, ни про фабрику, ни про скорость работы. Все эти вещи появляются позже, когда покупатель IP-блока начинает самостоятельно заниматься его переводом в кремний.

Что получает покупатель Soft IP? Посмотим на два примера:

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation — integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

В первом случае вы получаете исходный код и все необходимое для его моделирования и самостоятельного синтеза топологии, во втором — защищенный от чтения нетлист, который вы не можете изменить и части которого вы не можете переиспользовать (что не редкость для IP с предоставляемым исходным кодом). Разумеется, второй вариант в обычной ситуации существенно дешевле. Но могут быть и варианты, когда кодирование используется для защиты каких-то ноу-хау, которых нет в более простой версии устройства, поставляемой в виде исходного кода.

Например, так обстоит дело с процессором Европейского Космического Агентства LEON3:

1) Разработчик процессора, Cobham Gaisler, поставляет базовую версию LEON3 даже под лицензией GPL

2) Они же поставляют версию LEON3FT (защищенную от одиночных сбоев на уровне схемотехники): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

3) Само Европейское Космическое Агентство (на деньги которого делался изначальный дизайн) лицензирует исходный код предыдущей версии, LEON2FT, участникам своих проектов.

Промежуточные варианты защиты исходного кода могут, например, включать Verilog-код, прошедший обфускацию с целью невозможности его изменения и переиспользования отдельных частей. Техники обфускации Verilog-кода могут варьироваться от простого удаления комментариев и переименования переменных, чтобы код стал нечитабелен, до внедрения в блок специальных конечных автоматов, переводящих блок в нештатный режим работы, если при запуске схемы на вход им не пришла ключевая последовательность символов. В обфусцированный код также могут быть добавлены digital watermarks, которые позволяют на модели или готовом чипе проверить, использовано ли в нем конкретное IP.

Тем не менее, передача «Clean, readable, synthesizable» исходного кода является распространенной практикой, особенно в ситуации, когда разработчик может удобно проконтролировать использование IP блока в продуктах покупателя. Это, в частности, означает, что при желании вполне можно проверить исходный код купленного ядра на отсутствие в нем недокументированных возможностей (они же закладки, они же hardware trojans) и дальше быть уверенным, что оно не менее безопасно, чем ядро, разработанное самостоятельно.

Внимание, вопрос: если soft IP не привязаны к конкретной фабрике, то кто та третья сторона, которая обеспечивает выполнение лицензионного договора? Это весьма больной вопрос, и ответ на него может сильно отличаться в зависимости от типа Soft IP, размеров компаний продавца и покупателя, целевых рынков и т.д. и т.п… Вот несколько примеров:

ARM, другие разработчики микропроцессорных ядер или больших блоков, которые серьезно влияют на функциональность, основывают лицензионный контроль на том, что продавая вашу систему на кристалле, вы должны ее рекламировать (тайно продать большой объем чипов не очень просто), а значит выпустить новую модель на рынок без ведома разработчика IP будет непросто, равно как будет непросто самостоятельно написать что-то очень похожее, но все же немного отличающееся, и дальше продавать уже его. В случае возникновения вопросов в игру вступит внушительных размеров юридическая служба компании. Примерно так же работает еще и продажа и лицензирование патентов (и, как вы наверняка знаете, несмотря на многомиллионные отчисления крупных компаний друг другу, из судов их юристы не выходят практически никогда). Примерами такого рода лицензионных споров является недавняя история с отказом Apple от графических ядер Imagination Technology в пользу in-house разработки и исков на предмет того, что Apple не могли ничего разработать так, чтобы не нарушить лицензионые соглашения и патенты Imagination (особенно с учетом перехода значительной группы сотрудников из одной компании в другую).

Кроме того, распространенный пункт в лицензионных соглашениях — согласие на внешний аудит для подтверждения количества произведенных чипов (потому что оплата многих IP включает роялти с каждого проданного чипа) или количества разрабатываемых проектов (для случаев с попроектными лицензиями).

В случае с soft IP для FPGA, третьей стороной могут выступать вендоры, поставляющие сами ПЛИС и софт для моделирования и программирования. Например, софт и ПЛИС от Xilinx поддерживают не только шифрование исходных кодов IP, но и лицензии для только моделирования (без возможности прошить дизайн в ПЛИС) и даже такие лицензии, когда дизайн можно прошить в ПЛИС, но через некоторое время эта прошивка перестанет работать (то есть вы можете отлаживать прототипы в железе, но не можете выпустить серийный продукт).

Лирическое отступление относительно процессорных ядер и типов лицензий

Подробности лицензирования обычно составляют коммерческую тайну, но тем не менее, основные принципы хорошо известны.

Самая дешевая лицензия — на использование IP-блока один раз в одном проекте. Ее стоимость может оплачиваться целиком при покупке, а может иметь роялти-часть, привязанную к количеству проданных чипов. Также стоит заметить, что иногда покупатель IP, в свою очередь, передает продукт дальше как IP большего размера, и могут сложиться ситуации, когда разработчику исходного IP выгоднее заключить лицензионное соглашение с конечным потребителем (а иногда даже с разработчиком продукта, в котором будет использована микросхема); все зависит от того, на каком этапе удобнее проконтролировать количество произведенных чипов и кому из покупателей бизнес-модель лучше позволяет платить роялти.

Более дорогой вариант предыдущей лицензии — на использование одного блока в нескольких проектах сразу. Такая лицензия обычно используется при создании семейств микросхем, сходных по параметрам (и потому не требующих различной оптимизации IP).

Следующий вариант — лицензия на пользование ядром или семейством ядер на определенный срок. Он лучше подходит большим компаниям, которые работают над многими проектами одновременно, и которым удобнее заплатить один раз вместо того, чтобы заключать отдельный контракт на каждый проект. Среди прочего это позволяет сокращать сроки запуска — как раз на время переговоров по лицензированию. Разумеется, такая лицензия намного дороже разовой, поэтому для маленьких компаний она обычно нецелесообразна.

Вариант предыдущей лицензии — подписка на определенный срок, но не на конкретный блок, а на целый класс блоков или ядер (допустим, на все ARM Cortex). Подписка дает дизайнерам большой компании больше свободы и удобства в выборе нужного варианта — опять же, не тратя время на переговоры и согласования.

Самый дорогой вариант — архитектурная лицензия. Системы команд (или, чаще, их составные части) патентуются и защищаются, так что единственный способ самостоятельно сделать совместимое ядро — получить на это разрешение у правообладателя (или сделать ядро, совместимое со старой версией системы команд, на которую уже истекли патенты). Зачем это нужно? Архитектурная лицензия нужна для тех редких случаев, когда именно производительность ядра (или какие-то другие его специфические свойства, например, встроенное дублирование или троирование) является вашим конкурентным преимуществом. При этом вы, разумеется, должны обладать компетенциями в разработке ядер, как минимум не хуже, чем у лицензиара, а в вашей предметной области — даже лучше.

Почему бы в таком случае не разработать собственную систему команд? Ответ на этот вопрос очень прост: собственная система команд означает необходимость написания собственных компиляторов и всего сопутствующего софта, а также сложности с тем, что под популярные архитектуры все умеют программировать, а под вашу нет. В итоге даже такие большие компании, как Apple, предпочитают архитектурные лицензии ARM разработке чего-то своего, и выход новых игроков на рынок архитектур, поделенный между несколькими грандами (точнее, между ARM и подбирающими остатки всеми остальными) — чрезвычайно редкое явление.

Здесь мы плавно возвращаемся к вызывающему самые острые дискуссии вопросу про собственную архитектуру процессора: для того, чтобы вы могли продать микросхему, она должна быть максимально удобной для пользователя, а это значит, что под нее должно быть максимальное количество уже готового или легко адаптируемого софта, а также должны быть в наличии программисты, умеющие работать с вашей системой команд (потому что просить клиентов переучивать своих программистов — сомнительная идея). В итоге получается, что покупка лицензии на микропроцессорное ядро несет одновременно улучшение потребительских качеств микросхемы и сокращение как ваших расходов, как и расходов ваших клиентов. В качестве примера я, пожалуй, приведу компанию Apple, которая известна в том числе тем, что разрабатывает микроархитектуру своих мобильных процессоров самостоятельно, но! Эти процессоры все еще используют систему команд ARM, несмотря даже на то, что Apple имеет собственную операционную систему и в теории может использовать для нее процессоры с любой системой команд. Видимо, найти толковых разработчиков с опытом на ARM проще и выгоднее. То же самое, кстати, касается и персональных компьютеров Apple — они много лет выпускались с процессорами архитектуры PowerPC, но когда стало ясно, что PowerPC необратимо отстает от x86, Apple ценой значительных усилий совершили переход на процессоры Intel.

Конец лирического отступления

Маленьким разработчикам Soft IP непрактично содержать штат юристов, поэтому они обычно строят свою бизнес-модель так, чтобы контроля использования IP не требовалось или он был минимален. Основных варианта тут два:

1) Продавать достаточно дорого, чтобы окупать ядро по принципу «один клиент — одна продажа», без заморочек с роялти.

2) Строить бизнес-модель на кастомизации IP под конкретный проект клиента (например оптимизации производительности под типовые задачи), помощи в сопряжении с другими IP, аутсорсе синтеза IP в топологию (так называемый IP hardening) и так далее. Как это работает? Например, базовый дизайн микропроцессорного ядра может быть дополнен специфическими аппаратными блоками для часто используемых клиентом операций, или наоборот, структура конвейера может быть упрощена для экономии энергии в задачах с батарейным питанием.

В качестве soft IP в типовую систему на кристалле нужны микропроцессорное ядро (или ядра), процессорные шины для объединения ядер и периферии, контроллеры интерфейсов, аппаратные ускорители и т.д. и т.п.

Configurable IP

Еще один тип IP, находящийся между hard и soft — это конфигурируемые ядра, хорошим примером которых являются компиляторы памяти. Типичная многоядерная система на кристалле может содержать десяток блоков кэш-памяти разного объема и конфигурации, и еще флэш-память для хранения программ или подстройки. Как быть в этой ситуации? Покупать десять разных, хоть и однотипных IP-блоков? Разрабатывать память самим?

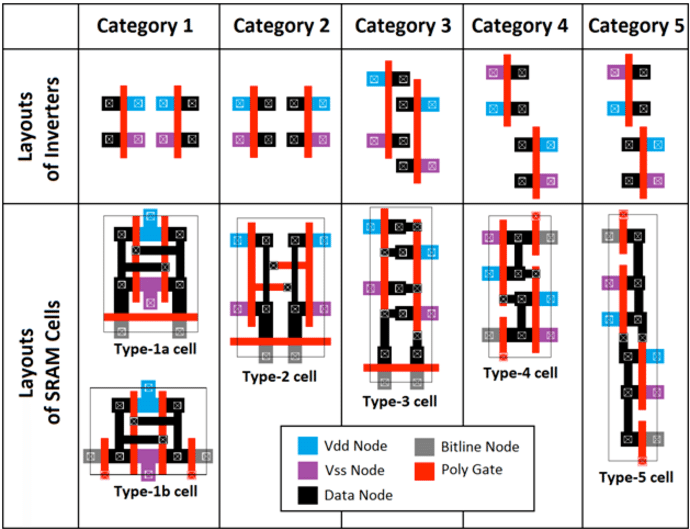

Для регулярных структур (всех видов памяти, разнообразных кодеров и встраиваемых FPGA) этот вопрос решается созданием конфигурируемых блоков, для которых пользователь может задать размер массива, внешние интерфейсы, конфигурацию топологии и некоторые другие параметры. В связи с тем, что ключевой элемент массива обычно привязан к технологии, такие IP-блоки являются разновидностью Hard IP, но все же обладают рядом свойств Soft IP (в частности, гибкостью).

Это все — разные варианты топологии стандартной шеститранзисторной ячейки кэш-памяти.

Foundation IP

Еще один «около-hard» тип IP-блоков — это foundation IP, совсем маленькие строительные блоки для конкретной технологии. Типичная библиотека логических вентилей — это несколько сотен элементов, от простейших инверторов до сложных триггеров с функциями диагностики. Такая библиотека может быть оптимизирована для низкого энергопотребления, высокой скорости работы или минимальной площади на кристалее, для работы с разными напряжениями питания, при разных температурах или, например, под воздействием радиации. И, разумеется, для каждого техпроцесса (даже с одинаковыми проектными нормами) нужна своя библиотека, потому что свойства транзисторов (такие, как пороговое напряжение и паразитны емкости) и минимальные размеры элементов различаются у всех производителей. Существуют и «generic» библиотеки с намеренно загрубленными размерами, чтобы уложиться в любой техпроцесс с подходящими нормами, но их параметры, разумеется, хуже, чем у специализированных решений.

Кроме библиотек логических элементов к Foundation IP относят библиотеки элементов ввода-вывода, библиотеки элементов электростатической защиты и, зачастую, блоки памяти из предыдущего пункта.

Любимый BarsMonster массив базовых элементов в топологии.

Verification IP

Итак, все блоки куплены, осталась самая малость — убедиться, что они нормально взаимодействуют между собой и что ваша система соответствует всем необходимым стандартам. Соответствие стандартам, кстати, касается и блоков, разработанных вами самостоятельно. Думаю, никому на хабре не нужно объяснять важность хорошего тестового покрытия и полноценного тестирования кода, а также трудоемкость создания хорошего тестового окружения. А теперь представьте, что ваш код немного по-разному исполняется при изменении температуры окружающей среды. И на разных экземплярах абсолютно одинакового «железа». И при разном напряжении питания.

Задачи тестирования и проверки соответствия популярным стандартам подчас настолько сложны, что привели к появлению целого класса полупроводниковых заказных блоков — Verification IP. Эти блоки — это тестовое окружение, они не производятся в кремнии, но их рынок довольно велик (и продолжает расти с усложнением типовых продуктов). Многие разработчики микросхем знают компанию Synopsys как второго по размеру производителя САПР, гораздо меньше людей знает, что четверть бизнеса Synopsys — это IP-блоки. На популярном ресурсе по поиску IP Design&Reuse в портфолио Synopsys 828 Silicon IP (включая процессорные ядра ARC — вторые по популярности после ARM) и 116 Verification IP на все случаи жизни.

Для нашей сферической системы на кристалле потребуются verification IP для интерфейса CAN, для шин внутри процессора (например APB и AHB в случае с использованием ARM) и что-нибудь еще по мелочи. Тестовое окружение для аналоговых блоков и процессорного ядра, скорее всего, будет идти с ними в комплекте, а для всей системы целиком тесты придется писать самостоятельно.

А что мы?

Тут мы плавно подходим к вопросу, а в чем, собственно, состоит наша работа, если все блоки для системы были куплены? Давайте загибать пальцы.

Задачи по разработке следующие:

Собрать полную схему устройства, проверить его работоспособность (с привлечением сторонних verification IP и их самостоятельно написанных аналогов).

Опционально — прототипировать и отладить ключевые цифровые части в ПЛИС.

Собрать план расположения блоков на кристалле (это не такая тривиальная задача, как может показаться).

Синтезировать все Soft IP под нужный техпроцесс, проверить их работоспособность.

Собрать и отладить топологию микросхемы с учетом длинных соединений между блоками, возможной просадки напряжения на шинах питания, согласования длины линий в многоканальных шинах и еще множества разнообразных факторов.

Экстрагировать паразитные параметры из топологии, проверить работоспособность устройства еще раз, переработать критические пути распространения сигналов.

Произвести окончательные проверки соответствия топологии и электрической схемы, а также топологии и правил проектирования выбранной технологии.

Исправить косяки топологии, которые найдет приемка на фабрике (а она найдет).

В комментариях к недавней статье про печатные платы развернулась довольно интересная дискуссия об автотрассировщиках топологии и о том, когда разумно их использовать, а когда нет (применительно к любительским и профессиональным проектам). В качестве примера проекта, ради которого стоит потратить значительное количество человеко-часов на настройку автотрассировщика, привели «плату с парой-тройкой BGA по 400–700 выводов и несколькими сотнями других компонентов». А теперь представьте, что у вас имеется десяток Hard IP-блоков с 400–700 выводов, и еще, скажем, миллион других компонентов по 4–8 выводов (логика, из которой состоят блоки Soft IP). Большая ли это работа — собрать такую топологию из уже готовых блоков? Примерно такая же, как собрать печатную плату с уже готовыми микросхемами. И ведь никто не пеняет разработчикам печатных плат тем, что они берут уже готовые микросхемы и «всего-навсего» собирают их вместе.

На рисунке — пример окна САПР Synopsys IC Compiler с автоматически сгенерированной небольшой топологией и подсвеченным критическим путем распространения сигнала, который было бы неплохо подправить.

Кроме этого, есть задачи вне разработки — правильная постановка задачи по разработке, организация производства, корпусирования, сертификации, адаптация существующего ПО, разработка отладочных плат и референсных дизайнов, маркетинг наконец.

Микросхему мало разработать, ее надо еще произвести и продать, и одним из ключевых драйверов современного рынка fabless-разработки и продажи IP-блоков стало именно разделение компетенций разработки, производства и продажи микросхем, позволившее представителям всех трех отраслей сконцентрироваться на профильных для них задачах, одновременно превратив конкуренцию в кооперацию и сэкономив огромное количество денег за счет аутсорса непрофильных активностей. Именно поэтому, видя рассказ о том, что в новом отечественном (или «отечественном») процессоре куплено все, что можно, можете смело понимать: люди, которые его делают, умеют считать и экономить деньги, а если все свое и доморощенное, значит, первым требованием была не экономическая эффективность, а какие-то другие соображения. Возможно, не менее важные, но — другие.

И напоследок три небольших бонуса

Первый бонус: есть ли Open Source?

В целом рынка/коммьюнити Open Source в полупроводниковой индустрии не сложилось. Скорее всего потому, что из-за высокой стоимости валидации (производства в кремнии и измерения параметров) разработка требует значительных инвестиций, и участие в ней энтузиастов-одиночек практически исключено. А коммерческие компании, разумеется, должны как-то возвращать инвестиции. Впрочем, есть и исключения, о двух из которых я расскажу.

Первое — Opencores.org

Этот сайт и коммьюнити существуют уже почти двадцать лет и добились некоторых полезных ре