Универсальный контроллер моторов на ARM Cortex-M85. Трассировка

Новейшее семейство микроконтроллеров RA8M1 просится быть использованным в умном электроприводе. Вычислительная мощь ядра ARM Cortex-M85 (480 МГц) позволяет легко управлять на нашей плате одновременно двумя PMSM/BLDC или тремя DC коллекторными моторами с использованием алгоритмов машинного обучения и еще оставляет ресурс для комплексной удаленной диагностики в реальном времени. Добавим сюда IoT на ESP32-С6, дисплей, интерфейсы энкодеров, полевые шины и в результате получаем универсальный контроллер моторов.

Контролер рассчитан на управление моторами с максимальной суммарной мощностью 800 Вт без активного охлаждения. Способы управления могут быть самыми разными: векторное безсенсорное, скалярное безсенсорное, с обратной связью по квадратурному энкодеру, с обратной связью по датчикам Холла, с обратной связью по аналоговому сигналу положения, с управлением по обратной ЭДС и прочие. Акустические и вибрационный сенсоры улучшают управление и являются источниками данных для машинного обучения. Контроллеры могут объединяться в сеть через интерфейсы: CAN, RS485 и беспроводные: BLE, Wi-Fi, Zigbee, Thread.

Схемотехника

Схемотехника в основном повторяет предыдущий проект контроллера. Вместо одного 3-фазного драйвера поставлено два. BLE/Zigbee/Thread чип заменен на модуль BLE/Zigbee/Thread/Wi-Fi.

Схема одного из каналов управления мотором

Трассировочный интерфейс под адаптер J-Link

Поскольку ядро новое, то возможны многие аппаратные и недокументированные баги. Поэтому кроме обычного отладочного SWD интерфейса (клок до 25 Мгц) на плате установлен трассировочный интерфейс (клок до 60 МГц). Трассировочный интерфейс сильно сокращает расход времени на отладку. Он позволяет быстро находить точки сбоев, аномальные потоки прерываний, переходы в запрещенные области памяти, места зависаний, баги периферии и т.п., упрощает профайлинг и оптимизацию кода.

Плата выполнена на 6-слойном стеке

Предыдущий контроллер был сделан на 4-слойном стеке с 0.3 мм минимальными отверстиями и 0.15 мм дорожками и зазорами. Текущий контроллер должен выдерживать большие амплитуды токов и следовательно ему нужно уменьшать сопротивление полигонов раза в два. Это можно сделать увеличив толщину меди или увеличив количество слоёв. Увеличение количества слоёв на два слоя или увеличение толщины меди в два раза по оценке калькулятора PCBWay обойдётся почти в одинаковую сумму. Но увеличение толщины меди до 2 oz потребует увеличить зазоры до 0.2 мм , а это уже критическая проблема при трассировке микросхемы главного микроконтроллера и других микросхем с повышенной плотностью выводов. Поэтому остаётся только вариант увеличения числа слоёв. Ещё хорошо то, что при 6 слоях появляется возможность уменьшить излучаемые платой помехи. Для этого применяем экранирующие полигоны и уменьшаем площади токовых петель.

-

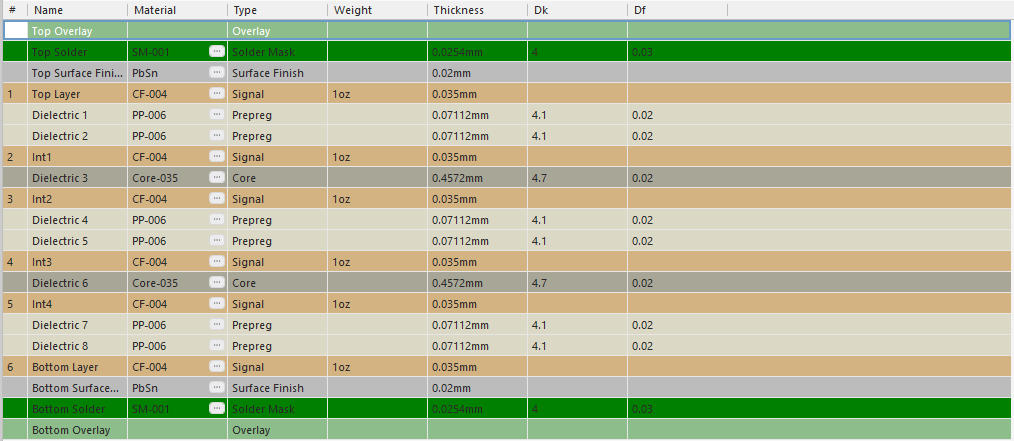

Спецификация стека платы

Спецификация стека платы выглядит так:

Плэйны не используются

Плэйны (т.е. слои со сплошной заливкой медью) всегда делают, когда на плате стоит быстрый процессор с внешней памятью. Но здесь я их не применяю, поскольку плата гибридная. Она совмещает и силовые цепи и высокоскоростные цифровые. В таких случаях плэйны заменяются полигонами, поскольку всю площадь платы заливать плэйном не нужно. Физически полигоны ничем от плэйнов не отличаются, но в Altium операции с плэйнами отличаются от работы с сигнальными слоями. В плэйнах работают с рисованием разрезов, а в слоях обычно работают с рисованием дорожек и контекстные инструменты соответственно разные. Имея это в виду можно спокойно заменить плэйн большим полигоном. Волновые сопротивления Altium умеет считать и относительно полигонов.

Одна из целей — уменьшение паразитных индуктивностей.

Нет ничего хуже на плате чем паразитные индуктивности дорожек и полигонов. Это они ответственны за огромные наносекундные выбросы на наблюдаемых осциллограммах сигналов в силовых цепях. Благодаря тому что у платы 6-слойный стек можно дополнительно предпринять некоторые меры по уменьшению паразитных индуктивностей.

Схема выходного каскада с паразитами

Снижаем индуктивность линий сигналов управления затворами силовых транзисторов. Ниже пример трассировки сигналов W и HSW. Это управление затвором верхнего транзистора. Звон в его затворе может затягивать время коммутации, а значит и потери. Кроме того становится трудно минимизировать мёртвое время. Плюс этот же сигнал идёт на измерительные цепи. Чем короче звон, тем больше есть время на измерение и тем выше можно выставить частоту коммутации.

Проводим дорожки во внутренних слоях разделённых тонким препрегом в 0.14 мм. Ниже показана конструкция дорожек. Площадь токовой петли доведена до минимума. Индуктивность стала меньше в несколько раз по сравнению с обычным решением, когда дорожки идут не параллельно.

Линии управления приближаются по топологии к дифференциальным

Стоит ли всеми силами увеличивать ширину дорожек к затворам? Уменьшение погонной индуктивности параллельных дорожек пропорционально корню квадратному от увеличения ширины. Т.е. увеличив ширину в 4 раза индуктивность уменьшится в два раза. С этой точки зрения усилия по увеличению ширины не окупятся, если это приведёт к сужению силовых дорожек. Сопротивление дорожек не имеет особого значения, поскольку основное сопротивление вносит драйвер.

Этапы трассировки

Как художник рисует картину с набросков, так и плата трассируется поначалу набросками дорожек. Можно, конечно, и сразу ложить полигоны на шины с большими токами, но тогда надо быть готовым часто их перерисовывать. Нельзя просто так взять и сразу нарисовать правильный полигон, да ещё до трассировки остальных цепей.

Чтобы случайно не возникло конфликтов пересечения пространств, где намечены полигоны, мы прокладываем дорожки, которые после укладки полигонов удалим. Чтобы позже вспомогательные дорожки удалить все и разом присваиваем им специфическую ширину, например 0.444 мм или 0.333 мм. Потом такие дорожки легко выделяются по критерию ширины и удаляются.

Расстановка переходных

Часто хочется заранее уменьшить количество переходных отверстий (via). Ничего хорошего они в сигнал не привносят. Но лучше все же не экономить на переходных и сразу ставить их стройно и оптом. Упорядоченность переходных сослужит хорошую службу если вдруг нагрянет тюнинг изготовленной платы (а он точно нагрянет) или вдруг надо будет достать щупом сигнал, который не планировали исследовать.

Микросхемы ставим так чтобы их легче было перепаять. Поэтому многие микросхемы стоят на обратной стороне платы подальше от разъёмов, которые плавятся от горячего воздуха. Процессор оставляем сверху чтобы иметь возможность измерять сигналы на его выводах в рабочем положении платы.

Создание правил в Altium Designer

Правила сильно облегчают трассировку. Вместо того чтобы постоянно держать в уме кучу ограничений и факторов при трассировке, программа просто не даст проложить дорожки с нарушением ограничений указанных в правилах. Но и правила надо уметь создавать.

Устанавливаем зазоры для пустых падов.

У микросхем бывают неподключенные пады. Но общее правило зазоров не делает различий между подключёнными и неподключенными падами. Хотя к неподключенным зазор может быть меньше.

Предупреждение о нарушении общего правила зазоров

Вот, например, как реагирует программа на недостаточный зазор к неподключенному паду. Чтобы уменьшить зазор к неподключенным падам нам придётся сделать класс неподключенных падов.

Создание класса неподключенных падов

Правила для класса неподключенных падов

Создав класс неподключенных падов создаём приоритетное правило с уменьшенными до технологического минимума зазорами только для этого класса.

Тут сразу надо помнить о том, что созданные правила в Altium не рефакторятся автоматически. Поменяв позиционные обозначения элементов придется идти в правила и переписывать там вручную идентификаторы объектов.

Правил должно быть много

В иерархических схемах, как наша, не работают общие правила для именованных цепей в субблоках. Если нужно описать уменьшенные зазоры между цепями с малой разницей потенциалов, то приходится делать правила для каждого субблока отдельно. Ниже пример как сделать правило для зазоров в цепи управления затворами верхних транзисторов. Приходится делать отдельные правила для каждой фазы и для каждого субблока.

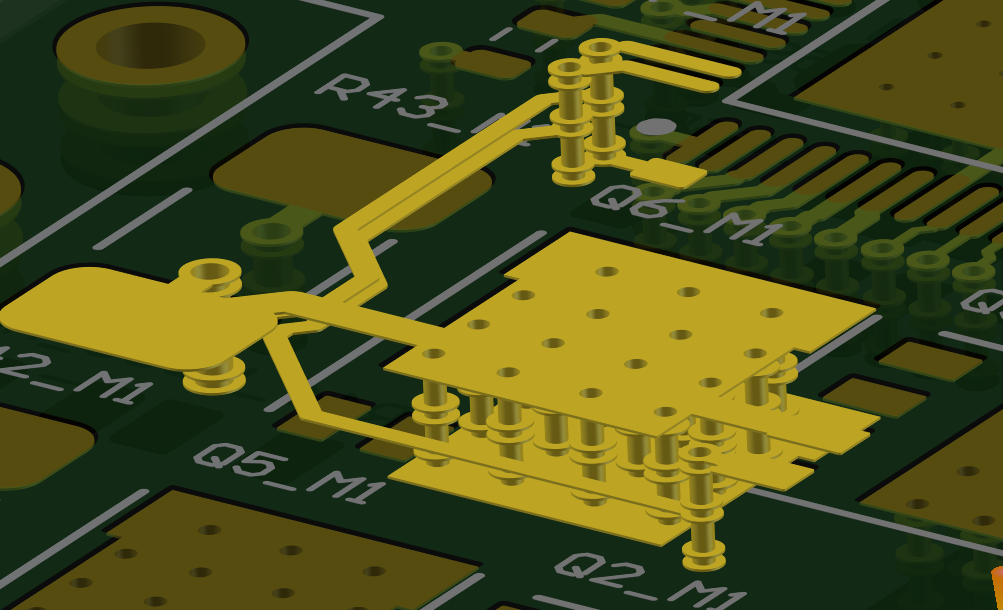

Результат трассировки

Полигоны на изображении платы сделаны прозрачными для лучшей визуализации дорожек.

Программирование

Программироваться контроллер будет с использованием уже достоточно развитого фреймворка на основе Azure RTOS, взятого из предыдущего проекта.

Необходимо будет только перенести исходники с Synergy Software Package (SSP) на Flexible Software Package (FSP)

Краткое демо по освоению FSP было дано здесь. Среды разработки для обоих пакетов: SSP и FSP — практически одинаковы. Периферия также имеет минимальные отличия.

В архитектуре чипов Renesas особенно привлекает унифицированность и гибкость таймеров (разбор нюансов архитектуры тут и тут). Все ШИМ таймеры имеют одинаковый набор регистров и одинаковую архитектуру, в отличие от, например, STM32Hxxx, где можно найти до 7 разных архитектур таймеров. Избыточное разнообразие сильно усложняет планирование многоканального управления моторами.

Наш контроллер по существу двухпроцессорный, второй процессор находится в модуле ESP32-С6. Модули ESP32 имеют очень ограниченное число пинов и все они ушли на интерфейсы SDIO, UART, JTAG. Через SDIO есть надежда разогнать Wi-Fi канал связи у главного микроконтроллера до 50 Мбит/сек. Такая скорость понадобиться для удаленной отладки алгоритмов управления моторами и модуляции. С более продвинутыми модулями можно было бы получить скорость до 100 Мбит/сек. Но ESP32 вне конкуренции по цене и могут ещё разгрузить основной микроконтроллер от некоторых дополнительных функций.

Схема контроллера планируется к публикации позже, после запуска демопроектов.