Сколько стоит для студента микросхему выпустить?

Всем нам известна проблема курицы и яйца: работодатели не хотят брать на работу выпускников без опыта работы, но где же в таком случае выпускникам получить опыт работы? В микроэлектронике эта проблема стоит особо остро ввиду требуемого огромного количества специфического опыта. Наши ВУЗы с советских времен знамениты широчайшей теоретической подготовкой, которая должна помочь выпускнику в любой сложной ситуации в жизни. Однако, современная индустрия требует практического опыта. Добавим сюда еще отсутствие мотивации, приводящее к тому, что по специальности работает процентов 15% выпускников, и получим жесточайший кадровый голод в отрасли, которая очень требовательна к качеству кадров. А ведь если бы каждый студент мог «поморгать лампочкой» со своего собственного кристалла ситуация могла бы развиваться совсем иначе.

Рисунок 1. КДПВ

Что же мешает таким грандам подготовки кадров отечественной микроэлектроники, как, например, МИФИ и МИЭТ, поступать аналогично своим зарубежным коллегам (например, MIT или UZH), а именно — давать возможность студентами-дипломникам выпускать свои собственные кристаллы? Можно, конечно, предположить, что выпуск собственного кристалла занятие крайне долгое, сложное и дорогое, а потому для института — дорого, а для студента — непосильно. Однако, это не так. Давайте же взглянем на одну из доступных технологий на отечественном рынке микроэлектроники, знакомство с которой позволит студенту стать значительно более привлекательным в плане будущего трудоустройства, а предложение которой для студента — позволит университету значительно поднять свой рейтинг в глазах абитуриентов и работодателей.

БМК — это базовый матричный кристалл. Понятнее не стало? Тогда сделаем шаг в сторону и посмотрим на сильно упрощенный цикл производства заказной микросхемы (ASIC):

- Разработка описания схемы

- Создание топологии

- Передача технологических файлов заводу и ожидание готовности кристаллов

- Измерений полученных кристаллов

- Корпусировка

- Продажа

Очень «длинных» пунктов здесь два — разработка схемы и ожидание результатов работы завода. Для сокращения времени разработки применяются различные методологии, а в студенческой среде наилучшее решение — командная работа, однако нас интересует второй пункт — время работы завода. В силу того, что микроэлектронный завод это очень сильно инертное производство, всё должно быть по плану. Не успели к дате запуска производства? Следующая попытка через квартал. Само производство в зависимости от сложности изделия может длиться до полугода. Причем эти полгода — это утвержденный производственный цикл на высокоавтоматизированных станках, а не разгильдяйство персонала. Как же можно снизить эти сроки? Путём внесения некоего общего базиса во все производимые схемы, чтобы этап внесения различий был быстрым.

Этим общим базисом и является БМК — кристалл с заранее расположенными транзисторами, функциональное назначение которого определяется слоями металлизации, которые позволяют выполнять межсоединения транзисторов. Эти межсоединения и формируют уникальные функциональные возможности кристалла.

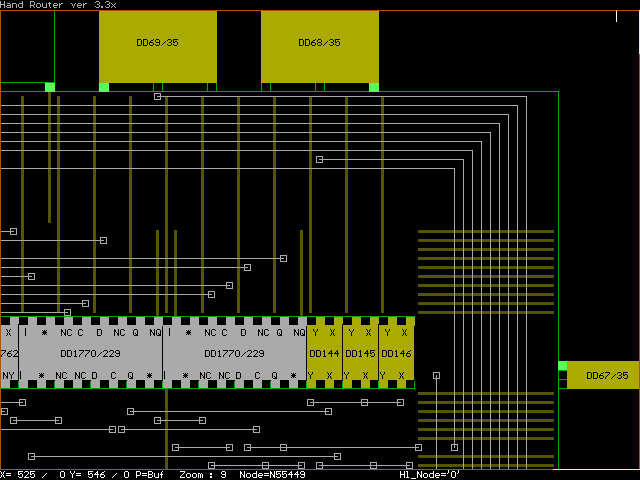

Рисунок 2. Hand Router v3.3, родом из недр НИЦЭВТа, создан в 1980х-1990х годах.

На одном БМК, используя разные схемы металлизации, можно выпускать сотни различных микросхем для различных организаций. Для завода в таком случае сам БМК становится массовым серийным изделием, а финишные этапы — слои металлизации, могут оперативно изменяться по требованиям заказчика. Таким образом получаем более частые «запуски» новых изделий в производство и снижение цены. Для студенческой разработки оба данных пункта крайне актуальны.

Давайте сравним пользу от применения различных методик обучения и посмотрим, что даёт наибольший эффект при наименьших затратах.

Таблица 1. Сравнение образовательного эффекта от обучения с применением различных методик

Кодировка заголовков, т.к. иначе не влезает по ширине в вёрстку.

A — ПЛИС-ориентированная разработка

B — БМК без применения ПЛИС и с реальным выпуском

C — БМК c применением ПЛИС и с реальным выпуском

D — ASIC без применения ПЛИС и без реального выпуска

E — ASIC c применением ПЛИС и без реального выпуска

F — ASIC c применением ПЛИС и с реальным выпуском

G — Текущая программа обучения в МИФИ, каф. 27

| Компонент маршрута | A | B | C | D | E | F | G |

|---|---|---|---|---|---|---|---|

| Постановка задачи | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| RTL-программирование | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| ASIC-ориентированное RTL-программирование | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Работа с современными САПР | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| Понимание ПЛИС-специфичного кода | ■ | □ | ■ | □ | ■ | ■ | ○ |

| Понимание работы синтезатора | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Понимание требований констрейнов | ○ | ■ | ■ | □ | □ | ■ | □ |

| Понимание важности размещения и трассировки | ○ | ■ | ■ | □ | □ | ■ | □ |

| Составление тестов | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Создание верификационного окружения | ■ | ■ | ■ | □ | ■ | ■ | □ |

| Мульти-корнер моделирование | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Моделирование с экстракцией | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Корпусировка | □ | ■ | ■ | □ | □ | ■ | □ |

| Аналоговая схемотехника | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Работа с измерительными установками | □ | ■ | ■ | □ | □ | ■ | ○ |

| Работа в лаборатории | ■ | ■ | ■ | □ | □ | ■ | ○ |

| Стоимость | 1 | 2 | 3 | 0 | 1 | 4 | 0 |

■ — присутствует в программе;

□ — отсутствует в программе;

○ — возможны варианты.

Данная таблица заполнена исключительно из моего видения того, как наличие того или иного этапа в неком сферическом дипломном проекте в вакууме влияет на исполнительность студентов. В реальности кто-то может и без преподавательской помощи осилить весь маршрут, а кто-то неспособен написать на Verilog’е мультиплексор. Строка «стоимость» отражает позиционирование в топе, но ни в коем случае не множители. Также «стоимость» не учитывает собственно стоимость САПР, по ряду различных причин.

Теперь становится видно, что при меньших дополнительных затратах маршрут, нацеленный на выпуск БМК, c применением ПЛИС и с реальным выпуском покрывает ровно тот же набор умений, что и необходим для выпуска ASIC. Остальные же маршруты хоть номинально и покрывают большой спектр умений, на практике добросовестно студентами не выполняются ввиду отсутствия мотивации на прикладывание большого количества усилий без какого либо видимого результата.

На сегодняшний день проектирование микросхем начального уровня стало достаточно простой задачей: все наслышаны о ПЛИС (программируемых логических интегральных схемах), о синтезаторах схемы из кода, о программах расстановки компонентов и последующей трассировки микросхемы. В то же время, многие начинающие разработчики с трудом представляют себе, что такое БМК, как с ним работать и какие преимущества это дает. К сожалению производителей БМК, такая ситуация приводит к следующим результатам:

«Анализ 2009 года показывает отток части потребителей из-за расширения области применения импортных ПЛИС на основании оформляемых разрешений.» © годовой отчет ОАО «Анстрем» за 2009 год.

На современном рынке микроэлектронике есть много производителей БМК: как отечественных, так и зарубежных. В частности, в Союзном государстве России и Белоруссии есть как минимум шесть производителей микросхем, которые предлагают для разработки свои БМК: ОАО Ангстрем, МВЦ НН, АО НИИМА «Прогресс», НПК «Технологический центр», ОАО НПО «Физика» и минский «Интеграл».

Обычно, для разработки микросхем применяют специализированные САПР известных фирм, таких как Cadence, Synopsis или Mentor Graphics, однако в случае с БМК все несколько сложнее. Официальной поддержки БМК, как отдельного типа микросхем, данное ПО не предоставляет, но возможно заставить его работать в нужном режиме с помощью различных ухищрений. В данной ситуации разработчикам БМК приходится разрабатывать свои уникальные маршруты проектирования, которые иногда используют наряду с самостоятельно разработанным ПО также и OpenSource ПО, например — Yosis.

- В случае ОАО Ангстрем, найти точную информацию и используемом САПР весьма затруднительно. Есть, однако, предпосылки считать, что их САПР «Невод» более не используется и осуществлен переход на использование продукции фирмы Cadence.

- МВЦ НН, ОАО НПО «Физика», АО НИИМА «Прогресс» и Интеграл, информации о используемом САПР не предоставляют, однако у Интеграла PDK под Cadence, так что можно сделать вывод, что остальная часть маршрута тоже там.

- НПК «Технологический центр» используют свой САПР «Ковчег», который реализует практически полный маршрут проектирования. Во всяком случае, это утверждается на их сайте.

Популярной причиной нежелания работать с БМК является неуверенность в том, а «влезет» ли разрабатываемая схема на данный БМК и на какой скорости всё это будет работать. Конечно, хорошо, когда есть серия БМК с единой библиотекой проектирования, и вы можете перескочить на более емкий или более быстрый кристалл, если потребуется, но это не всегда возможно. Вот, к примеру, про TSMC всё понятно: есть множество компаний, которые открыто заявляют о быстродействии своих схем, выполненных на том или ином тех. процессе. А что с нашими БМК? Где вообще взять список изделий, созданных на базе БМК, и посмотреть их быстродействие?

Несколько примеров:

- Цифро-аналоговый БМК. Около 300 вентилей + 8 силовых транзисторов. Реализована таймерная схема на 2 минуты с двумя ступенями защиты. Контроль нагрузки на токовых зеркалах, силовые транзисторы для управления нагрузкой. Пониженное энергопотребление, работа с кварцем 32.768кГц, диапазон питающих напряжений от 1.8В до 9В.

- Цифровой рад. стойкий БМК. 100 000 вентилей. Логика спец. назначения + NCO (numerically controlled oscillator). Аккумулятор фазы 40 разрядов, синус — 12 разрядов. Два регистра управления частотой синуса, параллельной и последовательное управление. Выход — параллельный.

- Цифро-аналоговый БМК. Около 400 вентилей + ЦАП 10 разрядов. Генератор синуса на 7 разрядов с токовым выходом.

- Цифровые БМК. От 1500 до 3000 вентилей. Различные терминалы мультиплексного канала ГОСТ 26765.52–87.

- Цифровой БМК. Около 500 вентилей. Восьмиканальный генератор для управления первичными обмотками трансформаторов.

- Цифровой БМК. Около 3000 вентилей. Мажорирующая схема для 8 разрядной шины.

К сожалению, специфика рынка приводит к тому, что подавляющее большинство разработок на БМК остаются неизвестны широкой публике. Публичные данные не дают чёткого представления о быстродействии, а заявленные в рекламных проспектах цифры выглядят неоднозначно. Вместе с тем, для задач знакомства с технологией много не требуется, а уже имея некий опыт работы за плечами гораздо проще дать приблизительную оценку сложности той или иной схемы.

Перейдем к самому интересному. У нас есть: БМК на ~3к вентилей (1 вентиль = 2 КМОП транзистора) с канальной архитектурой, разводка в одном слое металле и подслое поликремния; энтузиазм; одобрение руководства предприятия на самообучение работника.

Идея будущего кристалла родилась из безделья, а именно с прочтения одного форума, где, в частности, велась беседа о схемотехнически компактных решениях по вычислению кодов синуса. Мне эта тема показалась интересной, и я решил посмотреть, что же можно на этом направлении сделать.

Сейчас же посмотрим, что было сделано, что нет, какие ошибки и какие выводы были сделаны.

6.1 Проектирование

Поверхностные изыскания показали, что есть алгоритм расчета значений синуса, который из математических операций требует лишь суммирование, вычитание и сдвиг вправо. Оказалось, что это не просто алгоритм, а целое семейство, именующееся CORDIC (Coordinate Rotation Digital Computer). Интересующиеся подробностями работы алгоритма могут обратиться к списку литературы в конце статьи, а я лишь уточню, что с помощью данного алгоритма можно посчитать не только синус, но и косинус, арктангенс, умножать и делить аргументы, и некоторые гиперболические функции считать.

Изучив множество публикаций по этому алгоритму, и систематизировав эти знания у себя в голове, я прикинул, что можно попробовать на БМК емкостью около 3к вентилей реализовать этот алгоритм.

Итак, что мы имеем в конечном итоге по архитектуре схемы?

- Развернутый конвейеризованный CORDIC алгоритм для вычисления синуса.

- 4 дополнительных разряда во внутренних шинах данных для компенсации ошибок округления.

- 11 разрядный накопительный сумматор для значения фазы.

- Приращение фазы задается параллельной шиной.

- Формат данных на выходе: 7 разрядов + знак, параллельная шина.

Вроде всё хорошо, но что будет, если не компенсировать ошибки округления? А вот что (сравнение внутренней шины 11 бит и 8 бит):

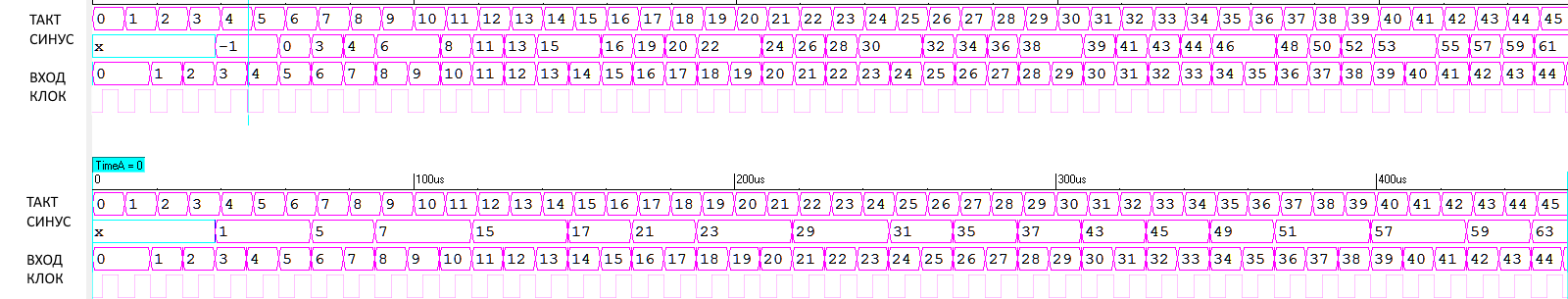

Рисунок 3. Сравнение выходных данных CORDIC алгоритма при применении внутренних шин размером 11 бит и 8 бит соответственно.

Если обратить внимание на вторые строчки данных, то видно, что ошибки округления могут эффективно понизить качество ваших вычислений.

Если мы в дальнейшем пристыкуем данную микросхему к ЦАП на 7 разрядов, то получим вполне годный генератор синуса (DDS, по нашему — прямой цифровой синтез). При этом у нас будет возможность для частотной модуляции синуса, но не будет возможности для фазовой модуляции.

Вообще, маршрут работы с маленькими БМК несколько отличается от общепринятого нынче маршрута проектирования. Если задуматься, отличия становятся очевидны: при таком маленьком вентильном объеме необходимо использовать каждый вентиль крайне эффективно, а основная парадигма современного проектирования заключается совсем не в этом. Она говорит о том, что изделие должно быть на каждом этапе архитектурно совместимо с современными системами автоматизированного тестирования, верификации, измерения. При этом вопрос вентильной эффективности остаётся за скобками, как необходимые накладные расходы. И вправду — в годы динамичного развития технологий производства думать о эффективности было лишним. Вот когда (и если) мы таки дойдем до физического предела и остановимся в повышении плотности транзисторов на кристалле, то тогда вопросы эффективности использования площади встанут перед нами в полный рост. Ну, а с маленькими БМК они и так стоят в полный рост, а потому вывод: в БМК маленьких емкостей можно и нужно использовать сложные дизайны с использованием различных хитрых схем генерации клоков, различных защелок, обратных связей и прочих вещей, за применение которых в современном маршруте старший инженер руки бы поотрывал.

Основная проблема использования таких вещей в том, что для их использования инженер должен четко отдавать себе отчет в том, что он делает и зачем. Однако, если понимание есть, то выигрыш может быть фантастический. Если же понимания нету… что ж, выстрелить в ногу можно миллионом различных эффектных способов.

Как же выглядел в моём случае маршрут проектирования:

- Составление схемы вручную в виде схемы из библиотечных элементов

- Оценка получившегося объема схемы

- Переработка схемы до тех пор, пока объем схемы не будет превышать 80% от емкости БМК

- Сюда также входит работа по созданию новых библиотечных элементов, их тестированию и интеграции в маршрут проектирования

- Составление тестов для схемы

- Ручная трассировка схемы

Бывалые проектировщики здесь сразу могут возразить, что упущено несколько важных этапов, но я реально ничего не забыл упомянуть.

Проектирование вручную очень хорошо показывает, насколько важна качественная библиотека компонентов. Первые варианты схемы не укладывались в кристалл просто по объему логики, а ведь в случае канального БМК — такого, где разводка идет по каналам, проложенным между «строками» транзисторов — примерно еще 30% от объема схемы занимают межсоединения. Поэтому пришлось несколько расширить библиотеку, основываясь на той топологии, которая получалась в данном конкретном проекте. Такое подход позволил сэкономить значительное количество вентилей и даже более менее свободно проложить все трассы.

Итоговое заполнение кристалла — 72%, еще треть кристалла ушла на разводку. Дальше файлы были переданы на завод, а я вернулся к своим текущим рабочим проектам.

При «ручном» способе проектирования необходимо помнить следующие моменты:

- Нельзя бездумно использовать библиотечные элементы, опираясь на их функцию. Необходимо изучить из чего составлен этот элемент на транзисторном уровне, является ли он цифровым или аналоговым. Какие у него нагрузочные способности по входам и выходам, является ли он чисто CMOS логикой, или TG, или чем-то еще.

- Необходимо учитывать и согласовывать мощности элементов и их нагрузку.

- Если у вас есть синхронный триггер, то тактировать его нужно сигналами равной мощности.

- Если вы используете какой-то сигнал без промежуточного усиления, а он нагружен на много потребителей, то сигнал может сильно завалиться. Это может быть незначительно в нормальных условиях, но критично при проверке на ВВФ (внешние воздействующие факторы).

Никакая система моделирования не заменит вам собственные мозги. Вообще нельзя запускать моделирование, если вы сами не понимаете, как работает схема.

6.2 Измерения

Крайне важный этап в работе с кристаллом — это его измерения. Можно выделить три типа измерений: технологические, функциональные, электрические. Первые проверяют, что завод не накосячил и кристалл технологически корректно изготовлен. Вторые же проверяют, что теория (т.е. моделирование) сходится с практикой (реальным кристаллом). Третьи отвечают за такие параметры, как: токи потребления, токи утечки, входные и выходные токи и пр. Здесь крайне важно понимать, что измерения на реальном зондовом аппарате это вообще не то же самое, что моделирование. И это даже не то же самое, что и работа корпусированной микросхемы на плате в составе какого-то устройства. Зачастую, это гораздо хуже в плане условий работы кристалла. Ведь зондовый аппарат — это одно, а измерительная система — другое. Между ним есть шлейф, межсоединения… А это все ни что иное, как огромное количество паразитных резисторов, емкостей и индуктивностей. Поэтому тесты для измерительной установки создаются отдельно с учетом физики протекающих процессов.

А еще измерительные установки бывают разные, и у каждой из них свои особенности и нюансы. Например, у установки Fairchild родом из 80-х годов прошлого века интерфейс не USB, а ленточная кассета. У отечественной установки FORMULA после первой зафиксированной ошибки на временной диаграмме измерения появляются рандомно еще некие «фантомы», которые легко исчезают после фикса первой ошибки. Измериловка от HP живет на каком-то древнем Unix’е и общается с внешним миром исключительно по сети. У измериловки от National Instruments положение строба задается не так, как у всех, а своим специальным образом, что накладывает свои ограничения на формирование тестовых последовательностей (векторов). Есть еще измерительные установки от Agilent, со своими нюансами. В общем идея понятна, да?) Легко и просто не будет.

А студенту, по-хорошему, надо бы поработать с каждой из измерительных установок, чтобы иметь широкое понимание об этом процессе. Потому что жизнь бывает сложнее наших ожиданий, и то, что изначально кристалл измерялся на, допустим, Fairchild, не значит, что следующие измерения не придется провести на NI. Таким образом должен быть некий исходный набор тестов, который применим к каждой из находящихся в эксплуатации измерительных систем посредством разного рода программных конверторов. Если при составлении тестов что-то не учесть, то может оказаться невозможным использование какой либо измерительной системы, либо будет нарушена согласованность данных тестовых векторов друг с другом.

Вообще, для начинающих у меня есть небольшой список правил и напоминаний, которых надо придерживаться при проведении измерений:

- Если нету на то веских причин, то следует измерительную систему считать заведомо исправной.

- Зондовый автомат обязательно должен корректно контактировать с пластиной. Если контактирования нету, то не имеет смысла проводить дальнейшую работу.

- «Быстрый» тест может работать некорректно при измерении с оснасткой с длинными проводами.

- Тест может быть сам по себе нелогично составлен, без учета физики проходящих процессов, как несинхронность сигнала общего сброса, например.

- Пластины могут быть разными по качеству.

- Кристаллы на пластинах могут содержать различные дефекты:

- Топологические

- Схемотехнические

- Технологические

- Все входы/выходы, отличные от чисто цифровых, должны иметь свой расчетный ток потребления. Ток потребления микросхемы должен быть рассчитан с учетом всех входов/выходов.

- Следует помнить о значениях напряжений и токов, установленных для различных драйверов измерительной системы.

- Схемотехническую ошибку при проведении измерений можно считать найденной, если она — регулярная. То есть повторяется независимо от пластины и кристалла на пластине.

- Если ошибка не критичная, то её необходимо «учесть» в исходных файлах и составить тесты заново так, чтобы устранить её.

- Если вы вносите изменения в исходные файлы после выпуска нулевой коррекции кристалла, то следует обязательно вести историю изменений.

Список можно расширять и дальше, но он даёт хорошее представление о том, какие нюансы могут всплыть при первом знакомстве с процессом измерения кристалла.

Но теперь перейдем к практике. Спустя всего лишь 4 (!) недели были получены пластины с готовыми кристаллами. Измерения пластин показали, что схема работает, но не целиком. Помните про выстрел в ногу, да?) Я успешно выстрелил себе в ногу проигнорировав на этапе проектирования неуказанный выше пункт «Экстракция паразитных параметров из топологии и повторное моделирование».

Рисунок 4. Мем.

Но делать то нечего, надо изучать что и почему не работает. Заранее приготовленный макет оказывается непригоден, а потому берем универсальную макетку, паяльник и вперед. Спустя 80 проводков, одну ардуину, пару корпусов универсальной логики и несколько литров кофе был получен рабочий макет, который не просто лампочкой помигал, а сыграл мне 8-битную ламбаду.

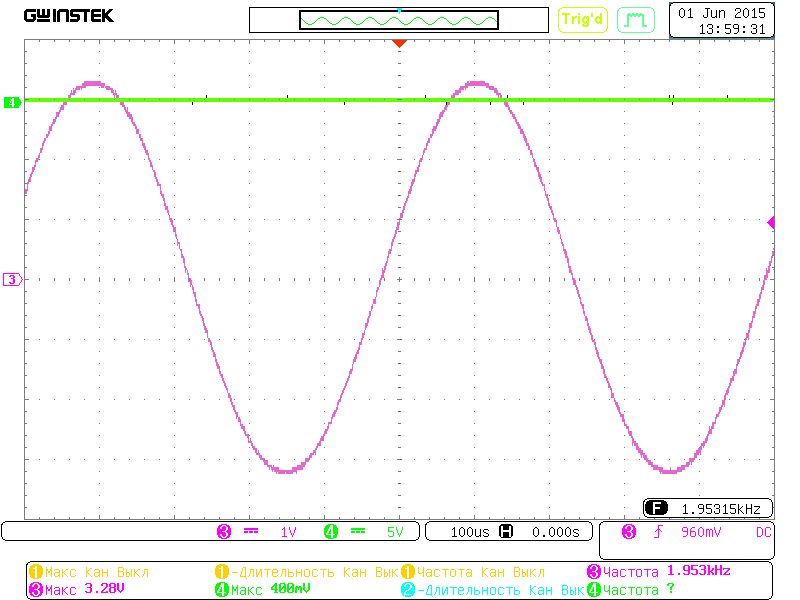

Ну, а если более серьезно, то далее парочка осциллограмм. При разных тактовых частотах и разных заданных приращениях фазы за такт можно получить следующие синусоиды:

Рисунок 5. Большое приращение фазы за такт

Рисунок 6. Маленькое приращение фазы за такт

То есть, чем меньше приращение фазы за такт, тем более гладкая получается синусоида.

Тем не менее, отрицательный результат — тоже результат. Выводы были сделаны, опыт получен. Энтузиазм подогрет 8-битной ламбадой до небывалых величин. Делаем вторую коррекцию.

6.3 Вторая коррекция микросхемы

Что же надо сделать дальше?

- Признать текущий вариант микросхемы несостоятельным;

- Более подробно исследовать варианты построения NCO (numerically controlles oscillator);

- Найти, исследовать, разработать вариант NCO на базе технологии сжатия ROM (cROM);

- Разработать сжатую схему умножения с достаточной для конкретной задачи точностью;

- Разработать для библотеки компонентов:

- Несколько вариантов ячейки статической памяти

- Несколько вариантов усилителей считывания из памяти

- Несколько вариантов адресации ячеек в памяти

- Выбрать из всего многообразия вариантов тот один, который должен дать наилучший результат;

- Оптимизировать применямые библиотечные элементы под конкретный проект;

- Спроектировать БМК

Рисунок 7. Промежуточный вариант топологии кристалла, загруженный в HRT.

Итоговые параметры выпущенной микросхемы:

- Заполнение БМК — 83%.

- Накопитель фазы 14 разрядов

- Задаваемое приращение фазы 11 разрядов

- Комплементарные выходы фазы (sin & cos, 12 разрядов) на параллельные шины

- Входная частота 16МГц

К сожалению, осциллограммки данной версии у меня не сохранилось, да и на что там особо смотреть? Данная версия хорошо работает во всем заданном диапазоне температур и напряжений, а результат по частоте оказался даже лучше ожидаемого. Трассировка данной версии микросхемы была достаточно сложной, но желание уместить-таки схему победило все сложности.

Разработка данной микросхемы для меня всегда была как некий второстепенный проект, но вместе с тем весьма увлекательный. Я получил уйму знаний о множестве различных интересных областей проектирования, в которые изначально не очень и хотелось погружаться. Если вы студент, и у вас есть возможность в качестве дипломного проекта выпустить свою собственную прошивку для БМК — хватайтесь за эту возможность обеими руками. Опыт такого рода бесценнен.

Это очень правильные вопросы.

Начнем со второго.

30 000 рублей стоит выпуск одной пластины диаметром 100 мм по технологии 2 мкм. За эти деньги мы получаем огромное количество опыта, который осядет «на кончиках пальцев» у студентов. Даже если в будущем этот студент пойдет программировать ПЛИС, у него никогда не возникнет вопрос про то, что такое Setup&Hold, никогда он не забудет, что код на Verilog’е это не просто программа, а алгоритм, выполняющийся на реальном устройстве, а внешние сигналы — не просто цифры логического состояния, а сложная цепочка, содержащая множество паразитных элементов. В зависимости от выбранного БМК можно опробовать и полноценный современный цифровой маршрут, и гибридный — миграцию с ПЛИС на БМК, и смешанное моделирование, верификацию любых уровней сложностей, аналоговые схемы… простор ограничен лишь фантазией студентов. А главное — теоретическое обучение будет подкреплено своим кристаллом, стоящим на полочке и мигающим лампочкой.

Примечание. Замечания по поводу ошибок в статье прошу направлять в личку.

ВУЗ Высшее учебное заведение

МИФИ Московский инженерно-физический институт

МИЭТ Московский институт электронной техники

MIT Massachusetts Institute of Technology

UZH Universität Zürich

БМК Базовый матричный кристалл

ASIC Application specific integrated circuit

ПЛИС Программируемая логическая интегральная схема

САПР Система автоматизированного проектирования

КМОП Комплементарная металл-оксид-полупроводник [технология]

CORDIC Coordinate Rotation Digital Computer

ЦАП Цифро-аналоговый преобразователь

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

- Сайты производителей БМК

- Гугл

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- Алгоритмы CORDIC. Современное состояние и перспективы, А.В. Захаров, В.М. Хачумов

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf