Революция в радиотехнике? RF-ARM-FPGA SoC

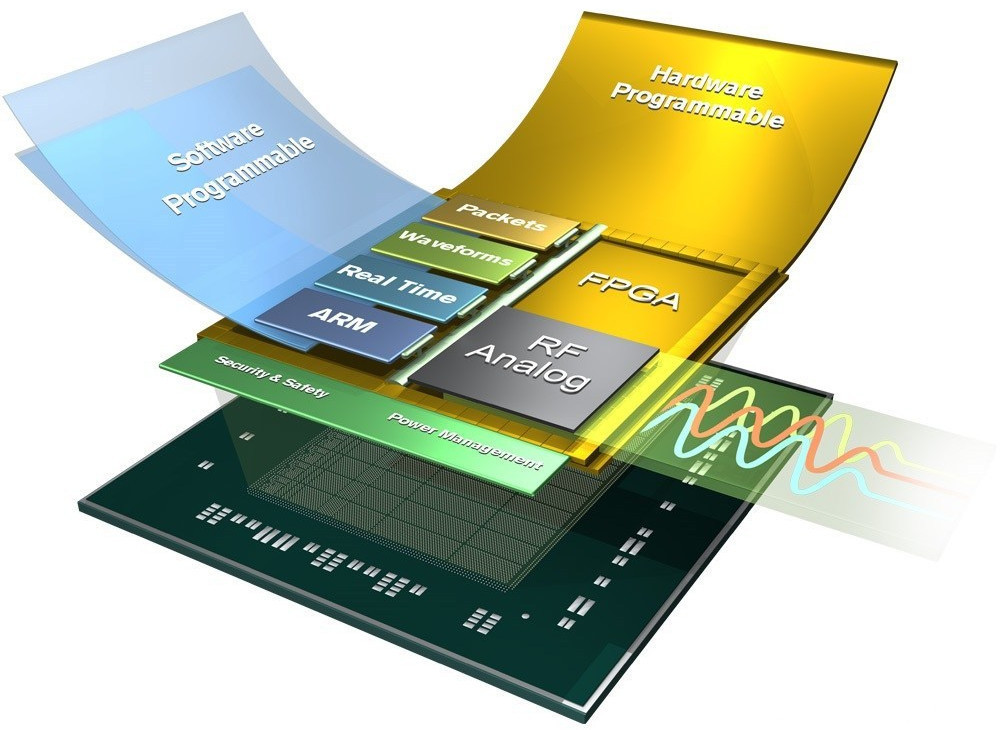

Компания Xilinx тихо и без лишней помпы анонсировала продукт, который может полностью изменить облик и процесс разработки современных радиоприемников и передатчиков. Это маленькая микросхема, которая объединяет 90% вопросов обработки и формирования радиосигналов:

- программируемая логика (FPGA),

- процессоры для обработки сигналов и пользовательских приложений (два ARM«а),

- до восьми 12-разрядных АЦП с верхней частотой до 4 ГГц (!),

- до восьми 14-разрядных ЦАП с верхней частотой до 6.4 ГГц (!).

Кажется мы входим в эпоху, когда архитектура трансивера становится такой же универсальной, как архитектура современного ПК. Make SW, not HW!

Эра до Zynq«а

Немного истории. Я представитель небольшой команды, основная деятельность которой в течение последних 10–15 лет — это R&D в области спутниковой навигации.

Чего только мы ни делали за это время! Разрабатывали новые сигналы для ГЛОНАСС, обрабатывали все возможные сигналы, имитировали сигналы навигационных систем, делали системы для обнаружения помехопостановщиков, мастерили микросхемы для антенных решеток, делали приемники размером с телевизор для квантово-оптических станций. В общем, по нашим приключениям смело можно писать Камасутру сигнальной обработки (что мы и сделали)!

Понятно, что при таком зоопарке задач мы никак не можем обходиться стандартными приемниками. Мы любим и знаем модули Геос и NV-08C, даже поучаствовали в этих проектах, но для своих проектов мы всегда использовали собственные разработки.

Единственный способ сделать мелкосерийный приемник — основываться на ПЛИС (FPGA). Тут стоит пояснить, что процесс обработки современных сигналов напоминает работу компьютерной графики. Операции относительно простые, но их нужно делать очень много параллельно. В этом смысле FPGA (или кусок кремния в крупной серии) для приемника как GPU для современного компьютера.

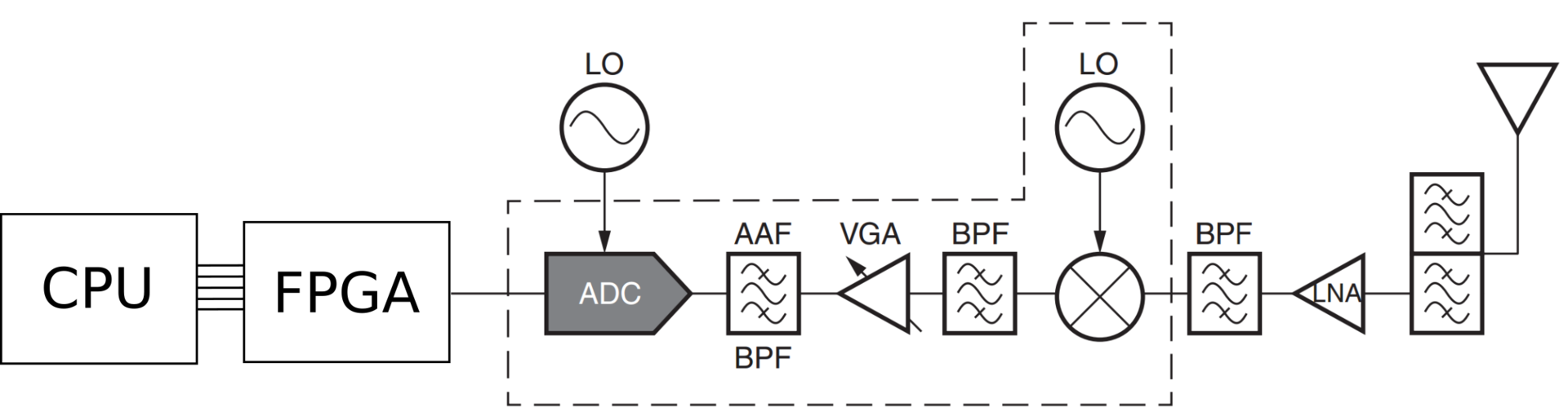

Как же выглядела структурная схема приемника лет так десять назад?

Что плохого в этой схеме? Процессор и программируемая логика разнесены в разные микросхемы. И это порождает кучу проблем.

Специфика обработки сигналов требует постоянного обмена данными между процессором и ПЛИС в режиме строгого реального времени! Потоки для навигационного приемника достигают нескольких гигабит.

Каждая микросхема требует своей обвязки, охлаждения, многослойной платы для соединения и банально занимает место на печатной плате.

И в конце концов, это просто сложно. А сложность в построении систем почти синоним провала.

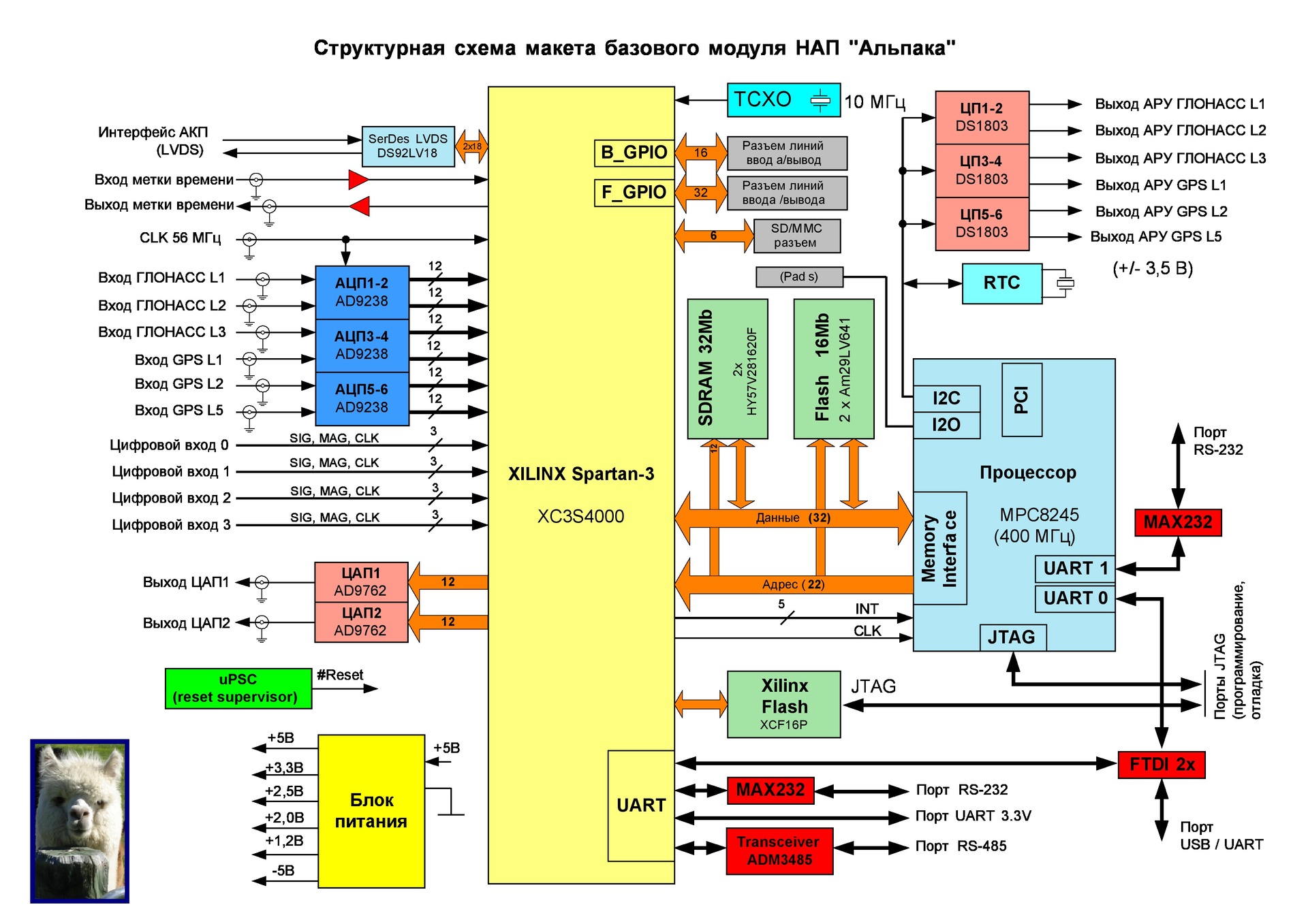

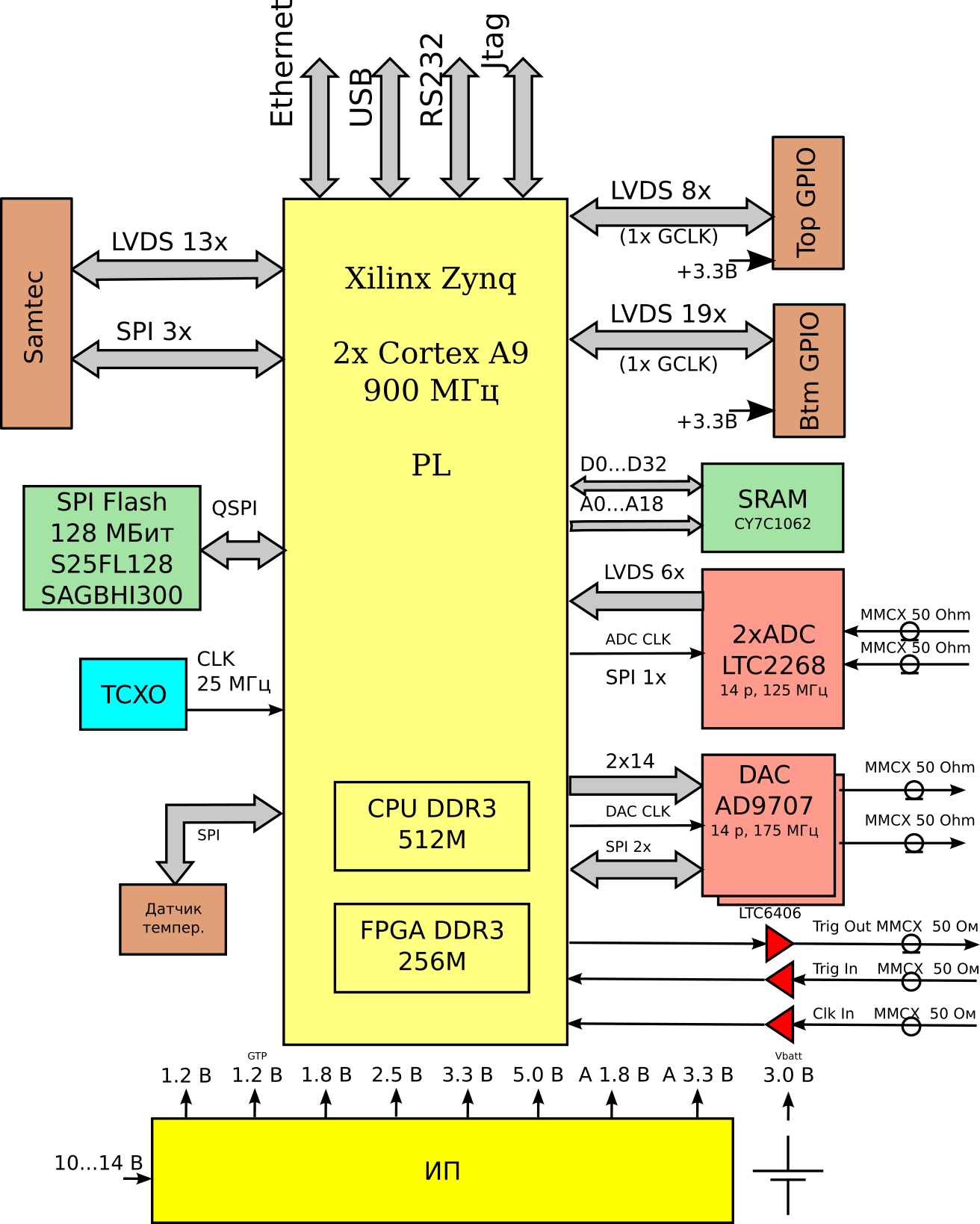

Например, структурная схема приемника, который мы делали в 2007 году:

В качестве FPGA использовался Xilinx Spartan 3, в качестве процессора — здоровенный PowerPC в виде MPC8245. Ушла куча времени на перенос toolchain«ов, поиск драйверов, организации обмена между ПЛИС и процессором и т.д.

Но внезапно мир изменился…

Появление SoC, объединяющих программируемую логику и процессорную систему

Описанная выше боль характерна для мелкосерийного производства и прототипирования. Для связки отдельный FPGA + отдельный CPU характерна высокая себестоимость, дикое потребление и габариты. А что ещё хуже, программная часть продукта была непереносима. Для каждой новой комбинации приходилось переписывать большую часть софта.

Как только продукт мог отбить производство ASIC«а, то производитель разрабатывал собственную микросхему. В такой микросхеме объединялась вся цифровая обработка: АЦП на промежуточную частоту, параллельная логика цифровой обработки, процессор, интерфейсы. По такой схеме построены все современные навигационные чипы.

В начале 2010-х Xilinx и Altera анонсировали продукты, которые решили половину наших проблем. Компания Xilinx начала выпускать микросхемы серии Zynq, объединяющие в себе программируемую логику (FPGA) и процессорную систему (двухядерный ARM с полным набором периферии).

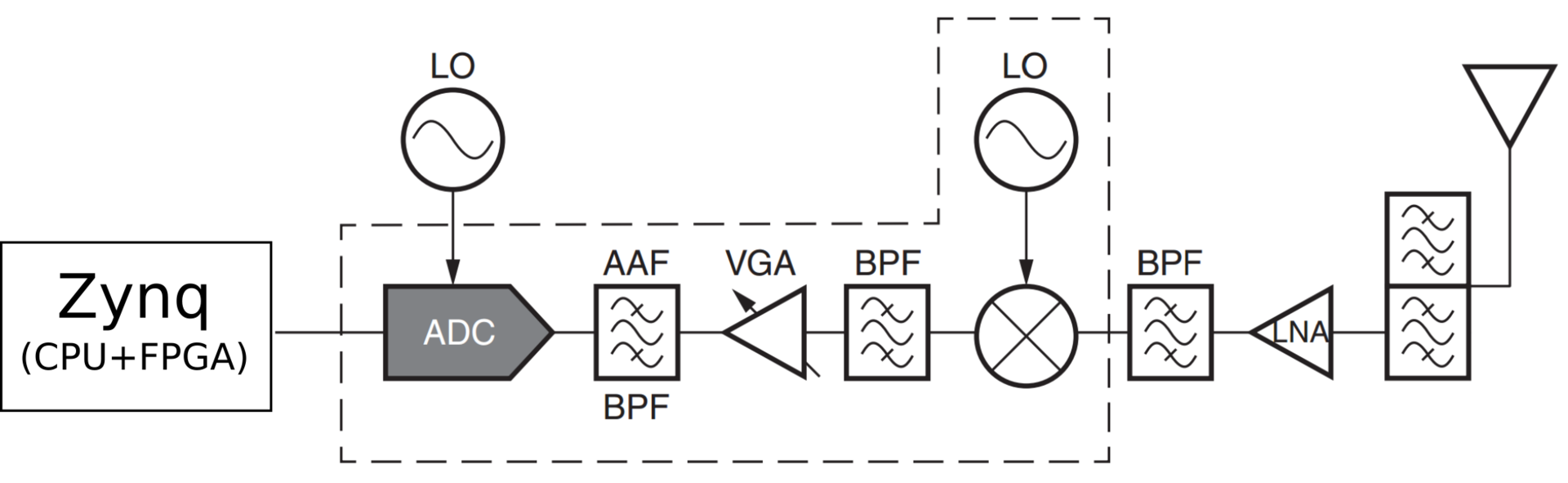

Система на кристалле Zynq была огромным шагом вперед. Существенно упростился код, поднялась скорость обмена между процессорной системой и программируемой логикой, упростилась печатная плата. Например, структурная схема одного нашего проекта в 2013 году, почувствуйте разницу:

И самое главное, неожиданно родилось новое качество: теперь наш софт запускался на любой плате с Zynq«ом.

В цикле разработки радиотехнического устройства, написание алгоритмов и софта, сопутствующие исследования, отработка занимают 80% времени. Если Java — это cross-platform, то Zynq — это cross-board. Теперь мы можем переложить разработку платы на заказчика, а сфокусироваться на главном — софте.

Кроме того, Xilinx взял на себя вопросы toolchain«ов, драйверов и прочие далекие от радиотехники проблемы.

Через пять лет после запуска Zynq«ов появилось интересное явление — коммерческие продукты на базе программируемой логики. Примером может служить Piksi Multi или Tersus Precise. Да, эти приемники всё ещё потребляют больше аналогичных, построенных на ASIC. Но цена стала сравнима! Маленький Zynq с небольшим количеством программируемой логики сейчас можно купить за $50! А это увеличивает число возможных приложения на порядки!

День грядущий…

Если учесть сказанное выше, то становится логично, что следующий шаг — добавить на кристалл АЦП и ЦАПы. Но компания Xilinx решила сделать сразу два шага вперед.

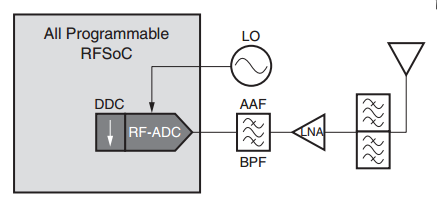

Тут чуть подробнее. Современные приемники или передатчики — это два мира. Цифровой и аналоговый. Например, рассмотрим приемник.

Аналоговый мир:

- антенна, преобразующая электромагнитное поле в электрический сигнал;

- фронтенд, функция которого — отфильтровать, усилить и понизить несущую частоту сигнала, чтобы его потянула цифровая обработка.

Стык между адом и раем аналоговым и цифровым миром — АЦП.

Далее идет цифровой мир, реализуемый разновидностью компьютера.

Xilinx замахнулся на аналоговый мир!

АЦП с верхней частотой в 4 ГГц позволит переходить на цифровую обработку сразу на несущей! ЦАПы с верхней частотой до 6 ГГц — выкинуть все звенья до усилителя мощности.

И таких АЦП и ЦАПов — по 8 штук! Это закрывает вопросы с многоантенными системами, которые с каждым годом становятся всё актуальнее: MIMO, CRPA, Beamforming, определение ориентации и т.д.

Аналого-цифровые преобразователи реализованы на одной микросхеме, что обещает высокую идентичность их характеристик. При этом они обладают высоким динамическим диапазоном — порядка 65 дБ SFDR.

Таким образом, аналоговая часть сводится до антенны, предварительных фильтров, предусилителя, усилителя мощности. И одного этапа гетеродинирования, если ваши рабочие частоты выше указанных. Большим вопросом остается антиалайзинговый фильтр на несущей — его изготовление то ещё удовольствие.

По заявлениям Xilinx, использование RFSoC позволяет существенно улучшить энергопотребление. В варианте с 8 АЦП и 8 ЦАП указывается энергопотребление в 27 Вт.

Как и в серии Zynq UltraScale, процессорная система представлена двумя процессорами — для радистов (двухядерный Cortex-R5) и для пользовательских приложений (четырехядерный Cortex-A53).

Резюме

Анонс Xilinx«а отражает общую тенденцию в радиотехнике — курс на унификацию и решения всё в одном. Лично мне это напоминает развитие компьютеров в XX веке. Какие последствия для индустрии принесло появления однотипных ПК, что стало с профессией программиста и как изменился мир — напоминать не требуется.

Главный вопрос теперь —, а будут ли продавать нам это чудо? Остается надеяться на гражданскую версию за адекватные деньги.

Ссылки

https://www.xilinx.com/rfsoc

www.xilinx.com/support/documentation/product-briefs/rfsoc-ieee-paper.pdf

www.eejournal.com/archives/articles/20170221-xilinx-rfsoc

Комментарии (7)

12 марта 2017 в 18:17

0↑

↓

Спасибо! Я пропустил такую новость.Но жрать такая штука должна очень много.

Для мобильных штук не пойдет, я думаю.12 марта 2017 в 18:23

+1↑

↓

Да, этот изъян пока решается только выпуском ASIC’а. Но в мобильных приложениях прочно засели монстры типа Qualcomm, там тяжело конкурировать.Другое дело возимые девайсы…

12 марта 2017 в 18:26

0↑

↓

А АЦП до 4 ГГц — это запредельные мегасэмплы в секунду (как это всё обработать-то?) или большая полоса пропускания + АЦП, «выхватывающий» полосу из сигнала (субдискретизация сигнала или полосовой сигма-дельта АЦП)?

12 марта 2017 в 18:34

0↑

↓

Судя по таблицам, они предполагают порядка 100 Мегасемплов за счет digital down conversion. Тут возникает вопрос, как быть с фильтрами? Обеспечить нормальную фильтрацию на несущей тяжело. Пока не знаю, есть ли у них промежуточная фильтрация.12 марта 2017 в 18:52

0↑

↓

Ну по первой ссылке пишут GSPS, хотя слабо верится…

12 марта 2017 в 19:01

+1↑

↓

У вас на картинке с цинком DDR3 как-то неоднозначно нарисована, как будто она не на периферии висит, как и флешка. Или это контроллеры типа?12 марта 2017 в 19:07

0↑

↓

В том проекте мы использовали не сам Zynq, а процессорный модуль с ним. На нем уже висел DDR, поэтому на схеме получилось такое обозначение.