Исходники промышленных процессоров станут доступными для университетов

Господа! На днях Imagination Technologies (компания, которая спроектировала графический процессор PowerVR GPU внутри Apple iPhone) и Xilinx (компания №1 в ПЛИС-ах / FPGA) начали понемногу предавать гласности несколько иконоборческую инициативу по бесплатной раздаче университетам исходников современного индустриального процессорного ядра MIPS microAptiv UP, которое используется например в микроконтроллере Microchip PIC32MZ. Студенты смогут менять команды этого процессора, добавлять к нему свои периферийные устройства и реализовывать полученный дизайн на ПЛИС-ах.Вот линк на сообщение о семинаре 13–14 мая возле Лос-Анжелеса, на котором Imagination и Xilinx будет показывать новый продукт под названием MIPSfpga представителям academia — imgtec.com/mipsfpga

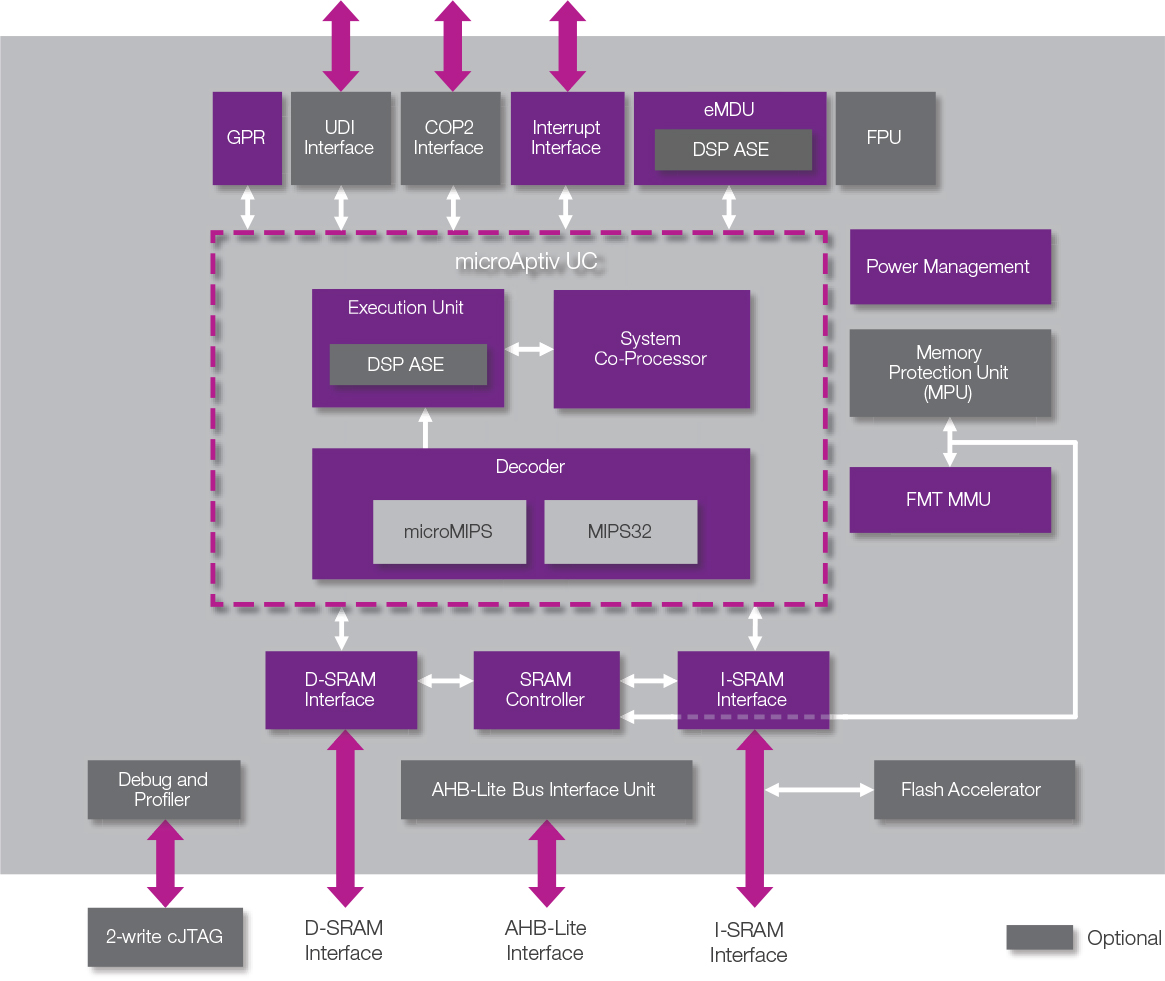

Фактически MIPSfpga — это бесплатная лицензия на базовую конфигурацию экономичного процессорного ядра MIPS microAptiv UP, которое предоставляется в исходных текстах на языке описания аппаратуры Verilog. Это то же самое ядро, которое продается коммерческим клиентам за сотни тысяч долларов. MIPS microAptiv UP — это простой дизайн с пятью стадиями последовательного конвейера (как в учебниках компьютерной архитектуры), но в нем есть кэши и TLB MMU. TLB MMU позволяет даже использовать на нем Линукс.

Описание ядра www.imgtec.com/mips/aptiv/microaptiv.asp

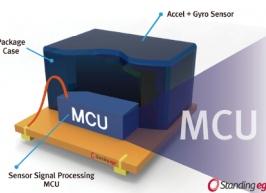

Наиболее широко известным примером использования ядра MIPS microAptiv UP является 32-битный микроконтроллер Microchip PIC32MZ, который начали выпускать в прошлом году. А из самых последних примеров использования: 10 апреля этого года Electronic Engineering Times опубликовала статью про южнокорейский стартап Standing Egg, который лицензировал ядро MIPS M5100 (фактически MIPS microAptiv без кэшей и MMU, но с добавленным расширением для виртуализации) для создания платформы для MEMS сенсоров, с приложениями для Internet of Things:

Наиболее широко известным примером использования ядра MIPS microAptiv UP является 32-битный микроконтроллер Microchip PIC32MZ, который начали выпускать в прошлом году. А из самых последних примеров использования: 10 апреля этого года Electronic Engineering Times опубликовала статью про южнокорейский стартап Standing Egg, который лицензировал ядро MIPS M5100 (фактически MIPS microAptiv без кэшей и MMU, но с добавленным расширением для виртуализации) для создания платформы для MEMS сенсоров, с приложениями для Internet of Things:

www.eetimes.com/document.asp? doc_id=1326327

Разработчики микросхем с MIPS microAptiv UP используют стандартную за последние 20 лет методологию электронного дизайна под названием Register Transfer Level (RTL, уровень регистровых передач). Согласно этой методологии, дизайн пишется на языке Verilog, после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических элементов, другая программа (static timing analysis) сообщает разработчику, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. — получается файл под названием GDSII, который отправляют на фабрику, где и изготавливаются микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC. При этом, ничего не мешает производить микросхемы с ядром MIPS microAptiv UP на российских фабриках Микрон и Ангстрем.

Альтернативой производству микросхемы на фабрике является реализация дизайна на программируемых пользователем матрицах логических элементов (Field Programmable Gate Array — FPGA), что и используется для образовательных целей в новом продукте MIPSfpga.

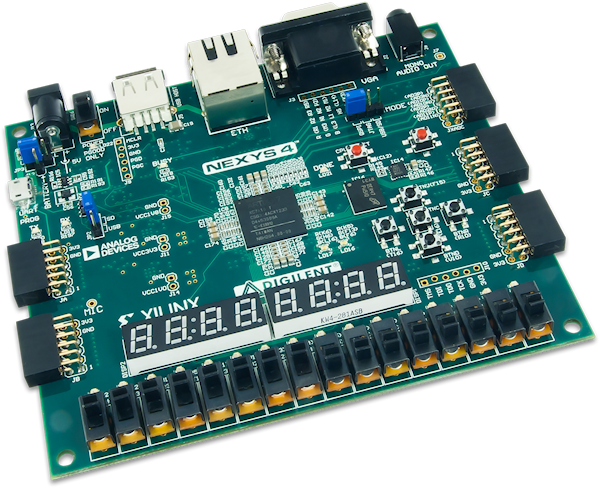

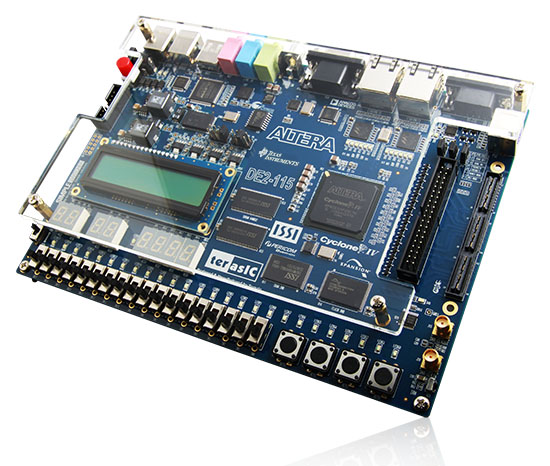

Хотя пакет MIPSfpga и заточен на синтез для FPGA (например в MIPSfpga есть реализация памяти внутри кэшей, используя макро для Xilinx Artix-7 и Altera Cyclone IV), но в основном это те же исходники, которые используются и для синтеза в ASIC. Иными словами, студенты и аспиранты могут экспериментировать с ядром на недорогих FPGA-платах, придумать какое-нибудь интересное решение (скажем многоядерную SoC из малых некогерентных ядер, или комбинацию из ядра MIPS microAptiv UP со специализированным студенческим DSP процессором), не вкладывая при этом денег инвесторов, после чего, когда идея доказана, найти инвесторов, приобрести коммерческую лицензию и сделать микросхему на фабрике — ASIC.

Обращаю внимание, что в случае с MIPSfpga речь идет не об ограниченном образовательном подмножестве MIPS (таких подножеств довольно много из других источников) и не об open-source ядре типа OpenRISC или Leon4, а о коммерчески успешном современном индустриальном ядре, которое за деньги лицензировало несколько десятков компаний.

У конкурирующей компании ARM тоже есть soft core для образовательного экспериментирования на FPGA, но их ядро не в открытом исходном тексте (т.е. студенты не могут подключать провода к внутренним регистрам и модифицировать верилог), у ARM-овского ядра ARM Cortex M0 в конкурирующем продукте нет кэшей, интерфейса к отладчику и TLB MMU. Все это у MIPSfpga есть.

Дополнительные детали:

Сейчас MIPSfpga работает на двух платах Digilent Nexys-4 с Xilinx Artix-7 и Altera DE2–115 с Cyclone IV E. У первой академическая цена $180 / коммерческая $320, у второй академическая $300 / коммерческая $600. Перенести его на другие платы довольно легко (при условии, что вместится) — нужно заменить некоторые макро для памяти и подсоединить top-module к board-specific внешнему verilog wrapper-у. В частности, можно попробовать перенести его на дешевую плату Digilent Basys-3 с Xilinx Artix-7 (академическая $80 / коммерческая $150), а также на платы, которые спроектированы или производятся в России.

В качестве toolchain предлагается Codescape MIPS SDK, который содержит отладчик и GCC toolchain. Связь между отладчиком и платой Nexys-4 делается с помощью EJTAG, BusBlaster probe и OpenOCD. На Altera DE2 115 применяется отладочный интерфейс который стоит прямо на плате, т.е. BusBlaster не нужен. Также прилагается Boot code на ассемблере, который инициализирует кэши и MMU и т.д.

Теперь какое это может иметь отношение к вам:

1. Первый этап апробации MIPSfpga на трех университетах в US и UK успешно завершен. Теперь продукт будет проходить бета-тестирование в бОльшем количестве университетов в США, Европе и Азии. Если вы работаете в университете, и в нем есть достаточная экспертиза в Verilog или VHDL чтобы работать с пакетом, то вы можете принять участие как early adopter и получить преимущество перед другими вузами в его использовании.

2. 13–14 мая в Лос-Анжелесе будет проходить семинар, организованный Imagination Technologies вместе с Xilinx, на котором профессора Harvey Mudd College и application engineers из Imagination будут тренировать профессоров различных вузов использовать MIPSfpga. Если вы или кто-либо из ваших знакомых преподавателей уиверситетов хочет в нем участвовать и может приехать в это время в Лос-Анжелес, просьба связаться либо с менеджером образовательных программ Робертом Оуэном (его координаты в imgtec.com/mipsfpga), либо со мной (yuri.panchul@imgtec.com).

3. К моменту семинара в Лос-Анжелесе MIPSfpga будет официально объявлен, а после завершения (1) станет общедоступным. Поэтому если вы не имеете возможности принять участие как early adopter, вы тем не менее сможете начать работать с продуктом летом.

Возможность использования индустриальных процессорных ядер на верилоге в образовательных целях и без покупки коммерческой лицензии, позволит большому числу молодых разработчиков в academia заняться прототипированием инноваторских решений в области систем на кристалле и расширений микроархитектуры, с непосредственным путем к коммерциализации — созданию своих микросхем для интернета вещей и других приложений.

Юрий ПанчулSenior Hardware Design Engineer, MIPS processorsImagination Technologies

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.