Cisco раскрыли особенности работы 400-гигабитного NPU

На выставке Hot Chips, прошедшей в августе этого года, ведущий инженер компании Cisco Джейме Маркевич (Jamie Markevitch) рассказал об особенностях работы сетевого процессора c производительностью 400 Гб/с, который в настоящее время поставляется клиентам.

/ Flickr / Timothy Lorens / CC

Чип выполнен по 22-нанометровому техпроцессу и имеет 672 ядра, каждое из которых обрабатывает до четырех потоков. Сетевой процессор (NPU) содержит 9,2 миллиарда транзисторов и 353 Мб памяти SRAM. SRAM играет роль кеша L0, в котором хранятся инструкции и данные для каждого потока. Также имеется кеш L1 для кластера из 16 ядер.

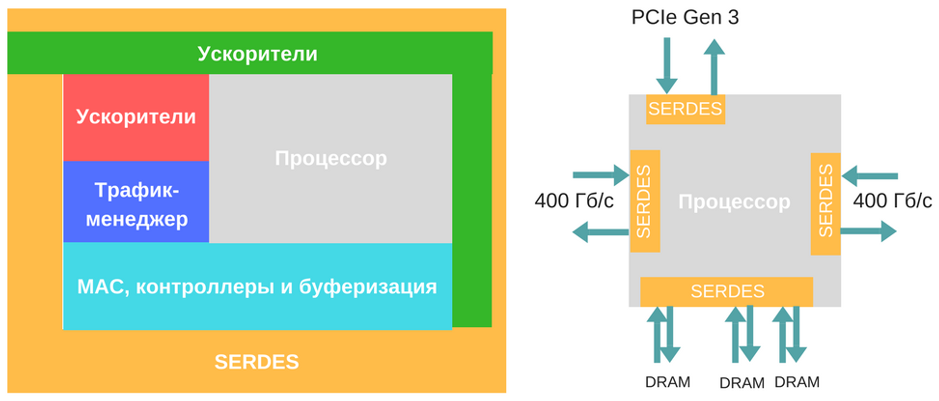

NPU обладает 42 кластерами ядер, которые соединены с кешем инструкций L2 за счет командного кеша L2. Он также объединяет кеши разных уровней, хранилище пакетов данных, ускорители, встроенную и динамическую память в единую «сеть». Эта сеть работает на частоте 1 ГГц и имеет пропускную способность более 9 Тб/с.

Блок-диаграмма чипа

Cisco не рассказали о наборе инструкций, который используется в NPU. Однако эксперты сделали предположение, что это кастомный набор, разработанный специально для работы с сетью, а не ARM, MIPS, Power или X86.

Потоки ядер NPU обеспечивают обработку пакета данных на протяжении всей его «жизни» в чипе. Это исключает простаивание или «жонглирование» пакетами между ядрами. Поэтому одновременно могут обрабатываться 2688 пакетов. Пакеты хранятся off-chip в DRAM, но обрабатываются в реальном времени в SRAM. Причём ускорители могут обращаться к DRAM-копии независимо от ядер, которые работают с SRAM-оригиналом.

Так как разные пакеты требуют разных характеристик, все ядра различаются по производительности, чтобы обеспечить максимальную эффективность. При этом Cisco NPU поддерживает привычные методы программирования — C или ассемблер.

Сетевой процессор обрабатывает пакеты на скорости 800 Гб/c, или 400 Гбит/с в полнодуплексном режиме. В свою очередь, пропускная способность интерфейса SERDES составляет 6,5 Тб/с. Большая часть соединений используется для подключения DRAM и TCAM — последняя хранит списки доступа (ACL). Она также используется для буферизации пакетов, поэтому ее иногда не хватает — тогда часть данных уходит на хранение в DRAM.

Большая часть логики NPU работает на частоте 760 МГц или 1 ГГц. Интерфейсы MAC поддерживают работу портов на скорости от 10 до 100 Гб/с.

Сетевой процессор оснащается интегрированным трафик-менеджером, который управляет 256 тыс. запросов одновременно и выдерживает нагрузку в полтриллиона объектов. Ускорители берут на себя обработку префиксов IPv4 и IPv6, сжатие и хеширование диапазонов IP, доставку пакетов, сбор статистики.

Внешняя память DRAM обладает 28 линиями SERDES, которые работают на скорости 12,5 Гб/с. SERDES использует проприетарный последовательный протокол для доступа к памяти — он способен проводить до миллиарда случайных обращений в секунду и поддерживает передачу данных на скорости до 300 Гб/с.

Логика связана с DRAM через параллельный интерфейс ввода/вывода — он обладает максимальной скоростью 1250 Мб/с. Интересно, что по 22-нанометровому техпроцессу выполнен только процессор. DRAM выполнена по техпроцессу 30 нм, а SERDES и BIST — по 28 нм.

«Мы определили, какие операции обычно проводят на такого рода устройствах, и оптимизировали чип для работы со случайными операциями на высокой скорости. Его можно использовать как буфер, в котором количество чтений будет равно количеству записей, а также для поиска данных по базам, когда количество обновлений не такое большое», — рассказал Джейми Маркевич (Jamie Markevitch), главный инженер Cisco.

Демонстрация «внутренностей» сетевого процессора — явление не уникальное, но редкое. Производители обычно такую информацию не разглашают, хотя исключения случаются. В январе компания Barefoot Networks рассказала об особенностях чипа Tofino, Innovium в марте — о Teralynx и Mellanox Technologies в июле — о Spectrum-2.

О конференции Hot Chips

Hot Chips — это симпозиум на тему высокопроизводительных процессоров. Впервые он состоялся еще в 1989 году. В этом году, помимо Cisco, мероприятие посетили многие крупные производители. В частности, Microsoft представили свои наработки в области дополненной реальности и рассказали о процессоре для Xbox One X Scorpio. Выступление китайской компании Baidu было посвящено дополненной реальности, а представитель Google рассказал об оптимизации железа для нейросетей.

P.S. О чем еще мы пишем в нашем блоге:

- Защита персональных данных: европейский подход

- Виртуализация приложений: как правильно настраивать виртуальные машины

- Особенности двухфакторной аутентификации: работает ли это в облаке IaaS