[Перевод] Начало войны техпроцессов: 5 нм и 3 нм

На горизонте появляются новые транзисторные структуры, новые инструменты и процессы –, а с ними и куча проблем

Несколько фабрик пытаются вывести на рынок техпроцессы на 5 нм, однако их клиентам предстоит решить — проектировать новые чипы на текущих транзисторах, или перейти на новые, созданные в техпроцессе 3 нм.

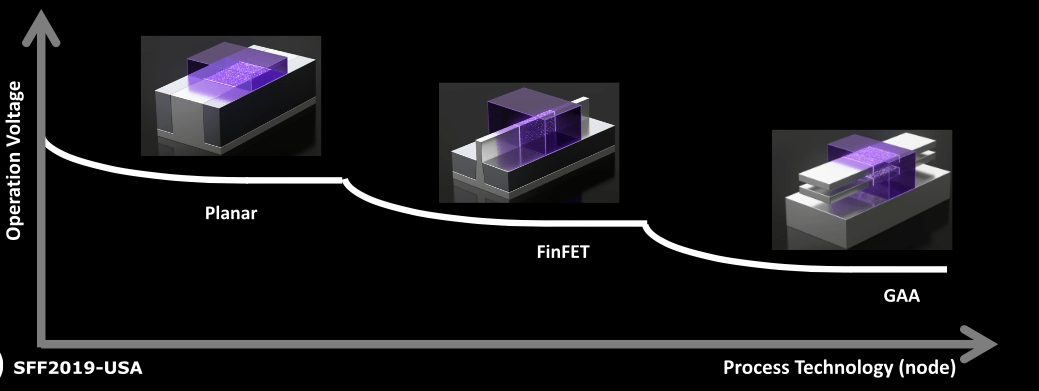

Для перехода нужно либо расширить текущие finFET на 3 нм, либо реализовать новую технологию кольцевого затвора [gate-all-around FET, GAA FET] на 3 нм или 2 нм. GAA FET — это следующий этап эволюции по сравнению с finFET, они быстрее работают, однако эти новые транзисторы сложнее и дороже в производстве, и переход на них может оказаться слишком болезненным. С другой стороны, индустрия разрабатывает новые технологии травления, структурирования и т.д., чтобы расчистить дорогу к этим новым техпроцессам.

Даты выпуска этих GAA FET разнятся от фабрики к фабрике. Samsung и TSMC делают finFET на 7 нм, и в этом году планируют переделать finFET на 5 нм, а также выпускать чипы в диапазоне полушага от 5 нм. Такие техпроцессы позволят улучшить как скорость работы, так и энергопотребление.

Что касается 3 нм, то тут Samsung через год-два планирует перепрыгнуть на нанолистовые FET — новый тип GAA-транзистора. TSMC же планирует впервые выпустить finFET на 3 нм. Следующим этапом TSMC выпустит GAA на 3 нм или 2 нм — так считают многие аналитики и поставщики оборудования.

«TSMC ускоряет разработку finFET на 3 нм, представляющих собой ужатые версии 5 нм, — Сказал Хэндел Джонс, директор IBS. — Производство первых пробных экземпляров finFET на 3 нм TSMC начнёт в 2020-м. Промышленные выпуски продукции запланированы на 3-й квартал 2021 года, что на квартал раньше запуска техпроцесса на 3 нм от Samsung. Разработка GAA в TSMC отстаёт от Samsung на 12–18 месяцев, но агрессивная стратегия по выпуску finFET на 3 нм может скомпенсировать это отставание».

TSMC продолжает оценивать свои варианты на 3 нм, и планы ещё могут поменяться. Пока компания не комментирует ситуацию, но обещает вскоре раскрыть свои планы на 3 нм. Тем не менее, переход TSMC на 3 нм finFET — логичный шаг. Переход к новым транзисторам может неблагоприятно повлиять на клиентов. Но в конечном итоге finFET исчерпает свои возможности, поэтому у TSMC нет другого выбора, кроме как переходить на GAA.

Другие компании тоже разрабатывают передовые процессы. Intel, эпизодически участвующая в коммерческом производстве, выпускает чипы на 10 нм, изучая 7 нм в лаборатории. Тем временем SMIC делает finFET на 16 нм/12 нм, исследуя при этом в лаборатории 10 нм/7 нм.

Все передовые процессы требуют значительных финансов, и не все чипы требуют использования 3 нм или других передовых технологий. Рост цен заставляет компании исследовать другие варианты развития. Ещё один способ получить преимущества масштабирования — новые виды корпусов передовых чипов. Несколько компаний разрабатывают такие корпуса.

Рабочее напряжение различных технологий

Пришёл ли конец масштабированию?

Чипы состоят из транзисторов, контактов и их соединений. Транзисторы играют роль переключателей. Передовые чипы могут содержать до 35 млрд транзисторов.

Соединения, находящиеся на верхней части транзистора, состоят из крохотных медных проводков, проводящих электрические сигналы между транзисторами. Транзисторы и проводки соединяются промежуточным слоем middle-of-line (MOL). MOL состоит из крохотных контактов.

Масштабирование интегральных схем (ИС), их традиционный способ развития, заключается в уменьшении размеров ИС с каждым новым техпроцессом и с упаковкой их на монолитном кристалле.

Для этого производители чипов каждые 18–24 месяца представляют новый технологический процесс, обеспечивающий всё большую плотность упаковки транзисторов. Каждому процессу даётся числовое название. Изначально эти названия были связаны с длиной вентиля транзистора.

Для каждого следующего процесса производители масштабируют спецификации транзисторов в 0,7 раз, что позволяет индустрии увеличивать быстродействие на 40% при том же энергопотреблении и уменьшать размер на 50%. Масштабирование чипов позволяет выпускать новые, более функциональные электронные продукты.

Формула работала, и производители чипов постепенно меняли техпроцессы. Но на рубеже 20 нм произошло изменение — традиционные плоские транзисторы выбрали весь свой ресурс. С 2011 года производители перешли на finFET, что позволило масштабировать устройства далее.

Однако finFET дороже в производстве. В результате стоимость исследований и разработок взлетела до небес. Поэтому периоды перехода от одного техпроцесса к другому увеличились с 18 до 30 и более месяцев.

Компания Intel следовала общей тенденции масштабирования в 0,7 раз. Однако начиная с 16 нм/14 нм другие производители отошли этот этой формулы, что внесло некоторую неразбериху.

В этот момент нумерация техпроцессов начала размываться и потеряла связь со спецификациями транзисторов. Сегодня эти названия– всего лишь маркетинговые термины. «Обозначение техпроцессов становится всё менее осмысленным и понятным, — сказал Сэмюэл Вон, аналитик в Gartner. — К примеру, на 5 нм или 3 нм нет ни одного геометрического размера, равного 5 или 3 нм. Кроме того, у разных производителей процессы становятся всё более разными. Для одного и того же техпроцесса эффективность чипов отличается у TSMC, Samsung и, конечно же, Intel.

Масштабирование замедляется и у передовых техпроцессов. Для процесса на 7 нм шаг затвора транзистора [contacted poly pitch, CPP] равняется 56–57 нм с металлическим шагом в 40 нм, согласно информации компаний IC Knowledge и TEL. Для 5 нм CPP примерно равен 45–50 нм с металлическим шагом 26 нм. CPP, ключевая метрика транзисторов, обозначает расстояние между контактами истока и стока.

Кроме того, соотношение стоимости и быстродействия выглядит уже совсем не так, из-за чего многие считают, что закон Мура уже изжил себя.

«Закон Мура на самом деле лишь наблюдение, ставшее самоисполняющимся пророчеством, поддерживающим движение полупроводниковой промышленности вперёд. Экономический аспект закона Мура начал ухудшаться с ростом стоимости многократного структурирования [multiple patterning] и экстремальной ультрафиолетовой литографии (EUV), — сказал Даглас Гуереро, главный технолог из Brewer Science. — Новые архитектуры и дизайны обеспечат прирост вычислительной мощности, но это будет уже не масштабирование. Это означает, что в будущем чипы увеличат вычислительную мощность, но их стоимость не обязательно будет уменьшаться с той же скоростью, что и ранее».

Масштабирование не то, чтобы совсем прекращается. ИИ, сервера и смартфоны требуют всё более быстрых чипов и продвинутых техпроцессов. «Лет десять назад некоторые люди спрашивали: Да кому нужно ещё больше транзисторов? Некоторые считали, что в мире уже не осталось идей по поводу того, что делать с более быстрыми компьютерами, кроме совсем экзотических применений, — сказал Аки Фуджимура, директор D2S. — Сегодня для интернета вещей меньшая стоимость, достаточно хорошее быстродействие и возможности по интеграции выигрывают у простого увеличения плотности. Однако для изготовления более быстрых и экономных чипов, у которых стоимость транзисторов будет падать, требуются более быстрые транзисторы».

Очевидно, не для всего нужны передовые техпроцессы. На чипы, производимые по хорошо отлаженным техпроцессам, Есть высокий спрос. «Сюда входят ИС для работы с радиоволнами и OLED-дисплеями в смартфонах, а также ИС для управления питанием, которые используются в компьютерах и твердотельных накопителях», — сказал Джейсон Вон, один из президентов UMC.

Масштабирование finFET

В вопросе масштабирования чипов производители годами шли по одной и той же схеме, с идентичными типами транзисторов. В 2011 году Intel перешла на finFET на 22 нм, а затем на 16 нм/14 нм.

В finFET управление током осуществляется размещением вентилей на всех трёх сторонах плавника. У finFET бывает от 2 до 4 плавников. У каждого — своя определённая ширина, высота и форма.

У finFET первого поколения от Intel на 22 нм шаг плавника составлял 60 нм, а высота — 34 нм. Затем, на 14 нм шаг и высота были одинаковыми, 42 нм.

Intel сделала плавники выше и тоньше, чтобы масштабировать finFET. «Масштабирование finFET уменьшает поперечные размеры устройства, увеличивая плотность по площади, а увеличение высоты плавника улучшает быстродействие», — написала у себя в блоге Нерисса Дрэгер, директор по связи с университетами в компании Lam Research.

На техпроцессах 10 нм/7 нм изготовители чипов пошли по тому же пути масштабирования finFET. В 2018 году TSMC начала производство первых finFET на 7 нм, за ней последовала Samsung. Intel в прошлом году после нескольких задержек начала производство на 10 нм.

В 2020 году конкуренция фабрик увеличится. Samsung и TSMC подготавливают 5 нм и различные полуцелые техпроцессы. Ведутся исследования касательно 3 нм.

Все процессы стоят дорого. Стоимость проектирования чипа на 3 нм составляет $650 млн — сравните это с $436,3 млн для устройства на 5 нм и $222,3 млн для устройства на 7 нм. Это стоимость такой разработки, после которой через год технология уже уходит в производство.

По сравнению с 7 нм, finFET на 5 нм от Samsung дадут 25% увеличение логической площади, и 20% уменьшение потребления энергии или 10% увеличение скорости.

Для сравнения, finFET на 5 мм от TSMC предлагает «скорость на 15% больше при том же энергопотреблении или уменьшение энергопотребления на 30% при той же скорости, с увеличением логической плотности в 1,84 раза», — сказал Джоффри Йеп, главный директор по передовым технологиям в TSMC.

В техпроцессах на 7 нм и 5 нм производители чипов провели серьёзные изменения. Для изготовления критически важных функций в чипах, две компании перешли от традиционной литографии на 193 нм к экстремальной ультрафиолетовой литографии (EUV). EUV использует длины волн в 13,5 нм, что упрощает процесс.

Но EUV не решает всех проблем масштабирования чипов. «Решение этих задач требует множества технологий, не ограничивающихся масштабированием, включая использование новых материалов, новых типов встроенной энергонезависимой памяти и архитектур передовой логики, новых подходов к травлению, инноваций в производстве корпусов и дизайна чиплетов», — сказала Реджина Фрид, управляющий технологический директор в Applied Materials.

Тем временем, за кулисами Samsung и TSMC подготавливают свои варианты техпроцессов на 3 нм. В прошлом производители чипов шли по одному пути, но сегодня их пути расходятся.

»3 нм бывает в различных вариантах, таких, как finFET и GAA, — сказал Вон. — Это даёт возможность клиентам выбирать различные сочетания стоимости, плотности, энергопотребления и скорости, так, чтобы удовлетворить свои запросы».

Samsung обещает представить нанолистовую FET на 3 нм. TSMC тоже работает над ними, но планирует продлить использование finFET на следующее поколение. «У TSMC будет finFET на 3 нм в третьем квартале 2021 года, — сказал Джонс. — GAA от TSMC появятся в 2022–2023 годах».

Вот тут клиенты фабрик должны взвесить все за и против, касающиеся стоимости и технических компромиссов. Расширение finFET — безопасный путь. «Многие клиенты считают TSMC наименее рискованным производителем», — сказал Джонс.

Тем не менее, GAA обеспечивает некоторое увеличение быстродействия. «У GAA на 3 нм меньше пороговое напряжение, и потенциально на 15–20% меньше энергопотребление, по сравнению с finFET на 3 нм, — сказал Джонс. — Однако разница в быстродействии будет на уровне 8%, поскольку MOL и BEOL одинаковые».

Backend-of-the-line (BEOL) и MOL — узкие места в передовых чипах. Проблема MOL заключается в сопротивлении контактов.

BEOL — это этап производства, на котором происходит подсоединение проводков. Из-за их постепенного уменьшения возникают задержки, связанные с ёмкостным сопротивлением. В finFET и GAA используются разные транзисторы, но схемы их соединения в техпроцессе 3 нм, скорее всего, будут почти одинаковыми. Задержки, связанные с ёмкостным сопротивлением, будут вредить обоим типам транзисторов.

Есть и другие проблем. finFET исчерпают свои возможности, когда ширина плавника достигнет 5 нм. finFET на техпроцессах 5 нм/3 нм уже упираются в этот предел.

Кроме того, finFET на 3 нм могут состоять из одного плавника, по сравнению с двумя или большим числом плавников в других техпроцессах. «Чтобы продлить работу finFET на 3 нм, нам понадобятся особые технологии, увеличивающие мощность единственного плавника и уменьшающие паразитные явления», — сказал Наото Хоригучи, директор по КМОП в Imec.

Один из способов продлить работу finFET на 3 нм — перейти на германий для p-канала. finFET на 3 нм с каналами высокой пропускной способности помогут увеличить скорость работы чипов, однако столкнутся с определёнными проблемами с интеграцией.

Переход на нанолисты

В конечном счёте finFET перестанут масштабироваться, и производителям чипов придётся перейти на новые транзисторы, а именно на нанолистовые FET.

Нанолистовые FET начали набирать обороты в 2017-м, когда Samsung представила Multi Bridge Channel FET (MBCFET) на 3 нм. MBCFET — это нанолистовые FET. Пробные образцы начнут производить уже в этом году, а промышленный выпуск начнётся в 2022-м.

TSMC тоже работает с нанолистовыми FET, представляющими собой один из типов GAA-транзисторов. Нанолистовые FET обеспечивают небольшое преимущество для масштабирования finFET на 5 нм, но у них есть несколько преимуществ.

Нанолистовой FET — это, по сути, finFET, положенный набок, и обёрнутый затворами. Нанолист состоит из нескольких отдельных тонких горизонтальных листов, положенных друг на друга. Каждый лист — это отдельный канал.

Вокруг каждого листа находится затвор, и в результате получается кольцевой транзистор. Теоретически, нанолистовые FET дают большее быстродействие при меньших утечках, поскольку управление током осуществляется с четырёх сторон структуры.

Изначально в нанолистовых FET будет примерно по четыре листа. «Ширина типичного нанолиста составляет от 12 до 16 нм, а толщина — 5 нм», — сказал Хоригучи.

Этим нанолист отличается от finFET. Количество плавников у finFET ограничено, что стесняет работу дизайнеров. «Преимущество нанолиста в том, что у него можно менять ширину. Ширину можно подбирать по запросам дизайнера. Это даёт им некоторую свободу. Они могут обнаружить лучший вариант по соотношению энергопотребления и скорости», — сказал Хоригучи.

К примеру, у транзистора с более широким листом будет больше и ток возбуждения. Узкий лист позволяет сделать устройство меньше размером с меньшим током возбуждения.

Нанолисты связаны с технологией нанопроводов, в которой каналами служат провода. Ограничение ширины канала приводит к ограничению тока возбуждения.

Поэтому нанолистовые FET и набирают обороты. Однако у этой технологии и у finFET на 3 нм есть несколько проблем. «Проблемы finFET связаны с квантовым управлением ширины плавника и профиля плавника. Проблемы нанолистов связаны с дисбалансом p/n, эффективностью нижнего листа, прослоек между листами, управлением длиной вентиля», — сказал Джин Кай, заместитель директора TSMC, во время презентации на IEDM.

Учитывая все эти сложности, на ввод технологии нанолистовых FET уйдёт какое-то время. «У перехода на новые архитектуры транзисторов есть много препятствий, — сказал Герреро. — Определённо для этого потребуются новые материалы».

В простейшем варианте процесса изготовление нанолистового FET начинается с формирования сверхрешётки на подложке. Эпитаксиальный инструмент располагает на подложке перемежающиеся слои кремний-германиевого сплава (SiGe) и кремния. Стопка будет состоять как минимум из трёх слоёв SiGe и трёх слоёв кремния.

Затем в сверхрешётке при помощи структурирования и травления формируются вертикальные плавники, для чего требуется очень точное управление процессом.

Потом начинается один из самых сложных этапов — формирование внутренних прокладок. Во-первых, внешние части слоёв SiGe утапливаются в сверхрешётке заподлицо. Это создаёт небольшие углубления, заполняемые диэлектриком. «Внутренние прокладки нужны для уменьшения ёмкости вентиля, — сказал Кай. — Их изготовление — важнейшая часть процесса».

И такие технологии уже есть — IBM и TEL недавно описали новую технику травления, подходящую как для внутренних прокладок, так и для выпуска каналов. Для этого используется изотропное сухое травление SiGe с соотношением 150:1.

Такая технология позволяет получать очень точные внутренние прокладки. «Изготовление выемок в SiGe требует очень выборочного бокового «слепого» травления слоёв», — сказал Николас Лубе, менеджер по R&D в IBM.

Затем формируются истока и сток. После этого слои SiGe удаляются из сверхрешётки при помощи травления. Остаются кремниевые слои, или листы, составляющие каналы.

В структуру помещаются High-k-материалы, и наконец, формируются соединения MOL, что и даёт нанолист.

Это упрощённое описание этого сложного процесса. Тем не менее, как и любые новые технологии, нанолисты могут быть подвержены появлению дефектов. Требуется дополнительное изучение и измерение всех шагов.

«Как и с предыдущими переходами между технологиями, мы видим проблемы, связанные с изучением и измерением нанолистов», — сказал Чет Ленокс, директор по решениям управлением процессами в KLA. «Может появиться много дефектных режимов как во внутренних прокладках, так и в нанолистах. Производителям ИС необходимы точные размеры отдельных нанолистов, а не просто средняя величина каждой стопки, чтобы уменьшить изменчивость своих производственных процессов».

Для этого тоже требуются новые технологии. К примеру, Imec и Applied Materials недавно представили работу по технологии «scalpel scanning spreading resistance microscopy» (s-SSRM) для создания кольцевых затворов. В технологии s-SSRM крохотный скальпель откалывает небольшую часть структуры, и в этот разрез можно добавлять легирующие примеси.

Другие варианты

В рамках R&D Imec разрабатывает более передовые виды GAA, такие, как CFET и вилочно-листовые FET (forksheet FET), нацеленные на 2 нм и меньше.

К тому времени для большинства производителей масштабирование ИС станет слишком дорогом, в особенности в свете уменьшения преимуществ по энергопотреблению и быстродействию. Поэтому всё большую популярность набирают передовые компоновки чипов. Вместо того, чтобы запихивать все функции на один кристалл, предполагается разбивать устройства на более мелкие кристаллы и интегрировать их в передовые корпуса.

«Это всё зависит от области применения, — сказал Рич Райс, старший вице-президент по бизнес-развитию ASE. — Мы определённо наблюдаем увеличение подобных попыток, даже в техпроцессах, ушедших глубоко в субмикронные размеры. Это развитие будет продолжаться и далее. Многие компании занимаются этим. Они решают, могут ли они интегрировать чипы на 5 нм, и хотят ли. Они активно ищут способы разбивания систем».

Это не так-то легко сделать. Плюс существует несколько вариантов корпусов с различными компромиссами — 2.5D, 3D-ICs, чиплеты и fan-out.

Заключение

Определённо не всем потребуются такие передовые техпроцессы. Однако Apple, HiSilicon, Intel, Samsung и Qualcomm не зря рассчитывают на передовые технологии.

Потребителям нужны самые новые и лучшие системы с увеличенным быстродействием. Вопрос лишь в том, дадут ли новые технологии какие-либо реальные преимущества по приемлемой цене.