Мгновенное заполнение последовательности выбранных ячеек физической памяти

(продолжение работы над своим процессором, и в заголовке про физическую память так как везде поисковиком находится про ячейки Excell).

Сначала думал — да ну какая мелочь для процессора, но потом подумал — многие пишут о мелочах и даже получают плюсы, почему не написать о мелочи, если чип создаётся новый.

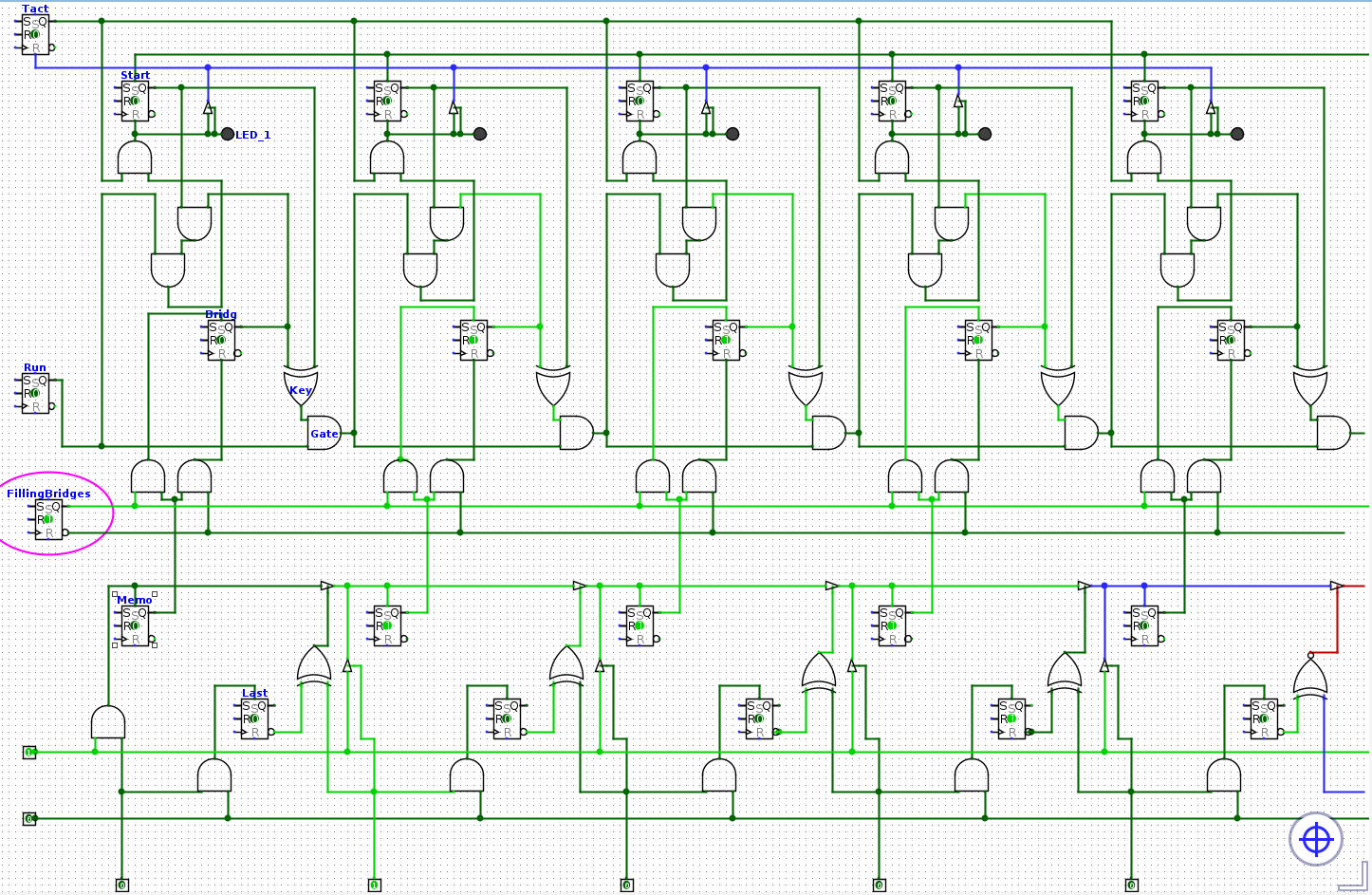

Сразу говорю, что роль памяти в данной схеме играют SR триггеры предполагаемого FPGA и процедура заполнения любого числа цепи ячеек (или даже одной) выполняется за два рабочих такта проектируемого процессора, независимо от числа выбранных ячеек. Над этой задачкой пришлось немного пломать голову, и нужно было понять что такое управляемый буфер (в данном случае это для Logisim Evolution).

После того, как составил рабочую схему кэша мостов, для работы процессора в режиме без счётчика команд, приступил к схеме управления кэшом мостов. Кэш мостов — это кэш обеспечивающий выполнение команд без счётчика команд, и позволяющий выполнять только команды в обозначенных ячейках памяти. По сути управление кэшем мостов сводится к мгновенному заполнению групп выбранных ячеек. И вот для того чтобы обеспечить бесперебойную работу управляемых буферов в сложной цепи (множество ячеек и множество источников сигнала) пришлось пойти на Хитрость с ИСКЛЮЧАЮЩИМ ИЛИ.

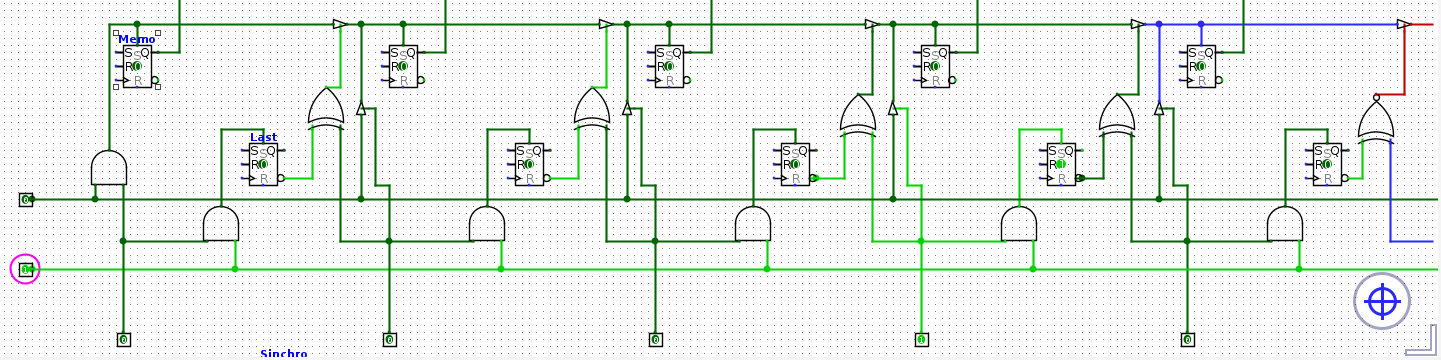

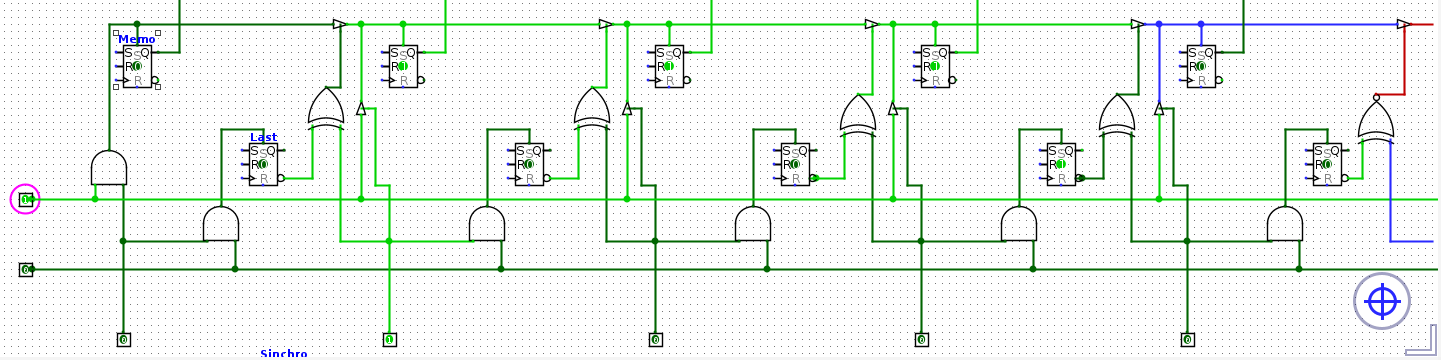

Триггеры группы Last — нижний ряд триггеров на данном изображении, служит для обозначения последнего триггера данной группы для конкретной ячейки, в который запишется единица и заблокирует прохождение сигнала по верхнему проводнику, через который подряд записывается единица в сами эти ячейки памяти механизма управления кэшем мостов — в триггеры группы Memo (незаконченное слово, так как по сути всё это является устройством для управления памятью, а не ей самой).

Подаётся сигнал единицы на два контакта для обозначения последней ячейки цепи (на изображении предпоследний нижний контакт и контакт нижнего горизонтального на схеме провода)

Затем подаётся сигнал для заполнения триггеров памяти механизма управления кэшем мостов — триггеров группы Memo (сам кэш мостов описан в предыдущей публикации и здесь приведу его позднее), и сигнал единицы проходит направо по схеме беспрепятственно, заполняя все триггеры Memo, вплоть до ячейки с заполненным триггером Last . Два ранее задействованных контакта перезодят в режим бездействия (сигнал нуля или плавающее состояние).

И вот в чём тут фокус: дело в том что, чтобы подать сигнал для начала заполнения цепи, управляемый верхний буфер предыдущей ячейки должен подавать на выход плавающий сигнал, не противоречящий любому (сигналу нуля или единицы) поступающему на соединение сразу после него, а разрешать прохождение сигнала должен сигнал единицы по условию функционирования управляемого буфера, но сигнал единицы на контакте управления не разрешит выходящий плавающий сигнал если на вход управляемого буфера подаётся ноль. Что делать? Для этого было решено включить в эту схему элемент ИСКЛЮЧАЮЩЕГО ИЛИ, и при подаче на нижний контакт от него справа он подавал-бы на верхний буфер сигнал нуля, разрешающий на выходе буфера плавающее состояние, и тогда сигнал с правого нижнего соседнего контакта соседнй ячейки пойдёт беспрепятственно, записывая далее по ячейкам единицу во все триггеры группы Memo, пока не дойдет до ячйки с единицею в триггере группы Last .

Далее я прикрепляю скриншот устройства кэша мостов из пяти ячеек, где в триггеры группы Bridges записаны соответственно единицы (единица или наль в данном случае выбираются в триггере FillingBridges). Данная схема асинхронна, так как предположительно она будет очень быстрого действия (любое число ячеек будет проходить сигнал беспрепятственно, со скоростью близкой к скорости распространения сигнала по одному проводу, именно к такой работе подбивалась вся схема).

Понятно, что читатель ждёт более визуабельного чего-то, и более подробного — так как сам люблю узнавать новое из чтения интересного, но это пока можно ожидать в будущем. Пока только так — схемы.

В общем-то остаётся «хирургия» над микросхемами памяти в качестве «донаров» для кэша команд и «импланирование» в их изъятые части кэш мостов и механизм управления им, но это уже скорее будет с языками программирования, чисто схемами там не отделаться.